- 1SQL Server 常用函数_sql server 常见函数

- 2PyTorch、TensorFlow 和 NumPy三者之间的区别与联系是什么?_tensorflow和pytorch numpy

- 3基于51单片机的儿童安全座椅设计

- 4vue实现Element-ui省市区三级联动+市辖区修改_element-china-area-data json

- 5如何用人工智能高效选研究题目?

- 6Mybatis3.3.x技术内幕(十五):Mybatis之foreach批量insert,返回主键id列表(修复Mybatis返回null的bug)...

- 7(PYTHON)selenium+post请求批量获取小红书图片并备注_selenium 小红书

- 8html5电路模拟器,eda仿真软件

- 9助力工业产品质检,基于YOLOv5全系列参数模型【n/s/m/l/x】开发构建智能PCB电路板质检分析系统_yolo工业质检

- 10前后端分离CRUD_前后端分离列表遍历

静态时序分析——多周期、半周期和伪路径_半周期check

赞

踩

一、多周期 multicycle paths

在一些情况下,如下图所示,两个寄存器之间的组合电路传输的逻辑延时超过一个时钟周期。在这样的情况下,这个组合路径被定义为多周期路径(multicycle path)。尽管后一个寄存器会在每一个的时钟的上升沿尝试捕获(capture)数据,但我们会在STA中指定个时钟周期后的上升沿(relevant capture edge)去捕获数据。

以上图为例,组合路径的延时为三个周期,那么三个时钟周期的多周期setup check可以用以下语句进行约束

- cerate_clock -name CLKM -period 10 [get_ports CLKM] // 设置时钟源

- set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D] //multicycle

这样,我们就达成了下面的图的效果,在第三个时钟沿进行建立时间的检查。

由于工具一般会在建立时间检查时钟沿(capture edge)的前一个时钟沿进行保持时间检查,而在多周期的情况下,这样进行保持时间检查较为严苛,以上图为例,在2nd时钟沿进行保持时间检查,那么,数据需要保持到2nd时钟之后才能变化。所以,在多时钟周期的情况下,我们如果在N个周期后进行简历时间检查,那么我们会将简历时间检查提前N-1个时钟周期。

同样以上面的的电路为例,多周期hold check可以用以下语句进行约束:

- cerate_clock -name CLKM -period 10 [get_ports CLKM] // 设置时钟源

- set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D] //multicycle

二、半周期 half-cycle paths

如果一个电路设计中同时存在正时钟沿触发和负时钟沿触发的触发器,那么在这种电路中需要进行半周期的检查。

我们以下面的电路为例:

对其进行建立时间检查,那么其检查的时钟沿如下图:

其时序报告如下:

与一般的时序报告不同的是,需要注意startpoint和endpoint,其注明的触发沿是不同的。

由于时序路径中仅有半个时钟周期用来进行建立时间检查,那么我们有额外的半个时钟周期来进行保持时间检查,如下图:

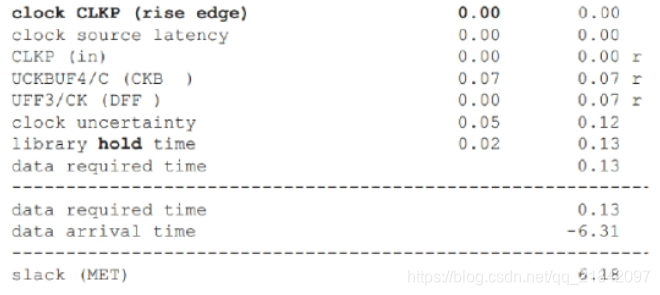

其保持时间检查时序报告如下:

三、伪路径 false paths

某些情况下,一些时序路径可能在电路设计的真实功能中并不存在,我们会在STA中将将这些路径设置为伪路径,这样,工具(prime time)会忽略这些路径,不对其进行时序分析。

一般需要进行伪路径的处理情况有:

1. 从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑。

2. 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域的路径。

设置伪路径可以减少工具的分析工作,让工具更专注于分析真实的时序路径,而且能减少分析时间。但是,设置过多的伪路径会降低分析的效率,反而使分析速度减慢。

我们有以下几种方法来设置伪路径约束:

- set_flase_path -from [get_clocks SCAN_CLK] -to [get_clocks CORE_CLK]

- //任何从SCAN_CLK时钟域到CORE_CLK时钟域的时序路径都是伪路径

-

- set_false_path -through [get_pins UMUX0/S]

- //所有通过这个pin的时序路径都是伪路径

建议减少使用-through,因为through命令会增加分析复杂度。