- 1基于Python数据挖掘的文本数据的分类与分析_数据挖掘文本分类

- 2Mac系统安装vue-cli_mac 全局安装vue-cli

- 3Android 修改home下的文件夹名称为英文_手机文件怎么改英文路径格式

- 4Qwen2 阿里最强开源大模型(Qwen2-7B)本地部署、API调用和WebUI对话机器人_qwen2本地部署

- 5大模型LLM训练的数据集_llm 数据集

- 6@[TOC](python数据结构与算法练习-动态规划问题)_python 给你一个只包含正整数的非空数组

- 7【软考数据库案例分析】(全)_软考中级数据库管理工程师 案例题

- 8java学习笔记——List集合(ArrayList、LinkedList)

- 9【gitlib】linux系统rpm安装gitlib最新版本及修改clone地址_linux升级gitlab

- 10AI大模型基础环境搭建_大模型环境搭建

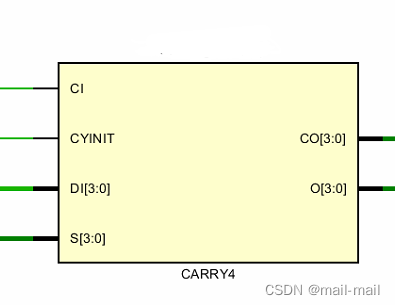

carry4 的构成

赞

踩

一、carry4的示例*

其中,

CI是上一个CARRY4的进位输出,位宽为1;

CYINT是进位的初始化值,位宽为1;

DI是数据的输入(两个加数的任意一个),位宽为4;

SI是两个加数的异或,位宽为4;

O是加法结果输出,位宽为4;

CO是进位输出,位宽为4;(为什么进位输出是4bit?后面有解释)

S[3:0]:为二选一逻辑MUXCY的选择信号,0选左边,1选进位结果,S的值为A^B。

DI[3:0]:即原理图O5或者AX(对应下图dev 的 DI或者AX)二选一,值为A或B,结果都一样。

CYINIT:加时为0,减时为1。即当做减法时,减数需要取反加1将减法操作转为加法操作。CYINIT=1时相当于加1操作。可用AX动态赋值。

CIN:用于级联slices生产一个更大的进位链 。

O[3:0]:即AMUX/AQ–HMUX/HQ 为实际计算结果

CO[3:0]:即AQ-HQ 为每一位的进位结果

COUT:等于CO[3],用于与其他CARRY4的CIN级联生成更大的进位链

二、Carry4的内部结构如下图所示

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-XlJPcCwM-1664418972493)(https://imgblog.csdnimg.cn/ca7a2cb6a6b44fdab7eb42ec787dce78.png)]](https://img-blog.csdnimg.cn/d2e3b33a03c14fc0b8453aa2ac8e8127.png)

图中类似于 O5与 AX的 等腰梯形 为或逻辑,

红框框住的部分为它的1个基本单元(本质上是1个全加器)。

CIN=进位输入(当它在最低位时,置0做加法,置1做减法)

S0=A0⊕B0 (这里和全加器中的S有些区别),它来自LUTA的O6

O0=S0 ⊕CIN=A0⊕B0 ⊕CIN(这里的O才是全加器的S),它来自LUTA的O5或外面外部输入AX

DI0 = A0 或者 B0 (这里指的是两个加数中的一个,它的作用要配合S0)

AX 是预置数,这里我们不过多关注

我们知道产生进位的条件在A B以及 CIN中有两个或两个以上的1。

当S0=0时,有两种情况,即两个加数都为0和两个加数都为1。此时,MUXCY选择DI0作为数据输入,CO0的结果由DI0决定。因为S0=0时,DI0为0等价于A0,B0,COUT0都为0。DI0为1等价于A0,B0,COUT0都为1。

当S0=1时,即A0与B0中有1个为1。此时,MUXCY选择CIN0作为数据输入,CO0的结果由CIN0决定。因为S0=1时,A0与B0中只有1个1,还缺1个1才能进位,进位所需的那个1就看CIN1肯不肯施舍了。

S0为0,选muxcy的左边,S0=1,选muxcy的右边

三、加法举例

这里我们要先解释一下FPGA中利用Carry Chain实现加法的原理,比如两个加数分别为 a = 4’b1000和 b=4’b1100,其结果应该是 8+12=20。

a = 4'b1000; b = 4'b1100; S = a ^ b = 4'b0100; D = b = 4'b1100; //D取a也可以 CIN = 0; //没有上一级的进位输入 CYINIT = 0; //初始值为0 // 下面为CARRY4的计算过程,具体的算法跟上图中过程一样 S0 = 0; //S的第0位 O0 = S0 ^ 0 = 0 ^ 0 = 0; CO0 = DI0 = 0; //上图中的MUXCY,S0为0时,选择1,也就是DI0,S0为1是选择2 S1 = 0; O1 = S1 ^ CO0 = 0 ^ 0 = 0; CO1 = DI1 = 0; S2 = 1; O2 = S2 ^ CO1 = 0 ^ 1 = 1; CO2 = CO1 = 0; S3 = 0; O3 = S3 ^ CO2 = 0 ^ 0 = 0; CO3 = DI3 = 1;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

加法最终的输出结果为:

a = 4’b1000;

b = 4’b1100;

{O3,O2,O1,O0}=4’b0100

{CO3,CO2,CO1,CO0}=4’b1000

最终结果:{CO3,O3,O2,O1,O0} = 5’b10100 = 20

可以看出 {O3,O2,O1,O0} 是 a+b 的半加器结果,而 {CO3,CO2,CO1,CO0} 是 a+b 的进位结果;

输出给下一级的 COUT 只是CO[3]。