热门标签

热门文章

- 1【ROS2】中级:tf2- 介绍

- 2大三暑假该选择实习还是准备秋招?_大三暑假实习对秋招作用大吗

- 3sql下员工工牌(YC0001)的简单实现_工牌绑定数据库实现

- 4【动态规划算法】不同路径_不同路径升级版

- 5springboot 第三方游戏账号交易平台-计算机毕设 附源码80552_游戏账号租赁系统功能结构图

- 6常用Git指令(提交GitHub项目)_github提交代码命令

- 7数据结构- 红黑树插入和调整_更改红黑树插入顺序,树是否相同

- 8【VMware】 vCenter Converter standalone 6.6.0正式版下载_vmware vcenter converter standalone下载

- 9minio+springboot+vue实现切片上传_springboot vue 文件分片上传

- 10java接入微信支付_微信支付pom依赖

当前位置: article > 正文

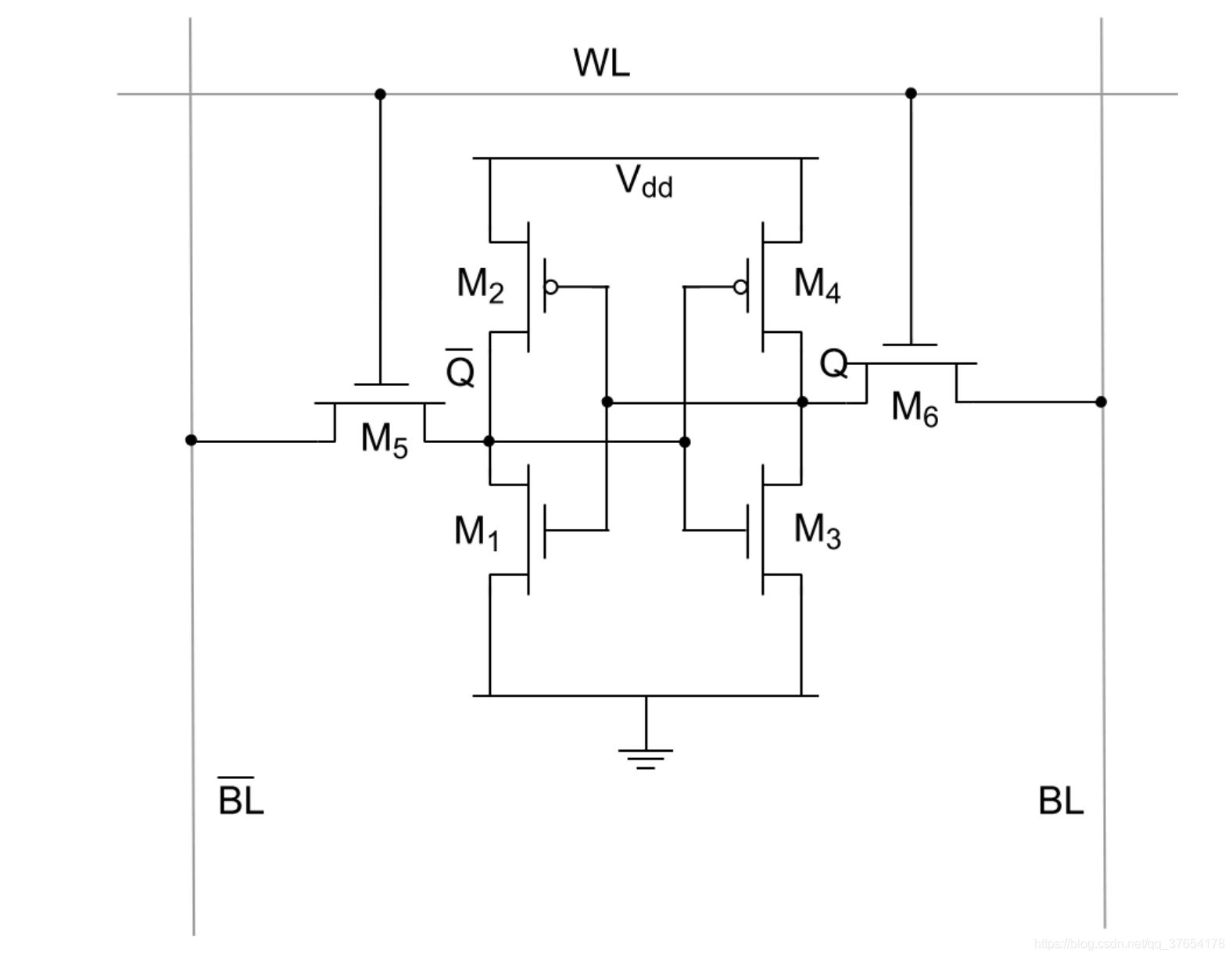

6T SRAM 读写工作原理

作者:我家自动化 | 2024-07-15 11:43:43

赞

踩

6t sram

图中M1,M3,M5和M6为NMOS管,高电平导通;M2和M4为PMOS管,低电平导通。BL(Bit Line)为位线,用于读写数据。WL(Word Line)为字线,用于控制读写操作。SRAM中每一bit的数据存储在由M1,M2,M3和M4组成两个交叉连接的反相器中(即图中的Q端和/Q端)。M5和M6两个NMOS管是控制开关,用于控制数据从存储单元到位线之间的传递。【源自6T SRAM的基本结构及其读写操作_KSY至上主义者的博客-CSDN博客】

1、读操作(BL与BLB=1)

(init Q=1,QB=0)

(1)预充电BL与BLB为1;WL拉高

(2)M6开启,BL=Q;M5开启,BLB=QB

(3)初始Q=1,M1为导通;初始QB=0,M4为导通;

(4)BL=Q=1,BLB—>QB=0(因Q不变,所以QB不会变,BLB反而被变化)

(5)BL与BLB产生电压差,SA进行放大(BL电压不变,BLB电压下降,读出为1;反之读出为0)

2、写操作(写1时BL=1、BLB=0)

(init Q=1,QB=0)

(1)预充电BL=1、BLB=0(写1);WL拉高

(2)M6开启,Q=BL=1;M5开启,QB=BLB=0——无变化

(1)预充电BL=0、BLB=1(写0);WL拉高

(2)M6开启,Q—>BL=0;M5开启,QB—>BLB=1

(3)Q与QB同时反向改变,锁存器存储数值变化

(4)Q=0,QB=1写入成功

3、保持操作

(1)WL拉低,此时Q与QB互锁不变

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家自动化/article/detail/829176

推荐阅读

相关标签