- 1如何去解决fatal: refusing to merge unrelated histories_refuing to unrelated histories

- 2浅谈学习网络安全技术必备的一些网络基础知识

- 3Visual studio行号开启及使用技巧_vs设置行号

- 4fastapi教程(一):初识 fastapi_fastapi教学

- 5ThreadPoolExecutor源码解读(三)——如何优雅的关闭线程池(shutdown、shutdownNow、awaitTermination)_threadpoolexecutor.awaittermination

- 6C语言笔记31 •单链表经典算法OJ题-3.反转链表•

- 7华为3面,官网显示面试通过了...开始泡池子,进入漫长等待期_华为泡池

- 8GPT4原理与代码实例讲解_gpt4怎么构造损失函数

- 9AI在测试中的应用_ai在测试领域的应用

- 10jar包冲突解决(getTextContent()方法无法找到)

静态随机存储器(SRAM)

赞

踩

目录

介绍

静态随机存储器(SRAM)是一种广泛用于计算机系统和嵌入式设备中的高速随机访问存储器。与动态随机存储器(DRAM)不同,SRAM 不需要定期刷新,因此可以实现更快的访问时间和更低的功耗。 SRAM通常用于缓存、高速缓冲器和存储器应用程序中,其中性能和可靠性至关重要。

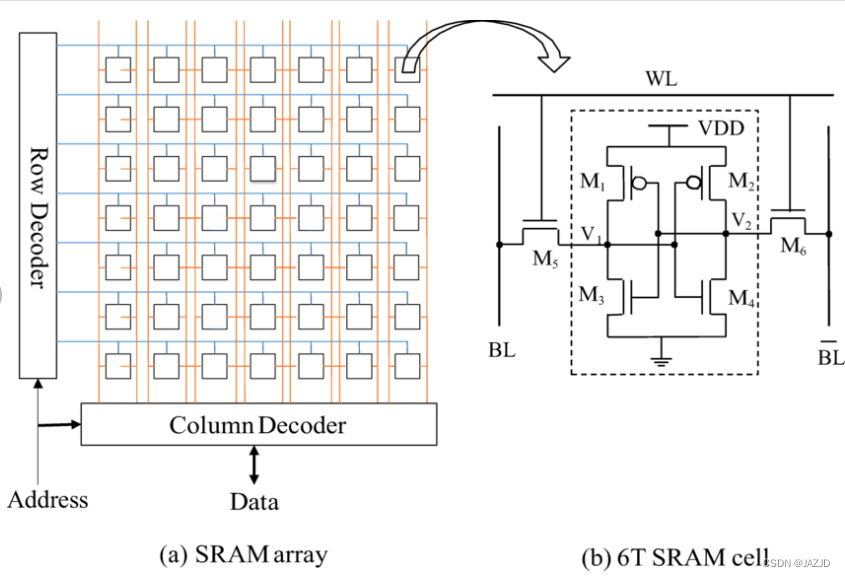

基本的 SRAM 存储单元阵列

静态随机存储器(SRAM)是计算机系统和嵌入式设备中常用的快速随机存取存储器。它由基本 SRAM 存储单元组成,这些单元被组织成矩阵或阵列。

1. SRAM 存储单元

每个 SRAM 存储单元由六个晶体管组成,通常被配置为跨耦合反相器。这种设计允许存储单元存储一个二进制位,0 或 1。

在 SRAM 存储单元中,两个晶体管 M1 和 M2 形成一个反相器,用于存储数据。M3 和 M4 形成另一个反相器,用于保持存储状态。M5 和 M6 用于控制对存储单元的访问。

当 M5 导通且 M6 截止时,数据可以通过 M1 和 M2 传输到存储单元。当 M6 导通且 M5 截止时,存储单元的状态被保持。

2. SRAM 阵列

SRAM 阵列由行和列组成,每个存储单元由一个唯一地址指定。行和列由解码器地址,允许对特定存储单元进行访问。SRAM 阵列通常具有多个字节或字的宽度,允许并行存储和检索多个位。

例如,一个 8x8 SRAM 阵列由 64 个存储单元组成,每个存储单元存储一个比特。该阵列有 8 行和 8 列,每个存储单元由一个 3 位地址(行地址和列地址)指定。

3. SRAM 阵列的读写操作

SRAM 阵列的读写操作由控制逻辑控制。

读取操作:

- 地址信号被送到译码器,选择要读取的存储单元。

- 存储单元的状态通过读取放大器被放大并输出到数据线上。

写入操作:

- 地址信号被送到译码器,选择要写入的存储单元。

- 数据信号被加载到存储单元上。

- 写放大器将数据写入到存储单元中。

4. SRAM 阵列的扩展

SRAM 阵列的内存容量可以通过增加存储单元的数量或增加存储单元阵列的层数来扩展。

- 增加存储单元数量: 这可以通过缩小存储单元的尺寸或使用更先进的制造工艺来实现。

- 增加存储单元阵列的层数: 这可以通过将多个存储单元阵列堆叠在一起来实现。

5. SRAM 阵列的应用

SRAM 阵列广泛应用于计算机系统和嵌入式设备中,例如:

- 缓存: 缓存用于存储最近访问的数据,以便处理器可以更快地访问它们。

- 高速缓冲器: 高速缓冲器用于在不同速度的设备之间缓冲数据。

- 存储器: SRAM 用于存储需要快速访问的数据,例如操作系统、应用程序和数据文件。

6. SRAM 阵列的优缺点

SRAM 阵列的优点包括:

- 速度快: SRAM 阵列具有比 DRAM 更快的访问速度。

- 功耗低: SRAM 阵列在空闲状态下不需要刷新,因此功耗更低。

- 耐用性强: SRAM 阵列不容易受到辐射和其他环境因素的影响。

SRAM 阵列的缺点包括:

- 成本高: SRAM 阵列的成本比 DRAM 更高。

- 密度低: SRAM 阵列的存储密度比 DRAM 低。

- 易失性: SRAM 阵列在断电后会丢失数据。

基本的 SRAM 逻辑结构

静态随机存储器(SRAM)的基本逻辑结构由存储单元阵列、译码器、读写电路和控制逻辑组成。

1. 存储单元

SRAM 的存储单元是其核心部件,由六个晶体管组成,通常被配置为跨耦合反相器。这种设计允许存储单元存储一个二进制位,0 或 1。

在 SRAM 存储单元中,两个晶体管 M1 和 M2 形成一个反相器,用于存储数据。M3 和 M4 形成另一个反相器,用于保持存储状态。M5 和 M6 用于控制对存储单元的访问。

当 M5 导通且 M6 截止时,数据可以通过 M1 和 M2 传输到存储单元。当 M6 导通且 M5 截止时,存储单元的状态被保持。

2. 存储单元阵列

SRAM 存储单元阵列由行和列组成,每个存储单元由一个唯一地址指定。行和列由解码器地址,允许对特定存储单元进行访问。SRAM 阵列通常具有多个字节或字的宽度,允许并行存储和检索多个位。

例如,一个 8x8 SRAM 阵列由 64 个存储单元组成,每个存储单元存储一个比特。该阵列有 8 行和 8 列,每个存储单元由一个 3 位地址(行地址和列地址)指定。

3. 译码器

译码器负责根据地址信号找到要访问的存储单元。它接收地址信号,并生成相应的行选择信号和列选择信号。这些信号用于控制存储单元阵列中相应存储单元的访问晶体管。

4. 读写电路

读写电路负责执行读取和写入操作。

读取操作:

- 地址信号被送到译码器,选择要读取的存储单元。

- 存储单元的状态通过读取放大器被放大并输出到数据线上。

写入操作:

- 地址信号被送到译码器,选择要写入的存储单元。

- 数据信号被加载到存储单元上。

- 写放大器将数据写入到存储单元中。

5. 控制逻辑

控制逻辑负责控制译码器、读写电路和其他组件的运行。它接收来自外部的控制信号,并根据这些信号生成相应的控制信号。

6. SRAM 逻辑结构的优点

SRAM 的基本逻辑结构具有以下优点:

- 速度快: SRAM 的存储单元可以直接访问,因此具有比 DRAM 更快的访问速度。

- 功耗低: SRAM 在空闲状态下不需要刷新,因此功耗更低。

- 耐用性强: SRAM 不容易受到辐射和其他环境因素的影响。

7. SRAM 逻辑结构的缺点

SRAM 的基本逻辑结构也存在一些缺点:

- 成本高: SRAM 的制造工艺比 DRAM 复杂,因此成本更高。

- 密度低: SRAM 的存储单元体积较大,因此存储密度比 DRAM 低。

- 易失性: SRAM 在断电后会丢失数据。

SRAM 读/写时序

SRAM 的读写操作是通过控制字线 (WL) 和位线 (BL) 的电平变化来实现的。

1. 读操作

在读操作期间,以下步骤发生:

- 选择存储单元: 地址信号被送到译码器,选择要读取的存储单元。

- 激活存储单元: 字线 (WL) 被拉高电平,选择要读取的存储单元的行。这将打开该行的访问晶体管,使存储单元连接到位线 (BL)。

- 读取数据: 存储单元中的数据通过跨耦合反相器被放大并输出到位线 (BL)。

- 感知数据: 感知放大器检测位线 (BL) 上的数据电平,并将其转换为逻辑电平。

- 输出数据: 感知放大器的输出被送到数据线上,作为读操作的结果。

- 取消选择存储单元: 字线 (WL) 被拉低电平,断开存储单元与位线 (BL) 的连接。

2. 写操作

在写操作期间,以下步骤发生:

- 选择存储单元: 地址信号被送到译码器,选择要写入的存储单元。

- 激活存储单元: 字线 (WL) 被拉高电平,选择要写入的存储单元的行。这将打开该行的访问晶体管,使存储单元连接到位线 (BL)。

- 设置位线电平: 位线 (BL) 被设置为要写入的数据的电平(高电平表示 1,低电平表示 0)。

- 写入数据: 写驱动器向位线 (BL) 施加电压,以覆盖存储单元中当前存储的数据。

- 更新存储单元: 跨耦合反相器根据位线 (BL) 上的电压更新其输出,从而将新数据写入存储单元。

- 取消选择存储单元: 字线 (WL) 被拉低电平,断开存储单元与位线 (BL) 的连接。

3. 时序图

上图显示了 SRAM 读写操作的时序图。在读操作中,字线 (WL) 在数据输出之前上升,然后下降。在写操作中,字线 (WL) 在数据写入之前上升,然后下降。位线 (BL) 在数据传输期间保持稳定。

4. 关键信号

- 字线 (WL): 用于选择要访问的存储单元的行。

- 位线 (BL): 用于传输数据到或从存储单元。

- 数据线: 用于传输读写操作的数据。

- 地址信号: 用于指定要访问的存储单元的地址。

- 读写控制信号: 用于控制读写操作的启动和停止。

存储器容量的扩展

SRAM 的内存容量可以通过多种方式扩展。一种常见的方法是使用分页架构。在这种架构中,SRAM 阵列被分为多个页面,每个页面都有自己的地址解码器和控制逻辑。这允许对多个页面进行并行访问,从而增加内存带宽并提高性能。

另一种扩展内存容量的方法是堆叠 SRAM 芯片。通过堆叠多个 SRAM 芯片并使用通过硅通孔(TSV)互连,可以实现更大的内存容量。这种 3D 堆叠技术允许在有限的物理空间内实现更高的内存密度。

此外,可以通过使用多个 SRAM 阵列并行操作来扩展内存容量。这种方法通常用于高速缓存应用程序,其中多个阵列可以同时访问,从而实现更高的吞吐量。

结论

静态随机存储器(SRAM)是一种可靠且高速的内存解决方案,广泛应用于各种应用程序中。其基本的 SRAM 存储单元阵列、逻辑结构和读/写时序使其成为高速缓存和存储应用程序的理想选择。通过扩展 SRAM 的内存容量,可以满足对更高内存需求的应用程序的要求。随着技术进步,SRAM 将继续在嵌入式系统和计算机系统中发挥关键作用。