- 1四种常用的标准自定义View方法(上)_使用过那些自定义view

- 2mac 生成目录结构tree brew安装_tree brew下载

- 3MySQL8.4 安装配置与卸载_mysql8.4安装

- 4linux桌面安全审计,Linux安全审计功能的实现——audit详解

- 5使用ExcelWriter导出数据到excel表时出现字段缺失的问题 2021.6.30_excelwriter.write() 导出没数据

- 6python 堆的使用 heapq_heapq 包

- 7如何不使用代理服务从hugging face上下载大模型?_hugging face 代理

- 8GitBook 从懵逼到入门

- 9Android程序设计之音乐播放器实现_android开发音乐播放器

- 10转--Hadoop集群部署案例

二、15【FPGA】呼吸灯实现_fpga呼吸灯实验报告

赞

踩

前言

学习说明此文档为本人的学习笔记,注重实践,关于理论部分会给出相应的学习链接。

学习视频:是根据野火FPGA视频教程——第十八讲

https://www.bilibili.com/video/BV1nQ4y1Z7zN?p=3

实战演练

一、设计规划

1.1 实验目标

在开发板上实现LED灯实现呼吸灯效果,工作原理是利用PWM来控制小灯在相同的时间段内的不同占空比,即在同样小时间段内,小灯亮的时间依次增加到最大后再依次减少,从而实现渐亮到渐灭的“呼吸”效果。

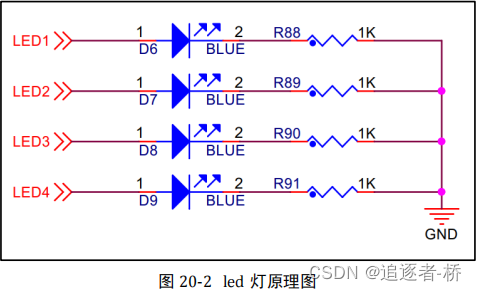

1.2 硬件资源

这里采用野火的升腾mini板进行实验

led灯原理图

二、程序设计

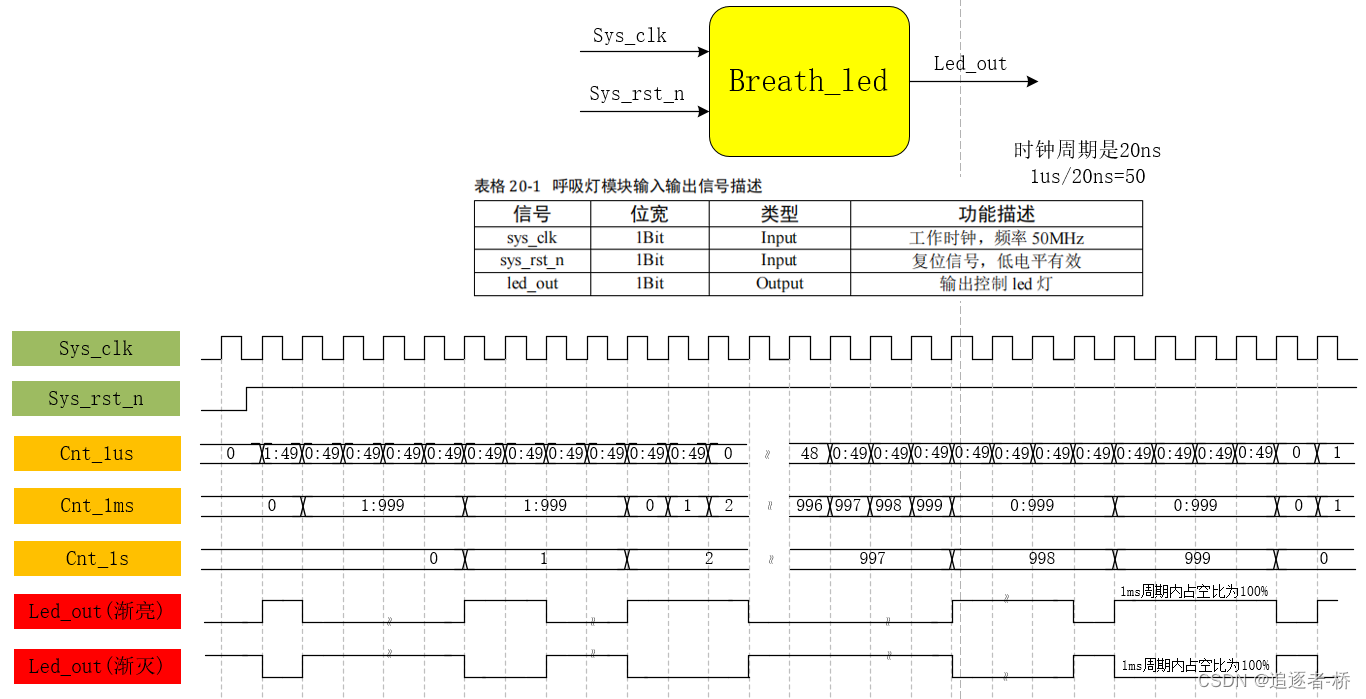

2.1 波形图绘制

PWM占空比控制灯亮的程度,假设led灯亮1s灭1s,实现渐亮与渐灭,由于两者类似只说渐亮。

为使渐亮的更细腻,这里将1s分为1000份,即1ms为一个时间周期,控制1ms时间内的导通时间即可以控制led灯的亮度,这里将1ms分为1000个小段(即1us),控制渐亮如:第一个1ms内让其导通1us;第二个1ms内导通2us;第三个1ms内导通3us;......;第1000个1ms内导通999us。逐渐,变灭与之相反。为区分渐亮与渐灭的时间,这里添加1s的时间标志cnt_en,1s后标志进行取反,当高电平时执行渐亮,当低电平时执行渐灭

2.2 代码编写

为了便于仿真代码对程序进行仿真,这里将计数器最大常数用parameter在模块前定义

- module breath_led

- #(

- parameter CNT_1US_MAX = 6'd49 ,

- parameter CNT_1MS_MAX = 10'd999 ,

- parameter CNT_1S_MAX = 10'd999

- )

- (

- input wire sys_clk ,

- input wire sys_rst_n,

- output reg led_out

- );

- reg [5:0] cnt_1us;

- reg [9:0] cnt_1ms;

- reg [9:0] cnt_1s;

- reg cnt_en;

- //us计数器

- always@(posedge sys_clk or negedge sys_rst_n)

- if(sys_rst_n == 1'b0)

- cnt_1us <= 6'd0;

- else if(cnt_1us == CNT_1US_MAX)

- cnt_1us <= 6'd0;

- else

- cnt_1us <= cnt_1us + 6'd1;

- //ms计数器

- always@(posedge sys_clk or negedge sys_rst_n)

- if(sys_rst_n == 1'b0)

- cnt_1ms <= 10'd0;

- else if((cnt_1ms == CNT_1MS_MAX) && (cnt_1us == CNT_1US_MAX))

- cnt_1ms <= 10'd0;

- else if(cnt_1us == CNT_1US_MAX)

- cnt_1ms <= cnt_1ms + 10'd1;

- else

- cnt_1ms <= cnt_1ms;

- //s计数器

- always@(posedge sys_clk or negedge sys_rst_n)

- if(sys_rst_n == 1'b0)

- cnt_1s <= 10'd0;

- else if((cnt_1us == CNT_1US_MAX)

- && (cnt_1ms == CNT_1MS_MAX)

- && (cnt_1s == CNT_1S_MAX))

- cnt_1s <= 10'd0;

- else if((cnt_1us == CNT_1US_MAX) && (cnt_1ms == CNT_1MS_MAX))

- cnt_1s <= cnt_1s + 10'd1;

- else

- cnt_1s <= cnt_1s;

- //添加渐亮与渐灭标志

- always@(posedge sys_clk or negedge sys_rst_n)

- if(sys_rst_n == 1'b0)

- cnt_en <= 1'b1;

- else if((cnt_1us == CNT_1US_MAX)

- &&(cnt_1ms == CNT_1MS_MAX)

- &&(cnt_1s == CNT_1S_MAX))

- cnt_en <= ~cnt_en;

- else

- cnt_en <= cnt_en;

- always@(posedge sys_clk or negedge sys_rst_n)

- if(sys_rst_n == 1'b0)

- led_out <= 1'b0; //led灯熄灭

- else if((cnt_en == 1'b1) && (cnt_1ms <= cnt_1s)

- ||(cnt_en == 1'b0) && (cnt_1ms > cnt_1s))

- led_out <= 1'b1;

- else

- led_out <= 1'b0;

- endmodule

在编写代码时遇到的问题: cnt_1us <= cnt_1us + 6'd1; cnt_1us = cnt_1us + 6'd1;

将代码中的阻塞赋值错写成了非阻塞赋值,“cnt_1us = cnt_1us + 6'd1;”该语句只有在执行完后才能执行后面的其他赋值语句,这样就会导致cnt_1us在最大时刻的前面和后面都会出现cnt_1ms出现跳变的现象,阻塞赋值判断的并不是该时刻的前状态,而是执行完的后状态。

三、逻辑仿真

3.1 仿真代码

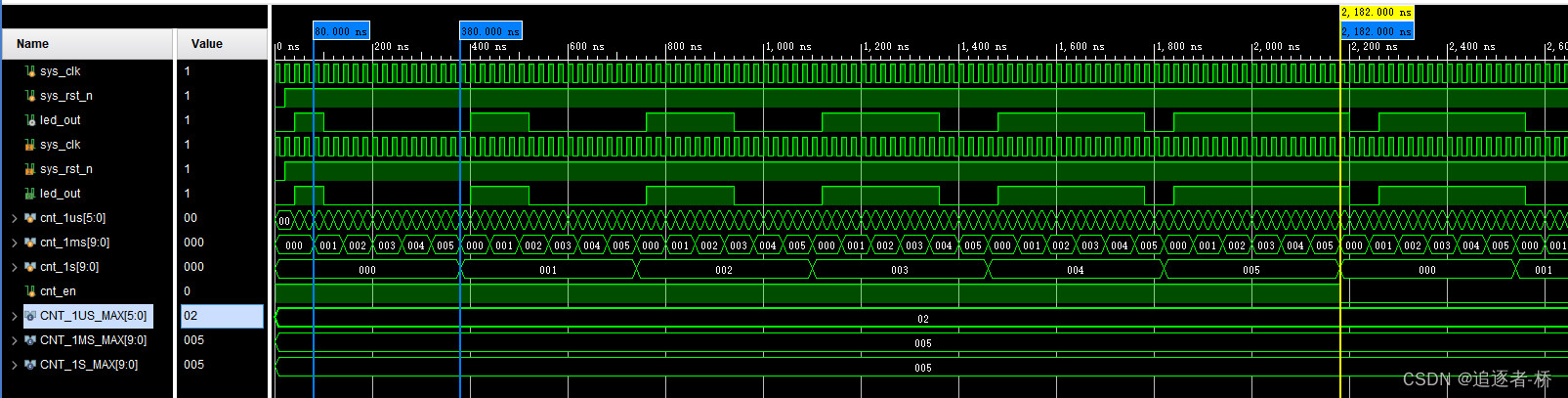

为了方便仿真代码的实现,这里修改最大值常数变为2,5,5

- `timescale 1ns / 1ns

- //

- // Company: 追逐者——桥的小作坊

- // Create Date: 2022/05/13 21:26:31

- // Design Name: 呼吸灯

- // Module Name: tb_breath_led

- //

- module tb_breath_led();

- reg sys_clk;

- reg sys_rst_n;

- wire led_out;

- initial begin

- sys_clk = 1'b1;

- sys_rst_n <= 1'b0;

- #20

- sys_rst_n <= 1'b1;

- end

- always #10 sys_clk = ~sys_clk;

- breath_led

- #(

- .CNT_1US_MAX(6'd2 ),

- .CNT_1MS_MAX(10'd5),

- .CNT_1S_MAX (10'd5)

- )

- breath_led_inst

- (

- .sys_clk (sys_clk ),

- .sys_rst_n(sys_rst_n),

- .led_out (led_out )

- );

- endmodule

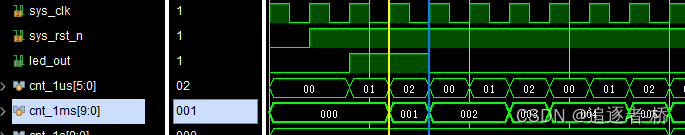

3.2 波形图对比

如图可知三个计数器的计数波形是正确的,输出与绘制的原理图也相同。

四、上板验证

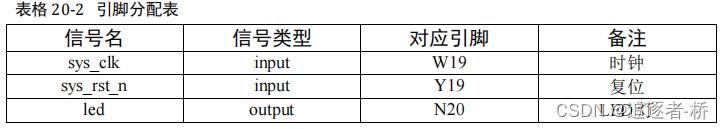

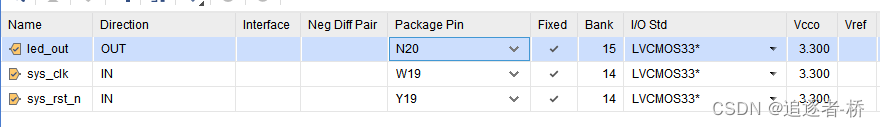

4.1 管脚绑定

Ctrl+s进行保存

4.2 程序下载

生成bit流文件,连接板卡,下载程序

PFGA—呼吸灯实现