- 1Unity2D学习笔记Day13:添加音效Audio_unity增加个吃金币的声音

- 2echarts 社区网站

- 3Drv8434s芯片两相步进电机驱动程序+硬件解决方案

- 4查询oracle序列当前值和最大值,修改最大值_oracle修改序列的最大值

- 5吴恩达深度学习网课 通俗版笔记——(05.序列模型)第二周 自然语言处理与词嵌入_词嵌入做迁移学习

- 6Python制作自动化脚本通用版教程_python编写自动化挂机脚本

- 7ChatGLM3-6B部署_chatglm3 6b最低部署要求

- 8HashMap源码解析

- 9elementUI upload上传文件时携带token_el-upload 携带token

- 10兴业数金测开一面面经_兴业数金 测试 面经

SerDes系列之DFE均衡技术_serdes ffe

赞

踩

反馈判决均衡 Decision feedback Equalizer (DFE)

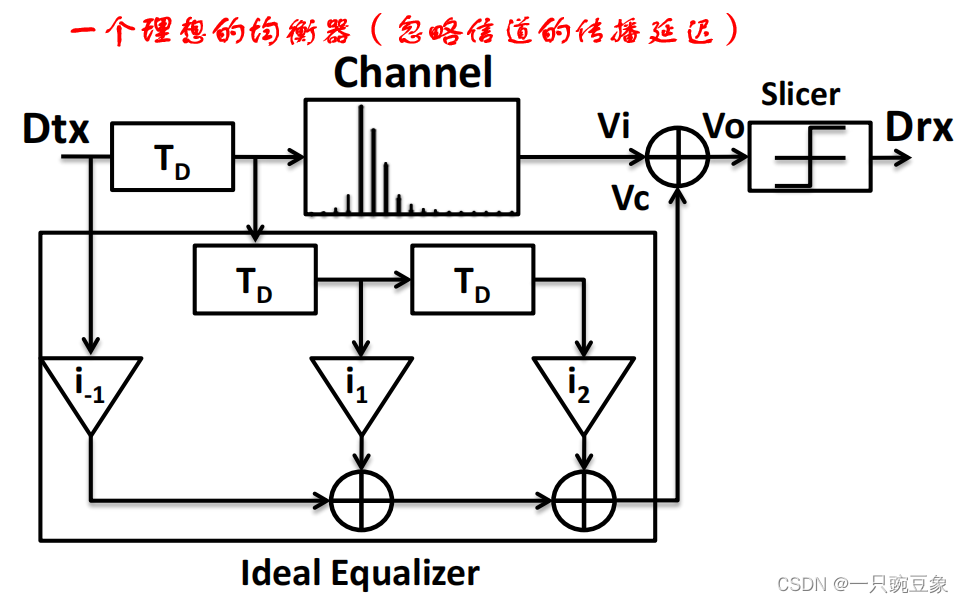

当我们仔细研究FFE的“噪声放大”问题时,会发现,主比特位和前后校正位都必须经历信道衰减,换句话说,由于它的线性滤波器特性,存在于校正位中的噪声将与主信号相结合,对信道ISI的均衡效果产生影响。如果在某种程度上,可以使用“干净的”校正位来应用于主信号路径上的ISI抵消,信道损失将在不引入任何噪声放大的前提下进行均衡。这个思维引导出如下图所示的均衡器结构。

在这种配置下,校正位是来自发射机的干净的数字信号,它永远不会被信道损耗或任何其他噪声源污染,因此可以在不影响主信号的动态范围或不引入任何额外噪声的情况下消除信道的ISI。当然,在现实中,将不存在这样一个理想的旁路通道来发送干净的TX数据到RX端,但是,在实际系统中,经过RX限幅比较器(Slicer)后恢复的数字位可以作为这些干净校正位的理想替代,从而导致反馈判决均衡器架构的出现,DFE使用干净的“数字”决策来纠正尾随的ISI(Post-cursor),从而避免了高频噪声放大的问题。

由于Slicer本质上消除了从信道中引入的所有噪声,因此它的输出可以被视为所需的与信道无关的位源,但是,由于它的反馈性质,DFE不能取消来自于Pre-cursor的ISI。

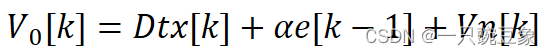

一种单抽头(1-tap)DFE均衡器结构如图所示,其中,Dtx和Drx分别是发射和接收的数字数据,Vi表示经过信道传输后的模拟信号(即受到通道ISI影响的数据),它在接收端DFE输入处与噪声电压Vn和反馈校正电压Vc进行了求和,以生成送入限幅器的Vo,其中d1取值的正负取决于Drx的极性。

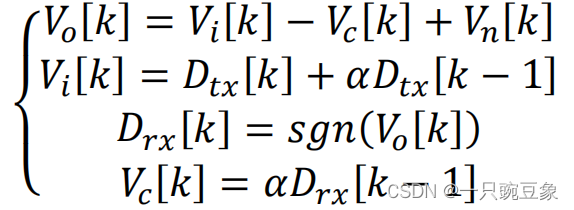

假设1-tap的DFE可以理想地去除通道ISI的影响,则上述参数的逻辑关系可以表述如下(此时,d1=α):

换言之,DFE将使用Vc的αDrx[k−1]完美抵消Vi中的αDtx[k−1]分量,因此,当d1取值越大时,被抵消的幅度就会越多,在Drx得到的有效数字数据的幅度也就越小,由此可见,好的信道设计,对于DFE的上限使用尤为重要。

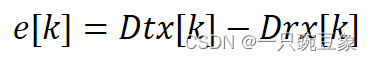

上述在理想状态下得出的参数之间的对应关系,实际中,传输位和接收位之间总是存在错误的,假设这个错误定义为:

实际得到的V0为:

这种潜在的错误主要有三种表现形式:

1. 当接收器做出正确判决后,输出为0;

2. 传输位为-1,但接收机做出了+1的判决;

3. 传输位为+1,但接收机做出了-1的判决。

因此,在DFE的设计中,就需要具备对上述错误的预判机制,这是一套复杂的设计流程,尤其是存在多个抽头的设计,DFE运算将更为复杂,这些内容都已超出本文的讨论范畴。

DFE虽然可以有效“弥补”FFE所带来的高频噪声放大问题,但是其面临的最大的技术难点是:不可避免地引入了反馈环路带来的延时问题,尤其当考虑到抽头运算所需时间必须远远小于一个UI单元时,使得DFE设计非常具有挑战性。并且,随着抽头数量的增加,这种技术复杂性将以指数级上升,这也限制了多抽头DFE技术在高速领域的应用,如常见的USB、PCIE等,都还是以单抽头方案为主。

一些改进方案:

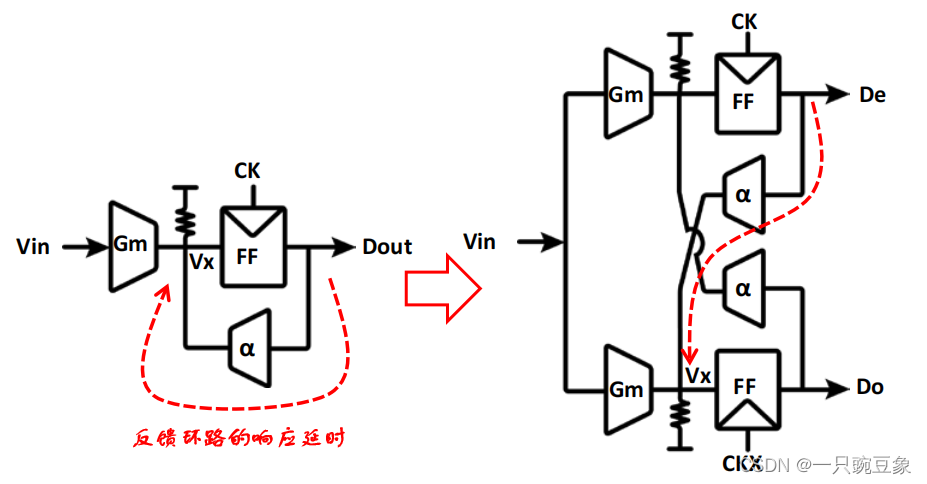

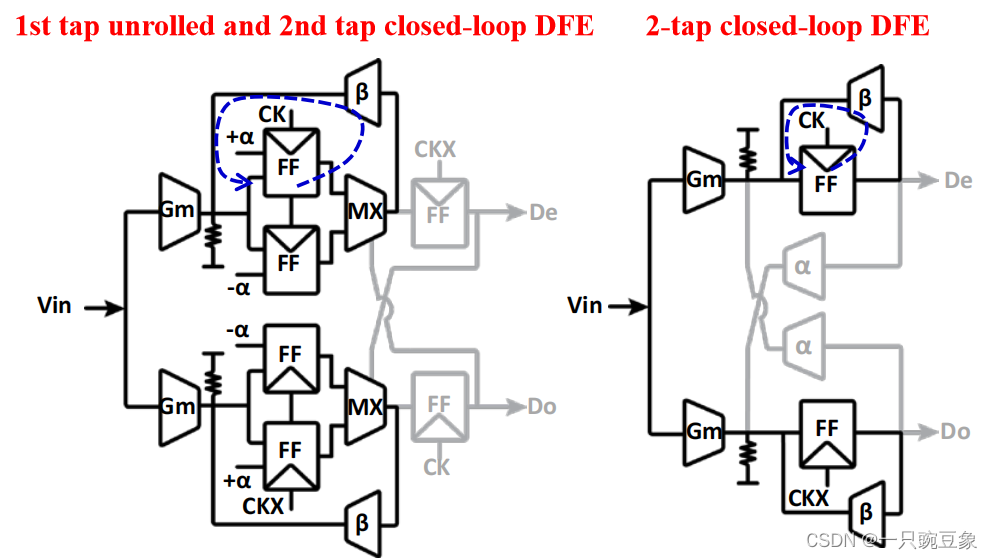

采用如图所示的双数据速率(DDR)体系结构有助于降低对于电路吞吐量的要求,但是,DDR结构并不能修改第一次tap采样时间,因此,也就不能完全解决响应延时的问题。

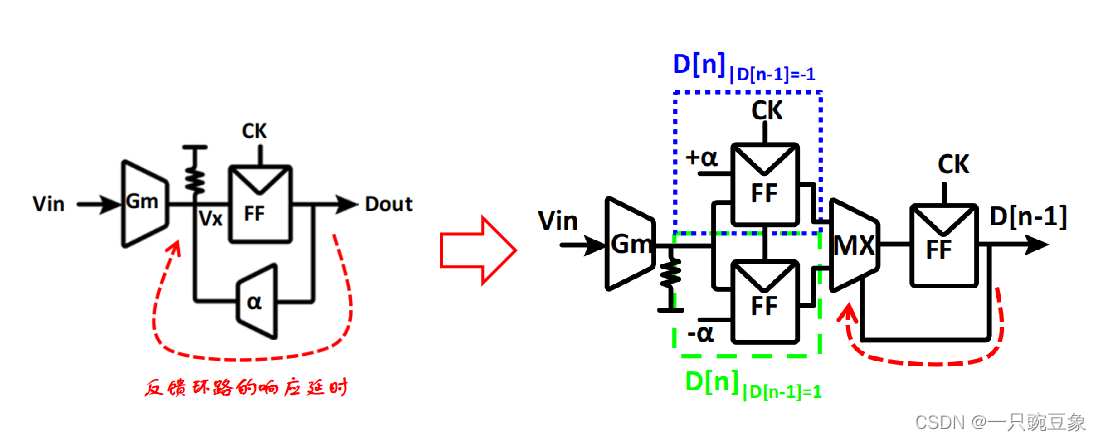

为了放松严格的第一次tap采样时间的约束,引入了loop-unrolling DFE体系结构,并在许多单抽头DFE设计中广泛采用。对于数字信号而言,前一位要么是1要么是-1,因此在输入端应用−α或+α的静态偏移量(α是Post-cursor的ISI的绝对幅值),因此,可以同一时间对不同的输入状态进行校正,但是,这种结构中反馈并没有彻底消除,因为在后级选择电路中依然存在环路,只是反馈从模拟端转移到了数字端,相对而言,反馈的响应时间会被加快。

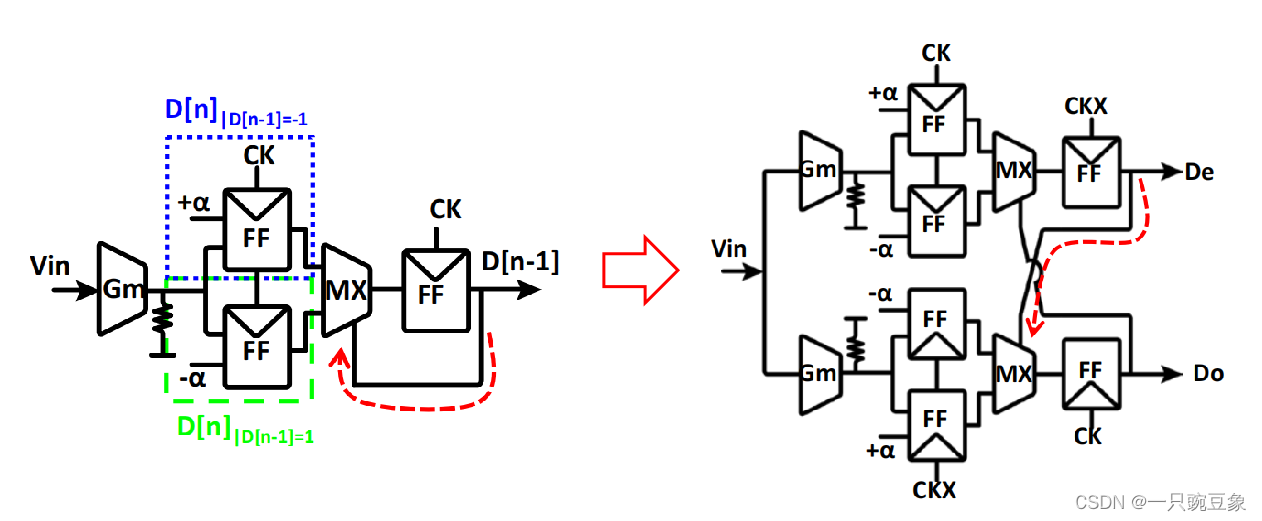

相应的,也可以在loop-unrolling DFE结构应用DDR体系以降低数据的吞吐量,这样就可以达到在单抽头DFE中取得“一举两得”的设计效果。

不幸地是,这种架构同样带来了其它的问题,由于使用了额外的选择器MX的延迟,它会给多抽头方案带来负担,特别是当1st loop-unrolling和2nd closed-loop DDR DFE组合使用时,延时会被明显加大,此时,其效果反而不如2-taps closed-loop DDR DFE的组合。

当然,也可以对loop-unrolling的结构进行级联以规避上述问题,但是,随着taps的数量增加,所需硬件(Slicer、MX等)的数量也在增长,带来了更多的寄生电容,导致大量的额外负载,从而增加了解决方案的能耗等级,应用中就会更加的耗电。

综上所述,DFE电路架构的最终设计目标,是在花尽可能少的反馈时间和能耗的同时,满足最大程度地信号恢复,新的技术还有很多,本文不足以一一陈述,并且由于改进设计过于复杂和专业,以后的写作中有机会再做专题讨论。

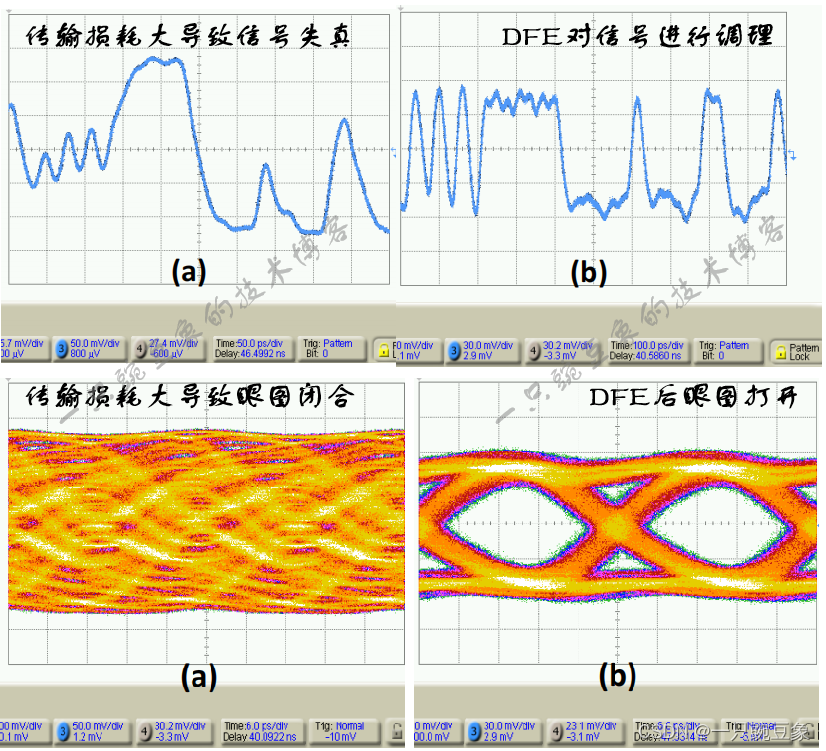

最后,从实际的Rx Die端DFE处理效果上,可以观察到,由于加权和限幅器的使用,虽然对信号的高频损耗进行了显著地修复,但伴随着电压幅度的降低和眼高的减小,应用中,应额外关注此变化对设计裕量的影响。

前文阅读

参考文献

[1] Energy-Efficient Equalization Circuits for High-Speed Wireline Links, Yue Lu;

[2] The Decision-Feedback Equalizer, Behzad Razavi.