热门标签

热门文章

当前位置: article > 正文

【无标题】_ad7616驱动程序

作者:木道寻08 | 2024-07-15 13:01:02

赞

踩

ad7616驱动程序

AD7606 verilog驱动程序

所谓驱动程序是指FPGA产生AD7606所需要的控制信号,包括RESET、CONVST、CS、RD,以及8个通道的数据。

转换控制

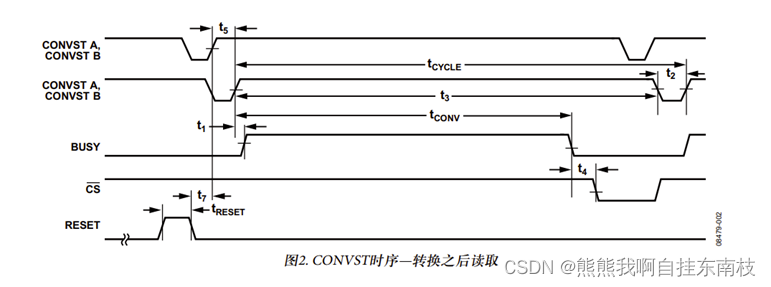

查看AD7606的芯片资料,转换之后读取的时序图为:

- RESET复位信号高电平有效,并且需要持续至少50ns。

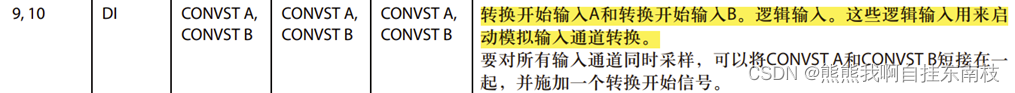

- CONVST转换(AD转换)开始信号,当CONVST信号由低变高时前端输入保持。两个CONVST引脚连在一起时,在上升沿启动对所有模拟输入通道同步采样。

CONVST低电平至少保持25ns。

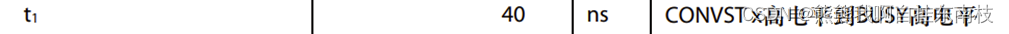

BUSY信号告知用户正在进行转换,因此当施加CONVST上升沿时,BUSY变为逻辑高电平,在整个转换过程结束时变为低电平。

读取控制

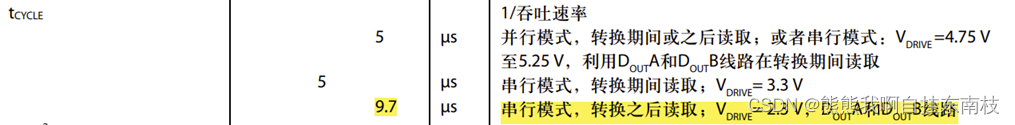

并行模式,转换之后读取。转换周期为5us。

3. CS片选信号低电平有效,t4等于零,即当BUSY拉低之后可立即拉低CS信号

- RD读取信号低电平有效。

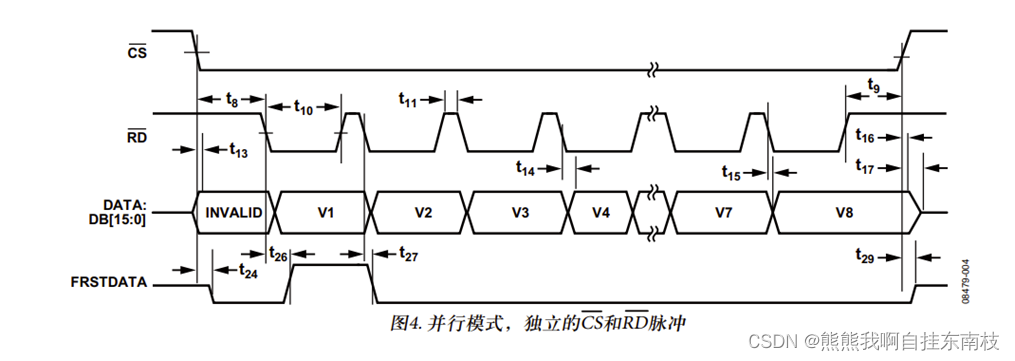

数据读取采用并行模式,输入独立的CS和RD信号。CS下降沿使总线脱离高阻状态,是使能数据线的控制信号。RD引脚用来从输出转换结果寄存器读取数据,使各通道的转换结果按升序逐个输出到并行总线。Busy变为低电平后的第一个RD下降沿输出通道V1的转换结果,下一个RD下降沿则用V2转换结果更新总线。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/木道寻08/article/detail/829483

推荐阅读

相关标签