热门标签

热门文章

- 1技术管理成长计划(一):角色认知及转身_主计划角色认知

- 2深度学习进阶之路 - 从迁移学习到强化学习_深度学习和学习进阶的本质

- 3Hadoop的MapReduce详解_hadoop mapreduce

- 4web前端顶岗实习总结报告_web前端实习报告

- 5使用 Langchain 和 Ollama 的 PDF 聊天机器人分步指南

- 62019年全国电子设计竞赛H题电磁炮之定点打击_电赛电磁炮代码

- 7MySQL常见报错及解决方案_invalid default value for 'gender

- 8【Docker】搭建一个媒体服务器插件后端API服务 - MetaTube

- 9基于单片机的教室智能照明台灯控制系统的设计与实现_基于51单片机的教室智能照明控制设计

- 10如何用JAVA如何实现Word、Excel、PPT在线前端预览编辑的功能?_前端在页面上编辑ppt和word的插件

当前位置: article > 正文

ZYNQ-PS与PL交互(AXI_LITE)_zynq使用axi-lite协议实现ps与pl简单通信

作者:木道寻08 | 2024-07-15 18:30:17

赞

踩

zynq使用axi-lite协议实现ps与pl简单通信

整体设计

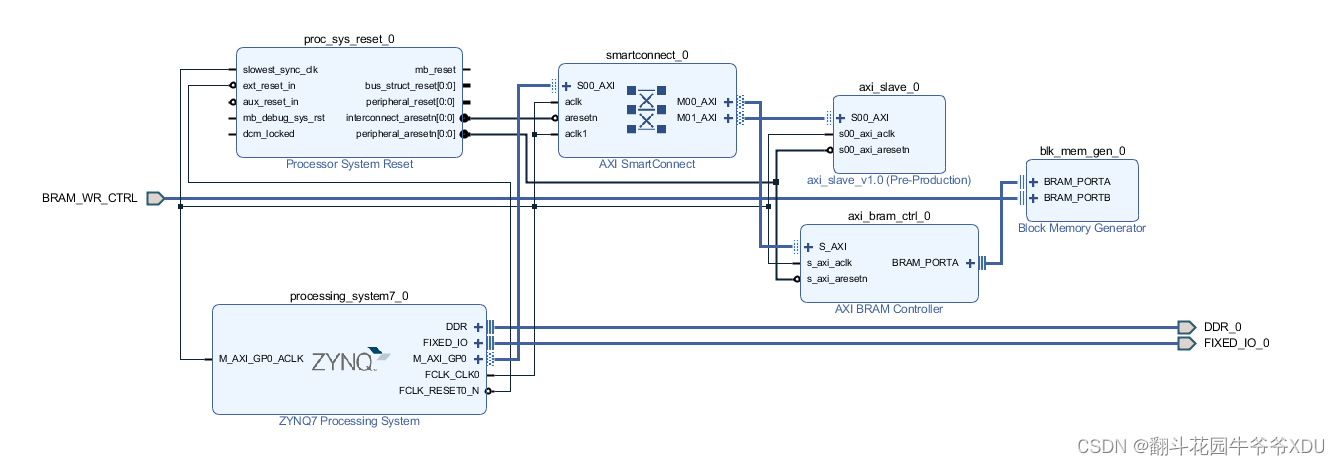

两种设计,一种由PS通过AXI_LITE将数据放入PL端的BRAM中,但后读出。另外一种PS端通过AXI_LITE将数据直接写入到PL端。

BD设计

注意:

- BRAM Controler 如果设置两个输出端口,A端口是写,B端口是读。如果只设置一个端口,那么这个端口可写可读。

- BRAM的大小配置不了,它的大小随着AXI总线变化而变化。

- 线路一:由PS通过GP口向AXI_SlAVE写数据。

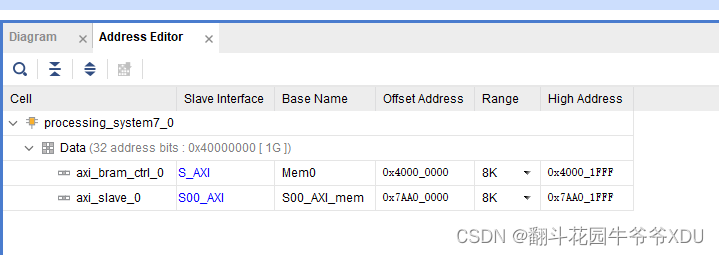

- 线路二:BRAM路线,将BRAM地址空间分为空间一,空间一为PL端的BRAM_WR_CTRL写入数据,PS端通过GP读出,空间二由PS通过GP口写入数据,PL端的BRAM_WR_CTRL读出。

BRAM_WR_CTRL设计

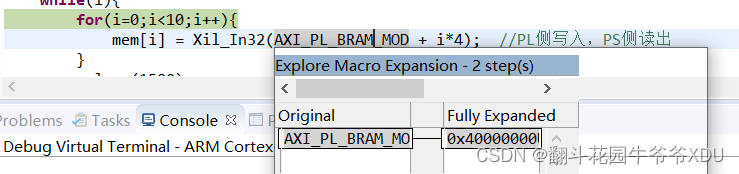

首先PL侧向BRAM模块写入40个32bit的数据,BRAM模块地址是字节地址,此处要计算地址自增,BRAM中地址空间是0-40,这里每一个空间存放的是一个字节,4个字节组成一个数。在PS端读取的时候,使用Xil_In32即可读出

else if(cnt >=100 && cnt < 100 + ((WRITE_DATA_NUM * (DATA_WIDTH/4))))begin

ro_addr <= WRITE_BASE_ADDR + ((cnt - 100)<<2);

ro_wr_data <= cnt - 100;

ro_wr_en <= 4'b1111;

ro_bram_en <= 'd1;

end

- 1

- 2

- 3

- 4

- 5

- 6

写完之后,改成PL读出PS端写入的数据

//PS侧写入地址,PL侧读出

else if(cnt >=100 && cnt < 100 + ((WRITE_DATA_NUM * (DATA_WIDTH/4))))begin

ro_addr <= WRITE_BASE_ADDR + ((cnt - 100)<<2);

ro_wr_data <= cnt - 100;

ro_wr_en <= 4'b1111;

ro_bram_en <= 'd1;

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

总体代码

`timescale 1ns / 1ps module Bram_Wr_Ctrl # ( parameter WRITE_BASE_ADDR = 0 , READ_BASE_ADDR = 40 , DATA_WIDTH = 32 , WRITE_DATA_NUM = 40 , READ_DATA_NUM = 40 )( input i_clk , input i_rst , output [31:0] o_addr , output [31:0] o_wr_data , input [31:0] i_rd_data , output o_bram_en , output [3:0] o_wr_en ); reg [31:0] ro_addr ; reg [31:0] ro_wr_data ; reg [3:0] ro_wr_en ; reg ro_bram_en ; reg [10:0] cnt ; assign o_addr = ro_addr; assign o_wr_data = ro_wr_data ; assign o_bram_en = ro_bram_en; assign o_wr_en = ro_wr_en; always @(posedge i_clk or posedge i_rst) begin if(i_rst) cnt <= 'd0; else if(cnt == 1500) cnt <= 'd0; else cnt <= cnt + 1; end always @(posedge i_clk or posedge i_rst) begin if(i_rst)begin ro_addr <= 'd0; ro_wr_data <= 'd0; ro_wr_en <= 4'd0; ro_bram_en <= 'd0; end //PL侧写入地址,PS侧读出 else if(cnt >=100 && cnt < 100 + ((WRITE_DATA_NUM * (DATA_WIDTH/4))))begin ro_addr <= WRITE_BASE_ADDR + ((cnt - 100)<<2); ro_wr_data <= cnt - 100; ro_wr_en <= 4'b1111; ro_bram_en <= 'd1; end //PS侧写入地址,PL侧读出 else if(cnt >= 900 && cnt < 900 + ((READ_DATA_NUM * (DATA_WIDTH/4))))begin ro_addr <= READ_BASE_ADDR + ((cnt - 900) << 2); ro_wr_data <= 0; ro_wr_en <= 4'b0; ro_bram_en <= 'd1; end else begin ro_addr <= ro_addr; ro_wr_data <= ro_wr_data; ro_wr_en <= ro_wr_en; ro_bram_en <= ro_bram_en; end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

调试记录

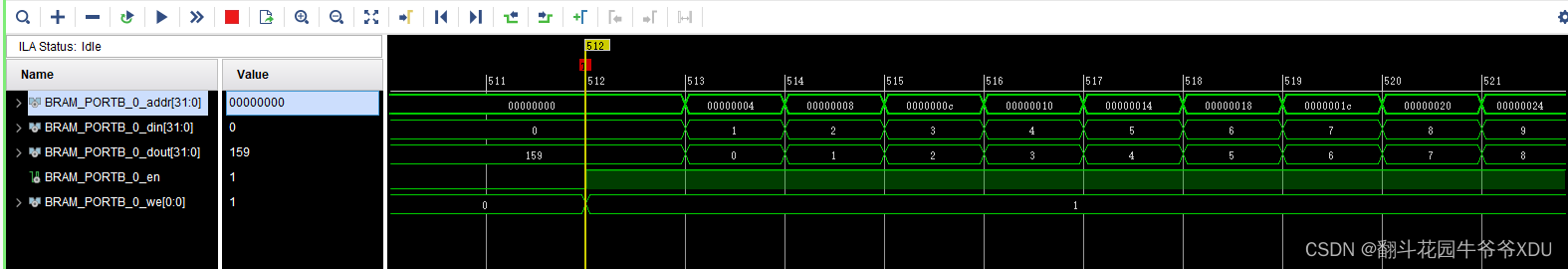

通过ILA抓取可知:PL侧写入BRAM以4Byte对齐地址写入数据Din,数据正确

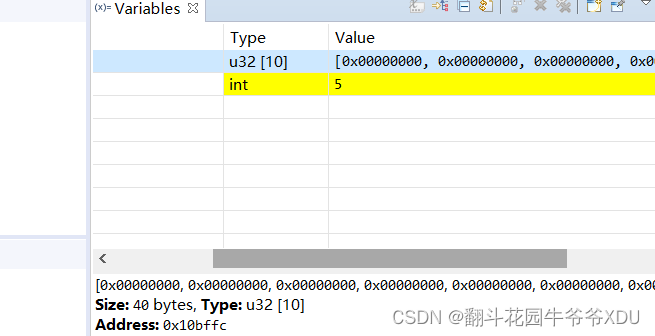

AXI对应BRAM接口的地址空间,但PS端读出的数据全是0

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/木道寻08/article/detail/830586

推荐阅读

相关标签