- 12024年Java最全爱了!Alibaba内部出品的“千万级并发商城项目”再造笔记,springcloud视频资源

- 2唯众中职人工智能专业解决方案_人工智能中职 方案

- 3【手势识别】基于matlab交警手势类型识别【含Matlab源码 3267期】_基于matlab的手势识别系统

- 4n皇后问题 题解

- 5安装ROS出现 Unable to Correct Problems ‘You have Held Broken Packages’ 错误_安装ros2e: unable to correct problems, you have held

- 6stable diffusion ——img2img Api参数数据格式参考,插件包含ControlNet和roop换脸

- 7anaconda powershell prompt中的指令

- 8QT连接MySQL_qt 连接mysql

- 9使用git创建项目

- 10linux docker漏洞,安装shadow或linux-pam的Alpine Linux Docker镜像有漏洞,附解决

基于Verilog 语言开发的FPGA密码锁工程。通过矩阵键盘输入按键值_verilog设计可视密码锁

赞

踩

基于Verilog 语言开发的FPGA密码锁工程。

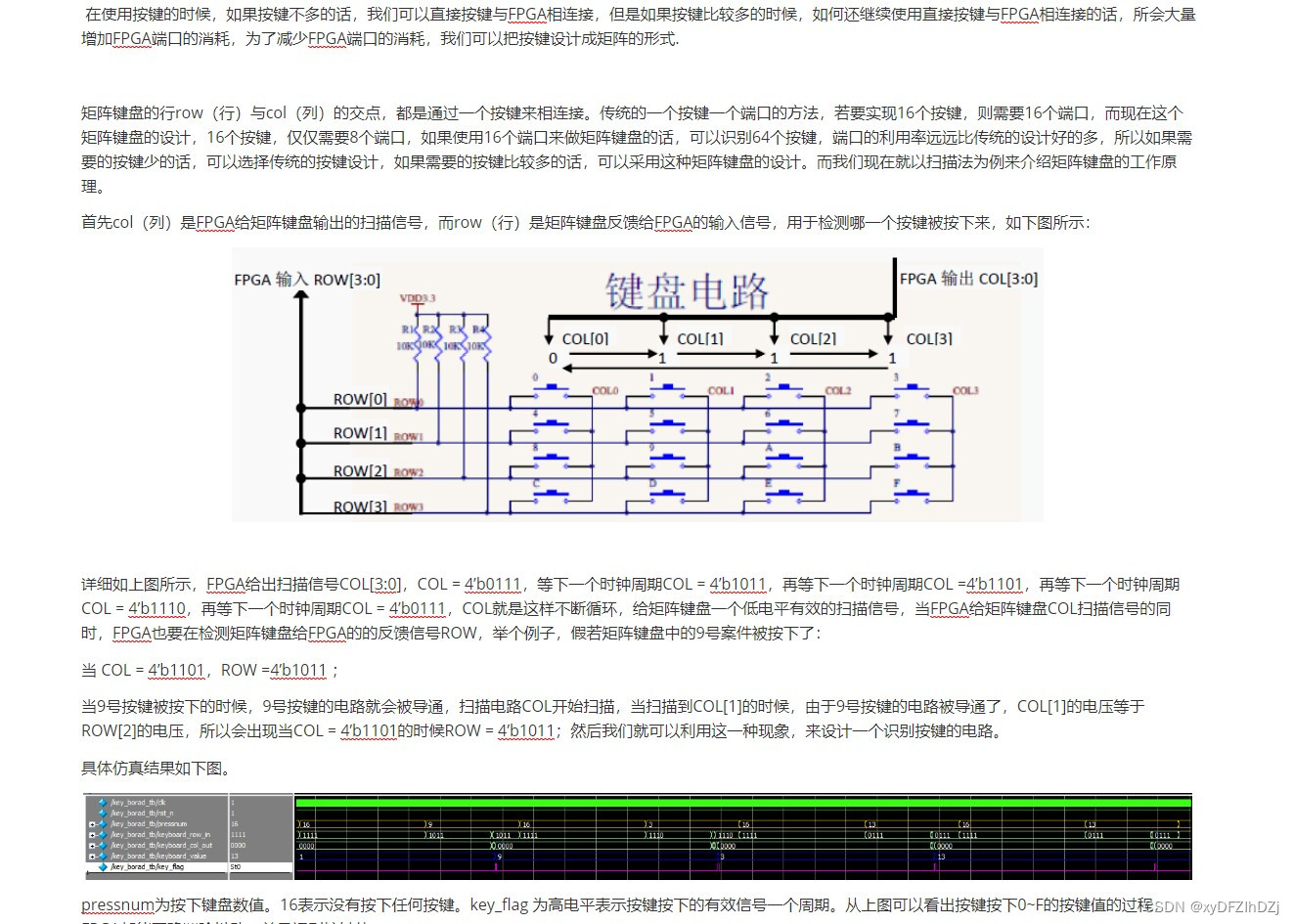

通过矩阵键盘输入按键值。

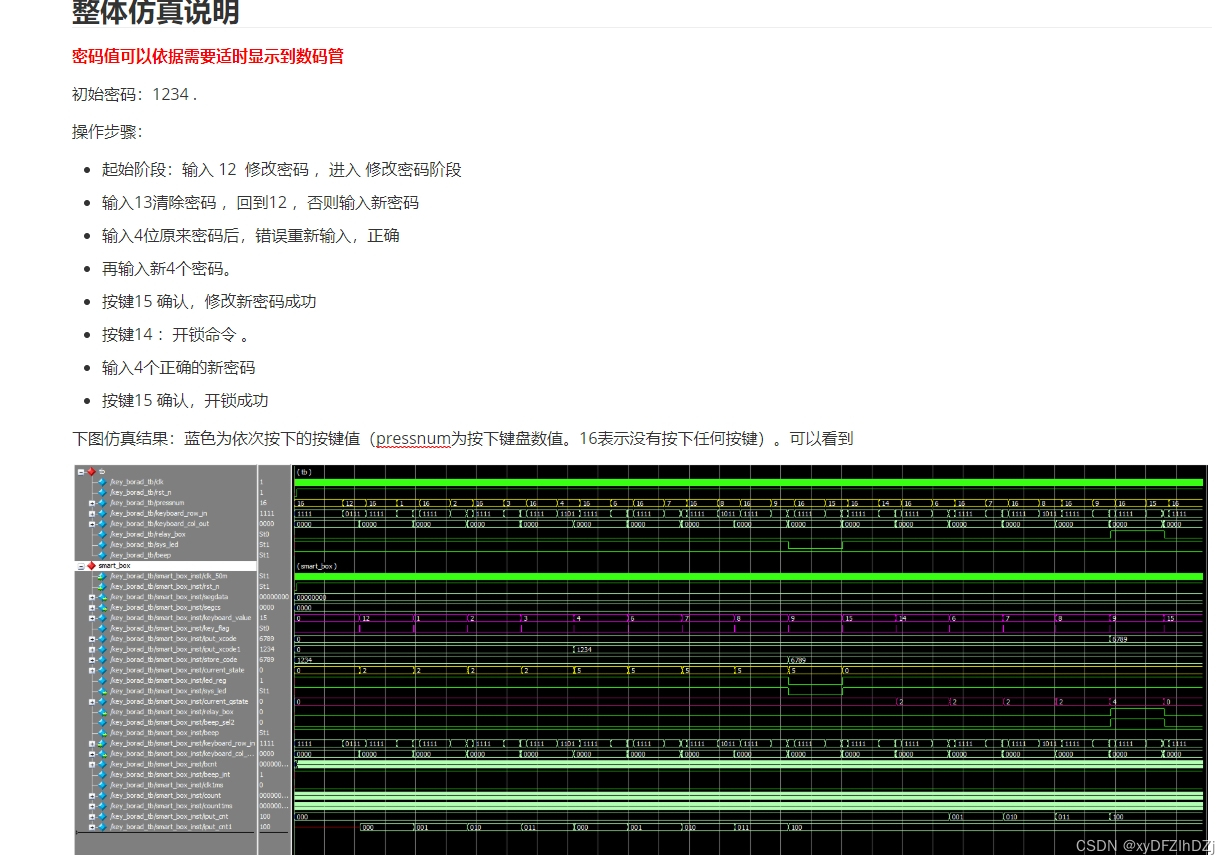

输入12修改密码,13清除密码,可以修改原来默认的密码,修改时首先要输入当前密码进行验证,正确后才能更新当前密码,否则修改不成功。

修改结束后按键15,确认修改成功。

也直接使用默认密码作为最终密码使用。

按键14,进入开锁阶段之后,输入密码进行开锁。

有两个版本,分别为Quartus 和vivado 两个版本。

工程均带有完整的仿真模块。

前两张图为一个简单文档说明。

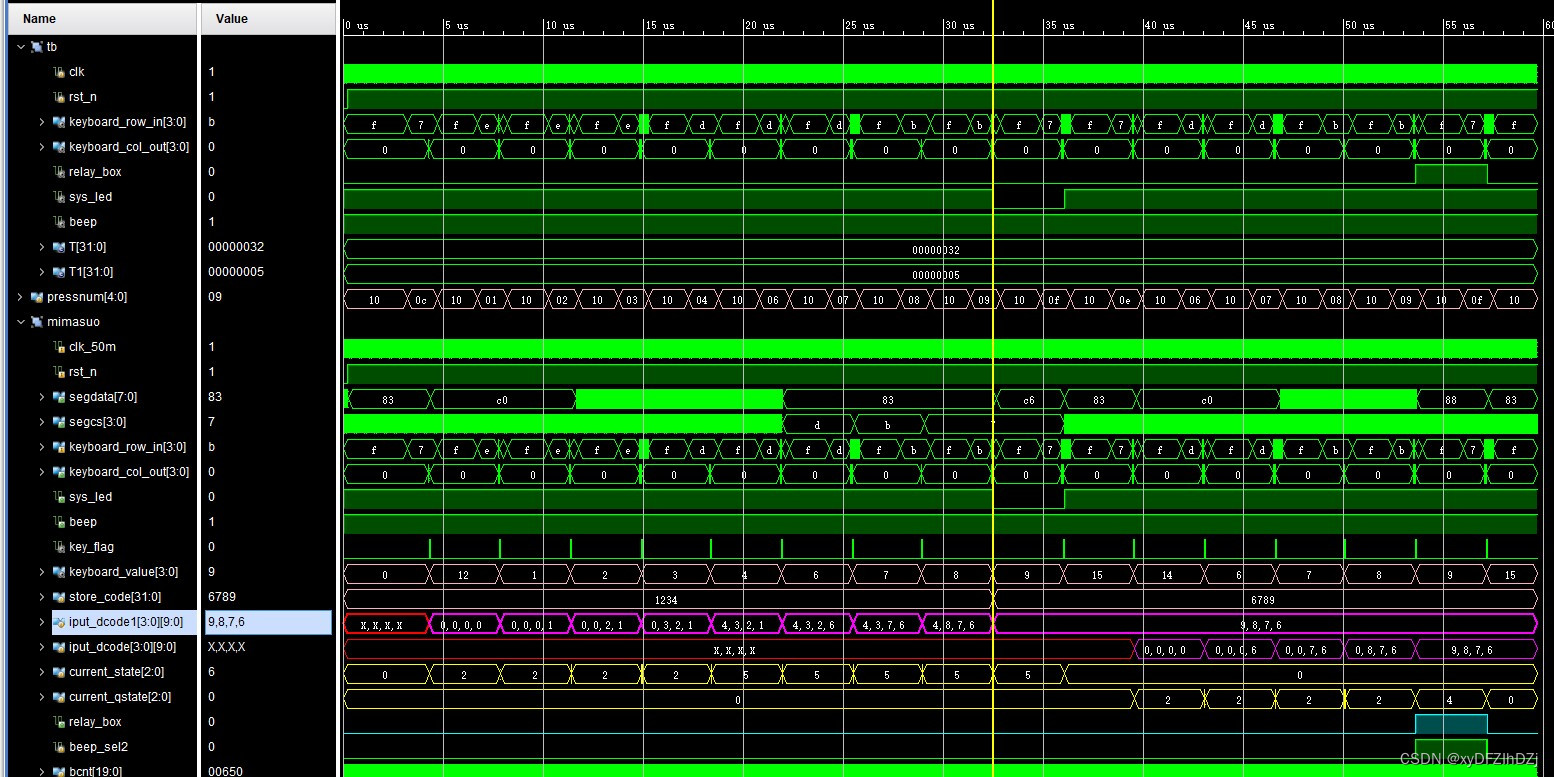

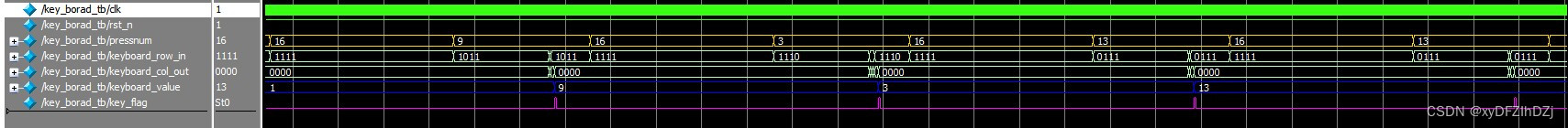

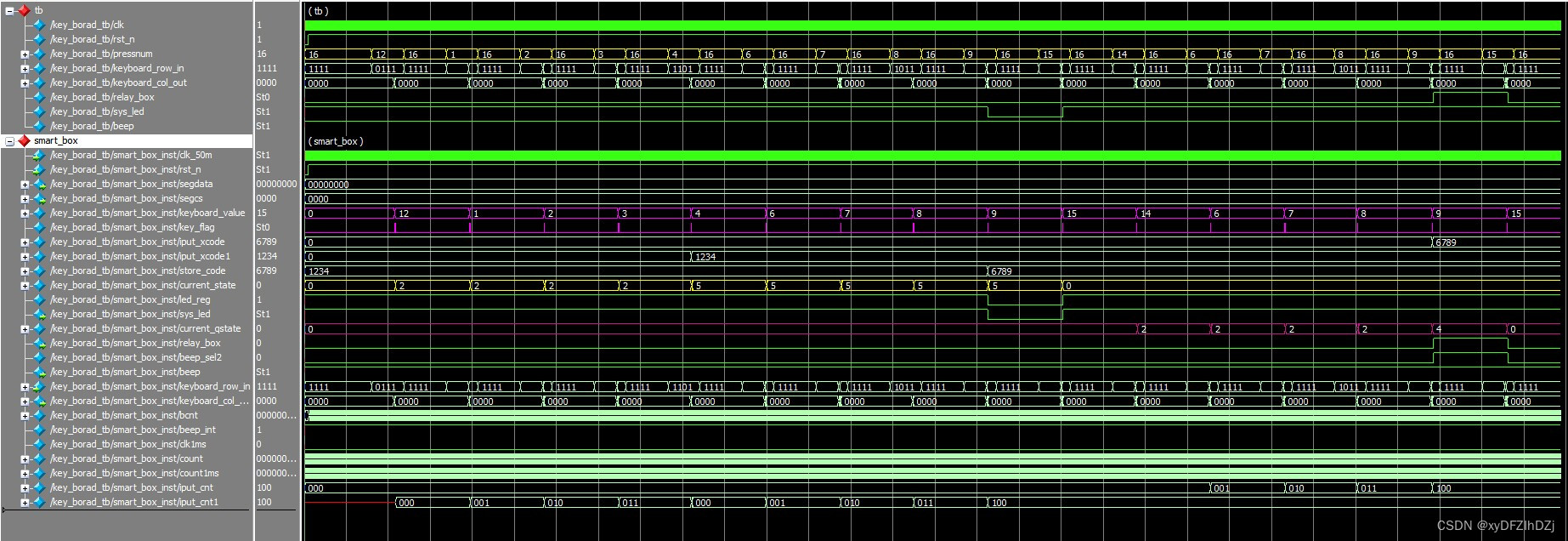

最后两张图为quartus的仿真图。

【技术分析】基于Verilog 语言开发的FPGA密码锁工程

随着科技的不断发展,密码锁已经成为现代人们生活中不可缺少的一部分。在密码锁的应用中,FPGA技术的出现,为密码锁的开发提供了新的途径。本文将介绍基于Verilog 语言开发的FPGA密码锁工程,探讨其原理和设计思路。

一、密码锁的基本需求

本工程的密码锁共有两个版本,分别为Quartus和vivado 两个版本。其基本需求如下:

1、通过矩阵键盘输入按键值。

2、可以修改原来默认的密码,并且修改时首先要输入当前密码进行验证,正确后才能更新当前密码,否则修改不成功。

3、有一个确认修改成功的按键。

4、按键13用于清除密码,按键12用于修改密码。

5、按键14进入开锁阶段,输入正确密码即可开锁。

二、基于Verilog语言的设计思路

Verilog语言是一种硬件描述语言,它在硬件设计中广泛应用。使用Verilog语言可以实现对硬件电路的描述,以及对硬件电路的仿真和测试。因此,在设计FPGA密码锁的过程中,我们选择使用Verilog语言作为开发工具。

在开始设计工程前,我们需要首先确定FPGA密码锁的整体框架。在本篇文章中,我们选择使用Quartus和vivado两个版本进行设计。

1、Quartus的设计思路

在Quartus的设计中,我们采用了经典的状态机模型。使用状态机模型可以将整个程序划分为多个状态,使得程序的结构更加清晰。具体实现如下:

首先,输入部分需要通过矩阵键盘接收按键值,接着判断按键的值是否在1到9之间,如果符合要求,就将按键值存储在一个4位寄存器中。同时,我们需要记录下当前输入的按键的个数,当输入4个按键后,就需要输入密码进行验证。

其次,在修改密码的部分中,首先需要输入当前密码进行验证,验证成功后,才可以进行密码的修改。如果修改成功,需要再次输入确认修改的按键。

最后,在开锁的部分中,需要输入正确的密码,才能够顺利开锁。

通过上述三个部分的设计,我们可以完成FPGA密码锁的整体框架。同时,在设计完成后,我们可以使用Quartus提供的仿真模块进行仿真测试。通过仿真测试,我们可以检查整个程序的正确性。

2、vivado的设计思路

在vivado的设计中,我们采用了更为高级的技术,使用了IP核技术。使用IP核技术可以将整个程序划分为多个模块,每个模块具有不同的功能,从而使得程序的结构更加清晰。具体实现如下:

首先,在输入部分,我们使用了矩阵键盘的IP核。该IP核可以识别按键值,并将其存储在一个FIFO缓存区中。

其次,在修改密码的部分,我们使用了先进的加密算法,以确保密码的安全性。

最后,在开锁的部分,我们同样使用了加密算法,保证了密码的安全性。

通过上述三个部分的设计,我们可以完成FPGA密码锁的整体框架。同时,在设计完成后,我们可以使用vivado提供的仿真模块进行仿真测试。通过仿真测试,我们可以检查整个程序的正确性。

三、仿真模块的设计与实现

在完成整个程序的设计之后,我们需要使用仿真模块对程序进行测试。在本工程中,我们选择使用Quartus中的ModelSim进行仿真测试,并在实现中搭配使用Quartus中的仿真波形分析功能。

在进行仿真测试时,我们需要注意以下几点:

1、首先,需要使用仿真模块测试每个部分的功能是否正常。包括输入部分、修改密码部分、开锁部分等。

2、其次,需要对整个程序进行综合仿真测试。也就是说,需要将整个程序连接在一起进行测试,确保在整个流程中程序协同工作的正常性。

3、最后,需要对程序进行较长时间的仿真测试,以确保程序的稳定性和可靠性。同时,需要对程序进行一定程度的优化,以提高程序的性能和速度。

四、总结

本文主要介绍了基于Verilog语言开发的FPGA密码锁工程的设计思路和实现方法。通过对Quartus和vivado两个版本的工程的介绍,我们可以看到,使用FPGA技术可以实现对密码锁的快速开发和部署,并且可以在保证密码锁安全性的同时,提高程序的性能和速度。同时,我们还介绍了仿真模块的设计和实现方法,以及需要注意的一些问题。

相关代码,程序地址:http://lanzouw.top/643325544397.html