热门标签

热门文章

- 1hadoop的三大核心组件之HDFS和YARN_hdfs yern

- 2【实体对齐·HGCN】Jointly Learning Entity and Relation Representations for Entity Alignment

- 3Linux系统简介_linux硬件设备由什么直接管理

- 4Git入门到精通(大全)_git从入门到精通

- 5软件测试只会“点点点”,凭什么让开发看的起你?_软件测试点点点

- 6echarts的简单使用_echarts简单使用

- 7Introduction to 3D Game Programming with DirectX 12 学习笔记之 --- 第七章:在Direct3D中绘制(二)_direct3d画圆

- 8HarmonyOS Next 使用Web获取相机拍照图片案例_onshowfileselector返回值

- 9用70行Python编写一个概率编程语言_pyro教材 概率编程

- 10自动化搞钱:7个最强免费AI工具,10倍速提升赚钱、超过99%的人_7個最強免費ai工具,10倍速提升賺錢、自媒體內容創作、工作效率,超過99%的人

当前位置: article > 正文

FPGA图像处理——cameralink发送设计实现之改进版_cameralink fpga oserdes

作者:煮酒与君饮 | 2024-07-24 05:01:29

赞

踩

cameralink fpga oserdes

摘要

本文延续上期文章对cameralink发送模块的设计探索。上期文章,用一般意义上的方法实现了速率为40Mhz/280Mhz 的图像数据传输,效果良好,这种方法由于将cameralink时钟信号一并以串行方式生成,可称之为“源同步”方式。然而这种方式下,对PCB的物理等长布线要求高,一旦改变硬件连接,可能造成部分数据失真。本文,将探究非源同步方式下的cameralink发送过程中时钟和数据的处理。这种情况下,采用时钟相位动态调整的方式,使得设计更具有灵活性。

1. 非源同步和源同步的区别

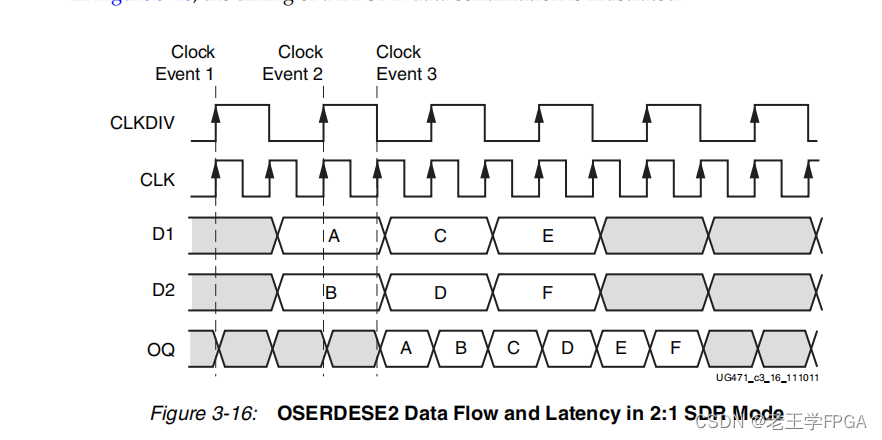

这里源同步是指数据和时钟边沿对齐同步发出,在没有外在物理延迟的情况下可以认为数据和时钟信号是同步对齐的。如下图所示,我们使用xilinx的OSERDES资源时,由于延迟的存在,其输出的串行数据和时钟边沿不是对齐的(延迟时间见下表)。

如果简单的将clk_div作为cameralink的xclk时钟,这样以来,采集卡通过cameralink接口接收到的时钟和串行数据存在相位偏差,采样时就会出现数据失真的情况。

如果这时我们将时钟信号也像数据信号一样经过OSERDES串行产生,这样的话时钟和数据信号之间具有相同的延迟,cameralink采集卡可以较为准确的接收到数据。

所以,上期的文章中,我们采用了将时钟信号一并串行生成的方式,实现了cameralink接口的正确传图。对时钟做的代码处理

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/煮酒与君饮/article/detail/873033

推荐阅读

相关标签