- 1ES9023音频解码芯片的工作原理_es9023解码电路图

- 2NECCS|全国大学生英语竞赛C类|听力|长对话|15:40~16:33_neccs常用词汇短语

- 3Linux下regex.h知识点和使用样例_

reg_extended - 4wpf圆角带进度显示ProgressBar样式_wpf progressbar样式

- 5【EAI 007】Mobile ALOHA:一个低成本的收集人类示教数据的双臂移动操作硬件系统_mobile aloha: learning bimanual mobile manipulatio

- 6rust-程序设计语言_rust程序设计

- 7『已解决』SecureCRT无法连接到CentOS虚拟机,没有出现输入用户名和密码的框框_电脑远程连接为什么没有出现输入用户名的空格

- 8如何在Genymotion虚拟设备上安装Google框架(Play,Accounts等)? [重复]_genymotion 安装gms

- 9【银行测试】支付类测试关注点与异常点+支付平台..._支付功能测试点

- 10git基本命令行操作_git 命令行操作

FPGA——1位全加器和4位全加器的实现_一位全加器电路图

赞

踩

一、认识全加器

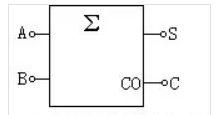

1、半加器

半加器是实现两个一位二进制数加法运算的器件。它具有两个输入端(被加数A和加数B)及输出端Y。

是数据输入被加数A、加数B,数据输出S和数(半加和)、进位C。

A和B是相加的两个数,S是半加和数,C是进位数。

所谓半加就是不考虑进位的加法,它的真值表如下 (见表):

逻辑表达式:

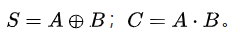

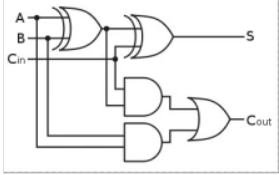

2、1位全加器

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

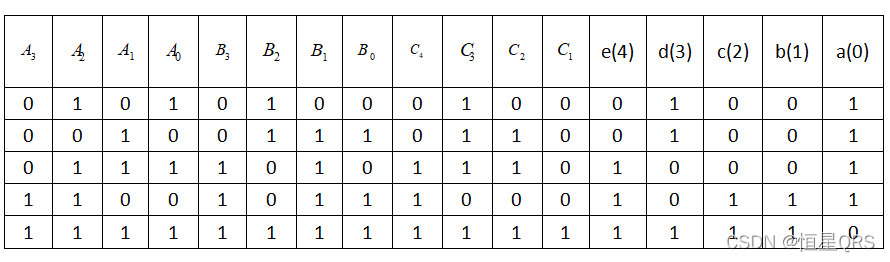

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci

3、4位全加器

四位全加器,是指能实现四位二进制数全加的数字电路模块。

2个四位输入以及1个一位进位,输出位一个四位数字加上1个一位进位。

二、使用原理图实现1位加法器

1、原理图实现半加器

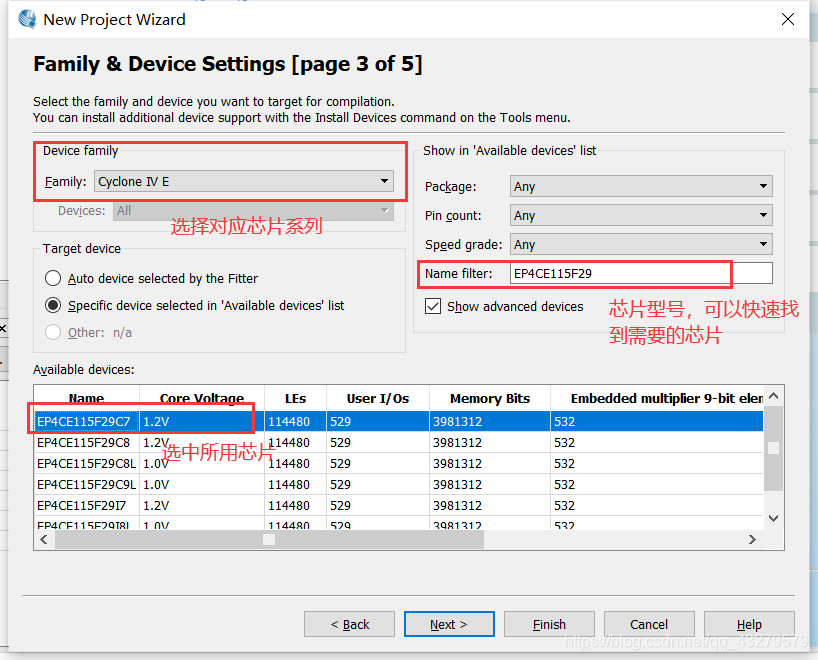

创建工程这里就不再赘述了,可以参考这篇博客:

https://blog.csdn.net/chenyu128/article/details/127835128

注意选择对所用的芯片型号:

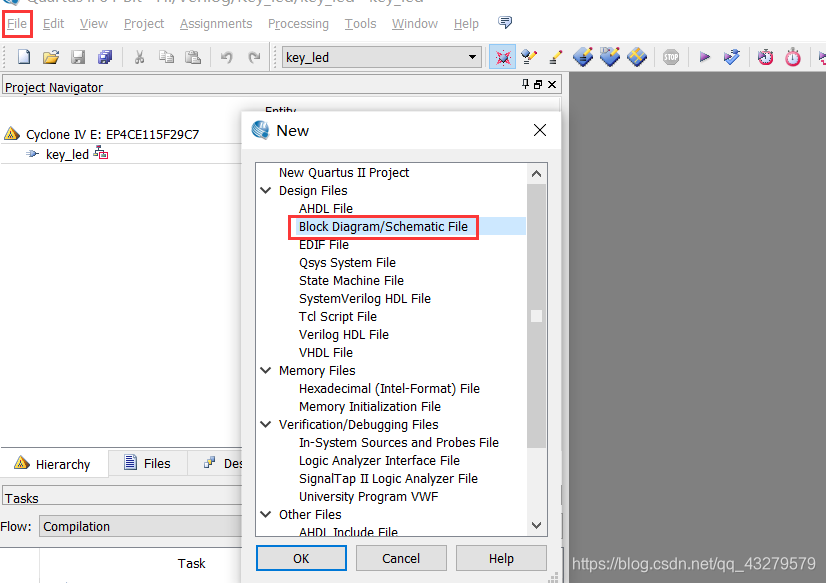

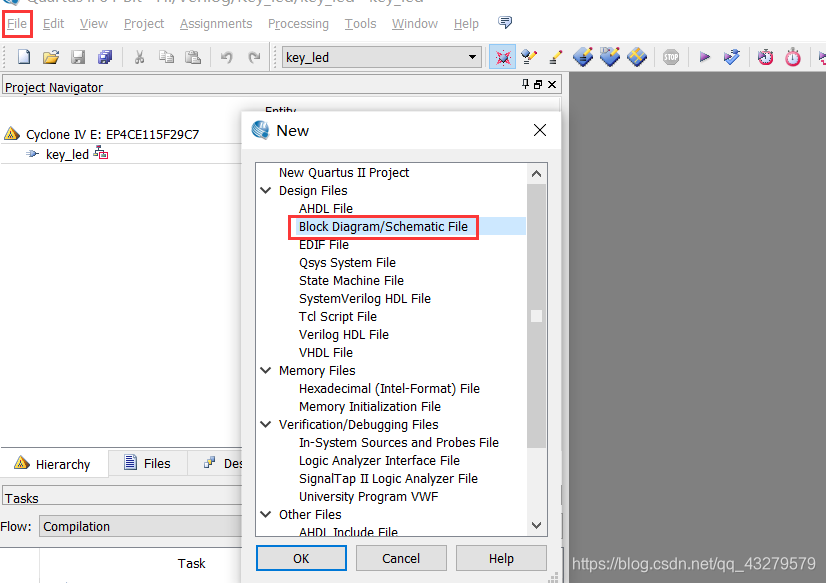

首先选择File->New,进入后选择Block Diagram/Schematic File

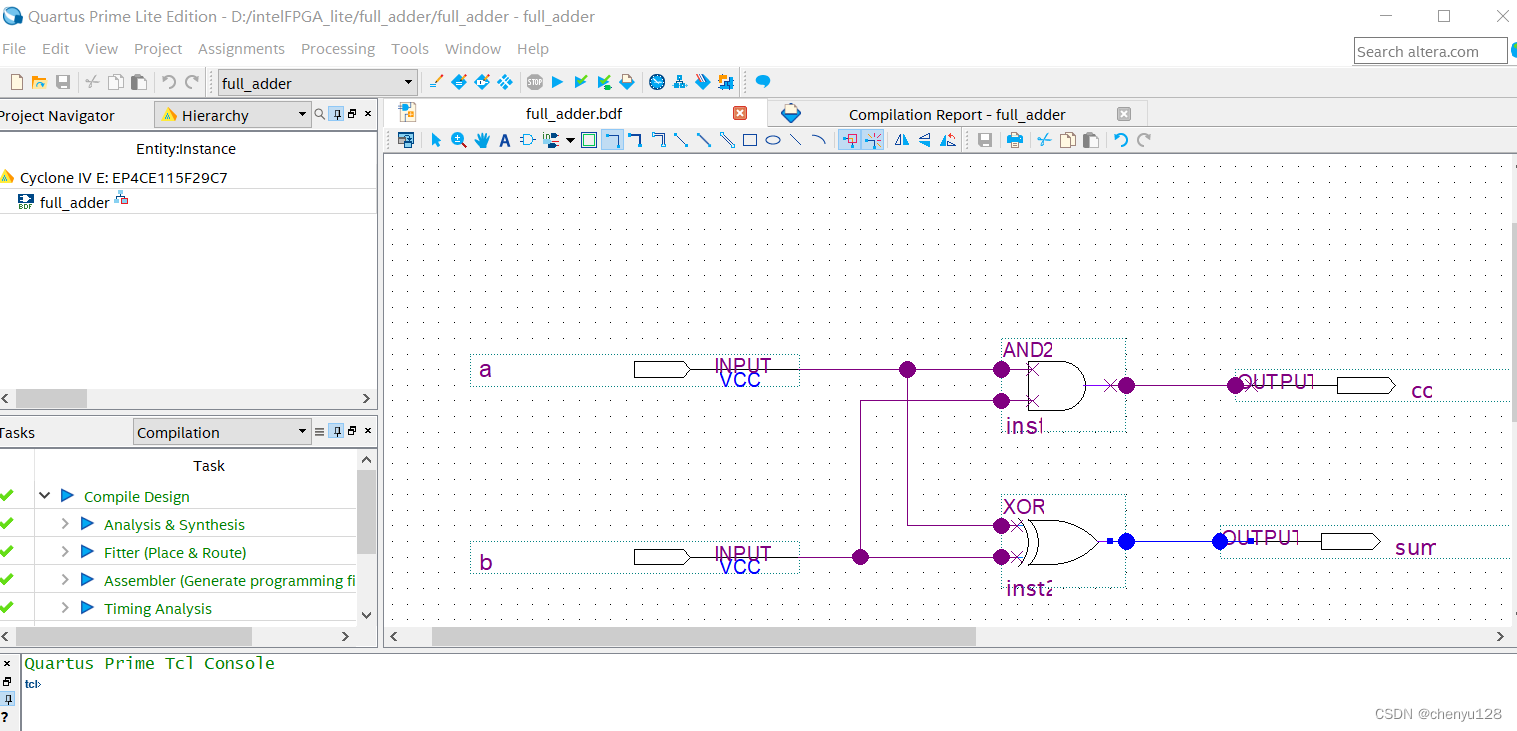

选择元件:两个输入,两个输出,一个与门,一个异或门

保存文件,并编译

通过tool->Netlist Viewers->RTL Viewer,查看电路图

仿真波形图

2、半加器元件实现全加器

将设计项目设置为可调用的元件

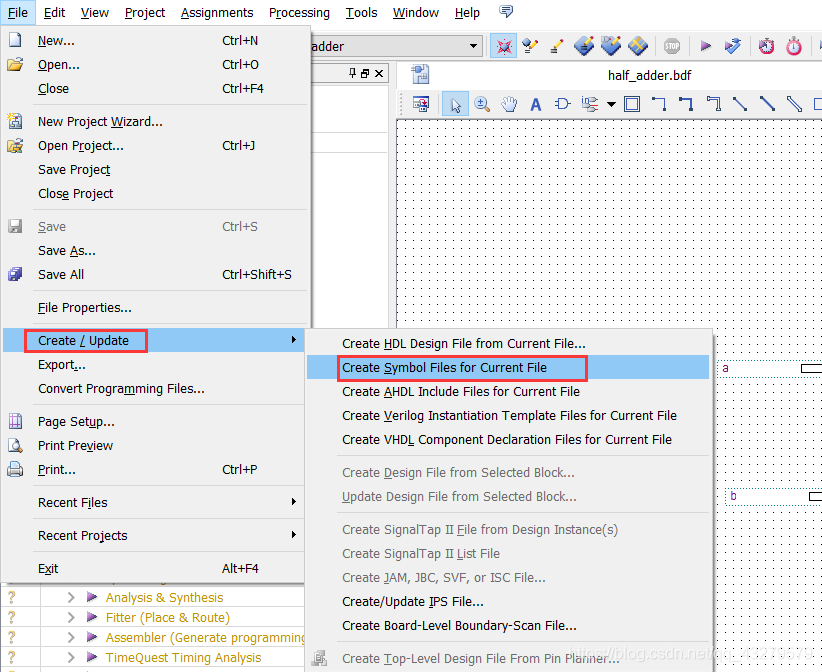

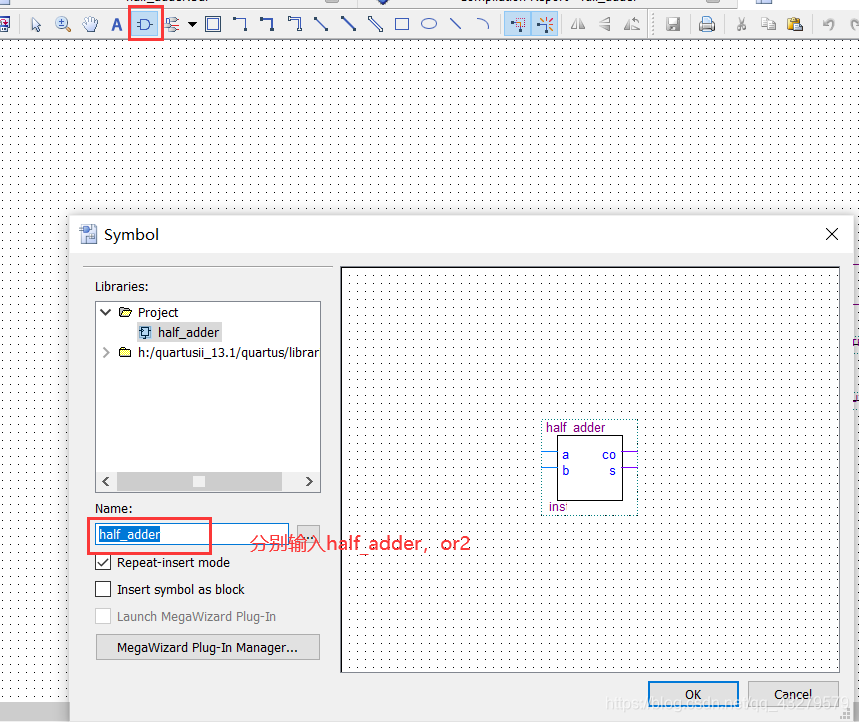

在打开半加器原理图文件half_adder.bdf的情况下,选择菜中File中的Create/Update→CreateSymbolFilesforCurrentFile项,即可将当前文件h_adder.bdf变成一个元件符号存盘,以待在高层次设计中调用

首先

选择File->New,进入后选择Block Diagram/Schematic File

选择元件:选择之前设置的半加器元件,三个输入,两个输出,再加上个或门

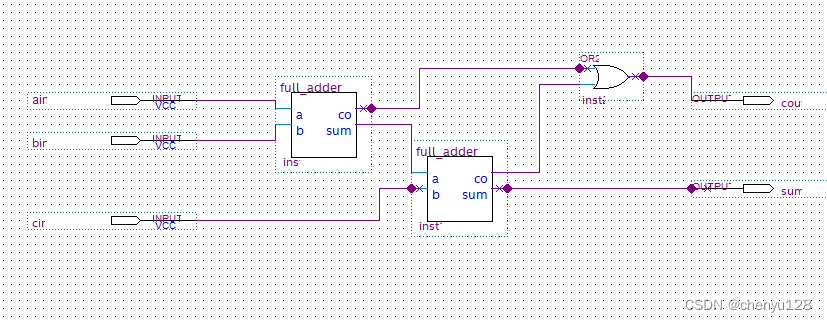

最终实现的效果图如下:

保存文件,并编译

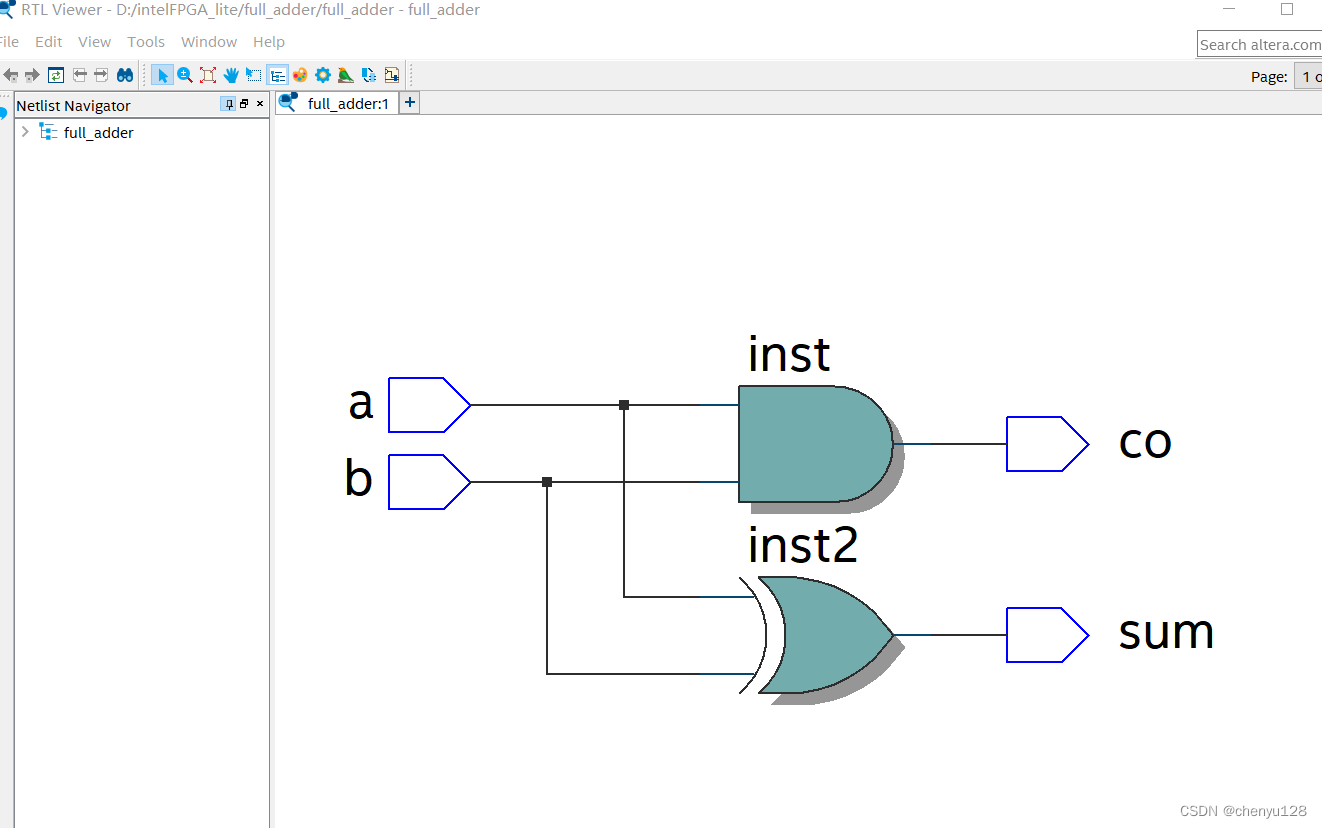

通过tool->Netlist Viewers->RTL Viewer,查看电路图

仿真实现

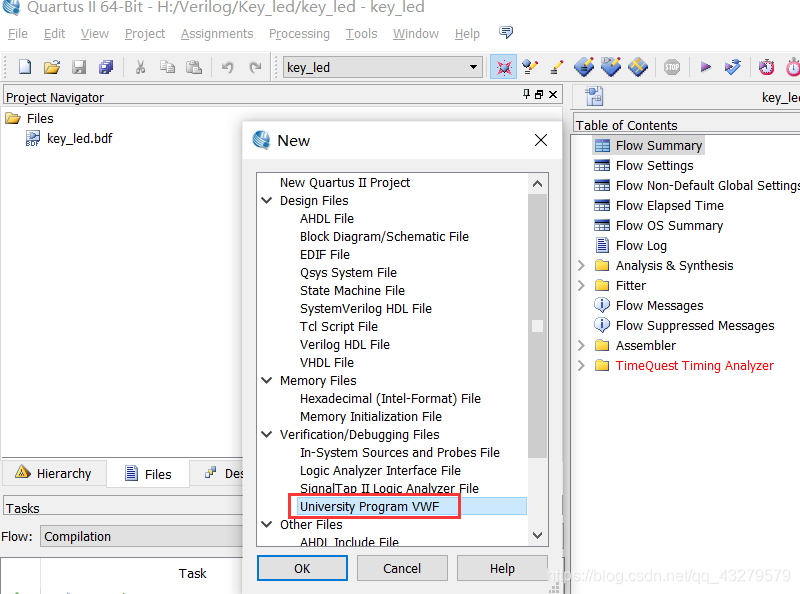

创建一个向量波形文件,选择菜单项 File→New->VWF

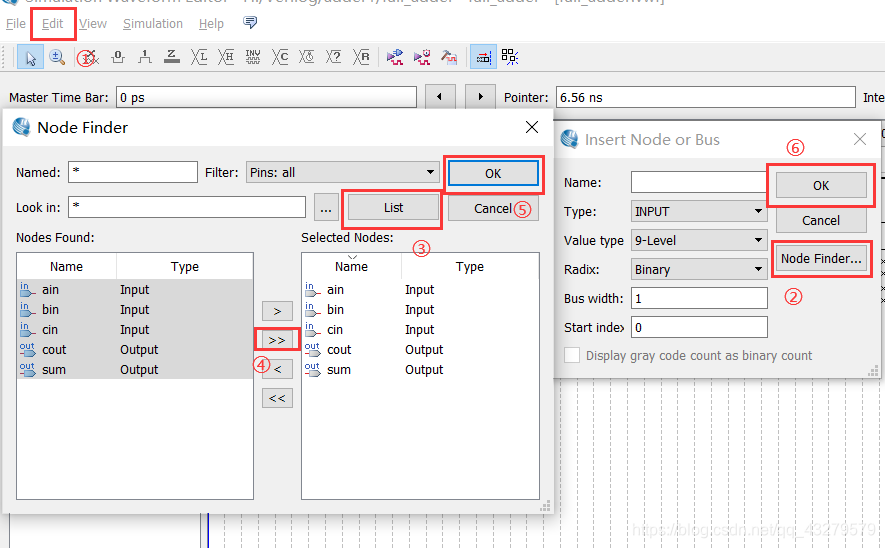

添加信号

随便设置输入信号的波形,然后点击功能仿真。

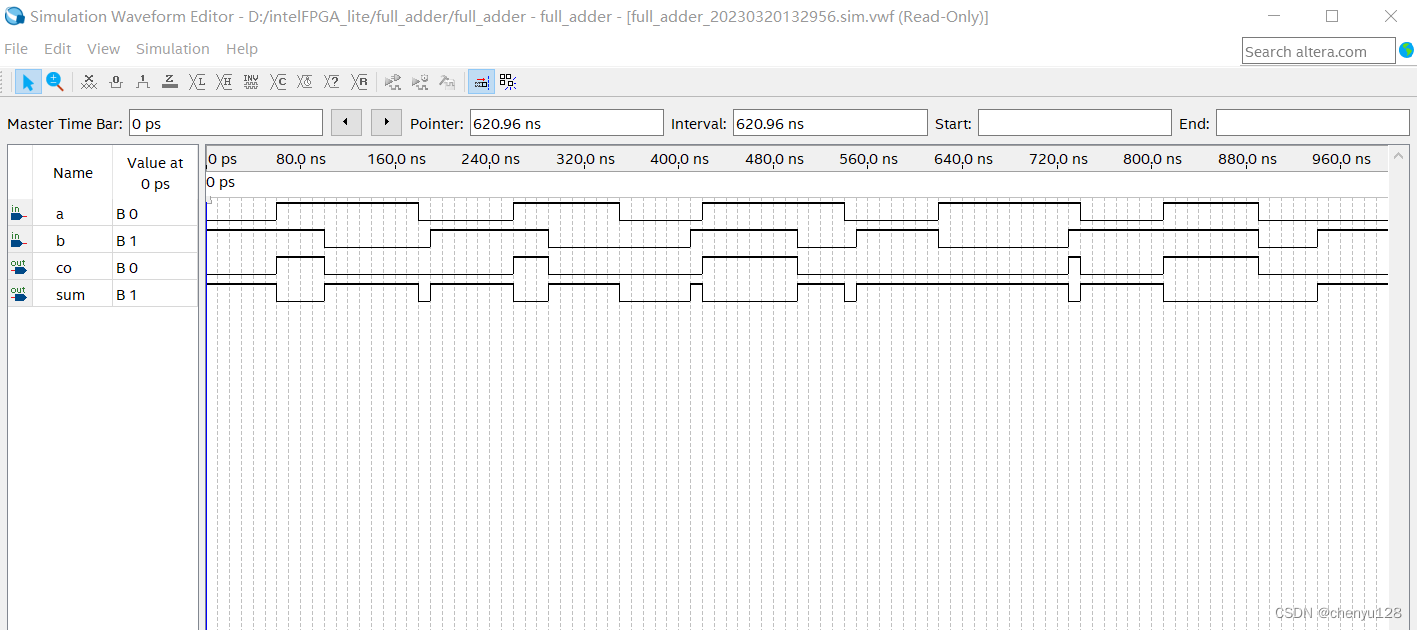

功能仿真结果

三、使用原理图实现4位加法器

四、Verilog HDL实现1位加法器和四位加法器

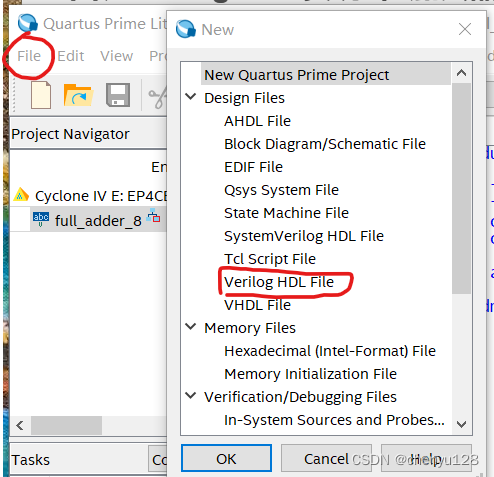

1、重新创建个项目文件,创建verilog HDL 文件

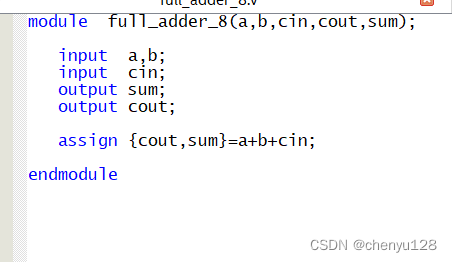

2、1位加法器代码

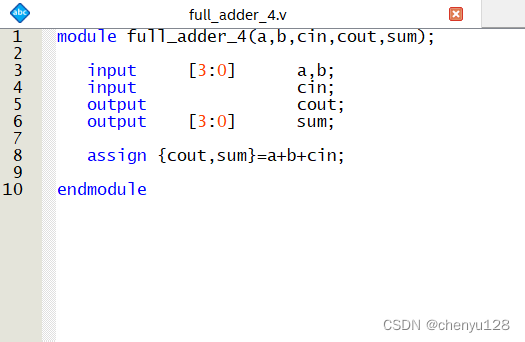

3、4位加法器代码

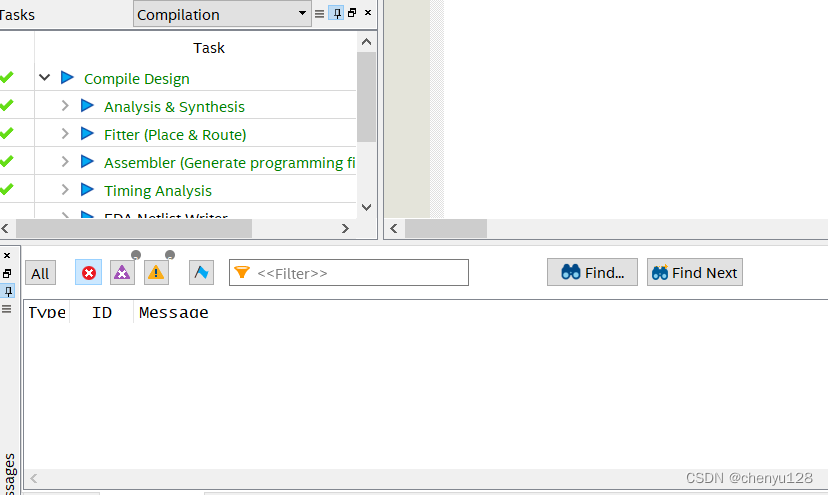

4、编译文件无错误并保存

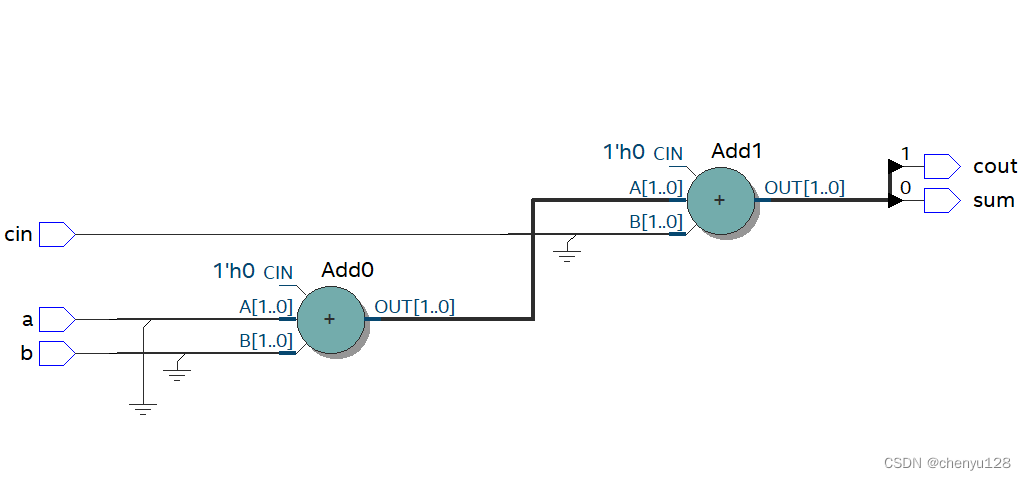

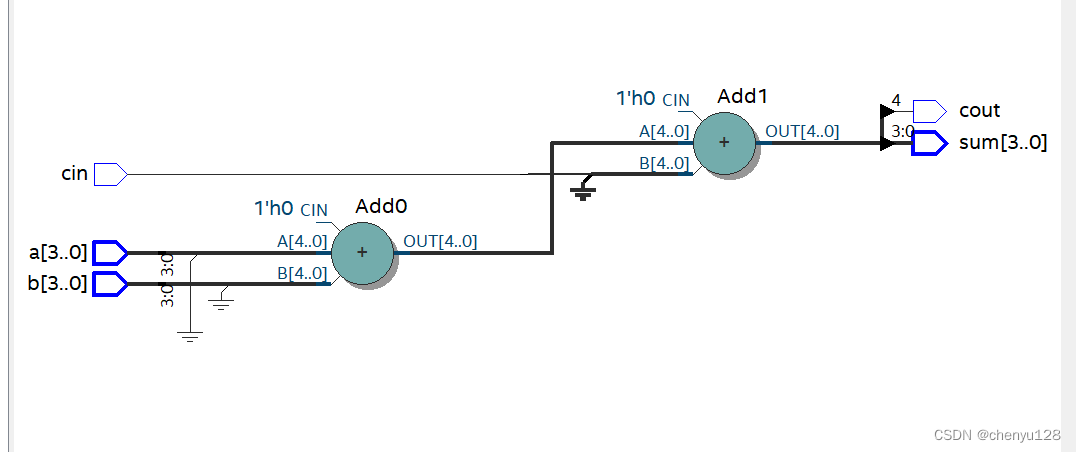

5、可以查看电路图

一位加法器的电路原理图:

4位加法器的电路原理图:

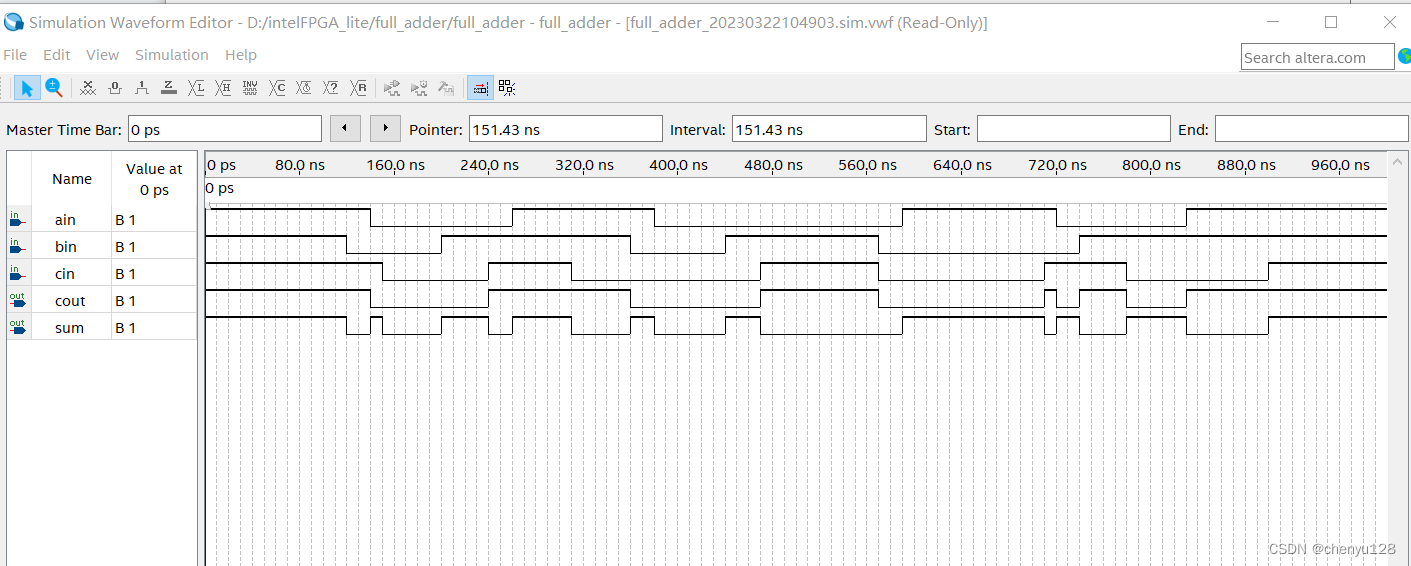

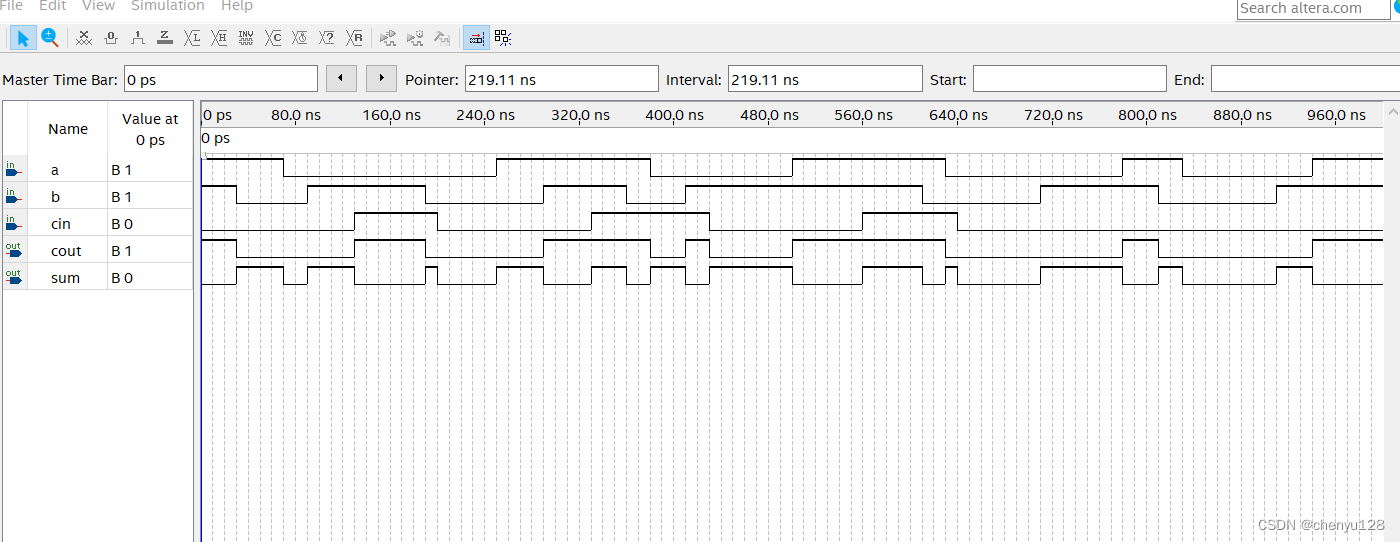

6、波形仿真

1位加法器的波形仿真图,高电平代表1,低电平代表0,可以看到,加法器正常工作无错误波形输出。

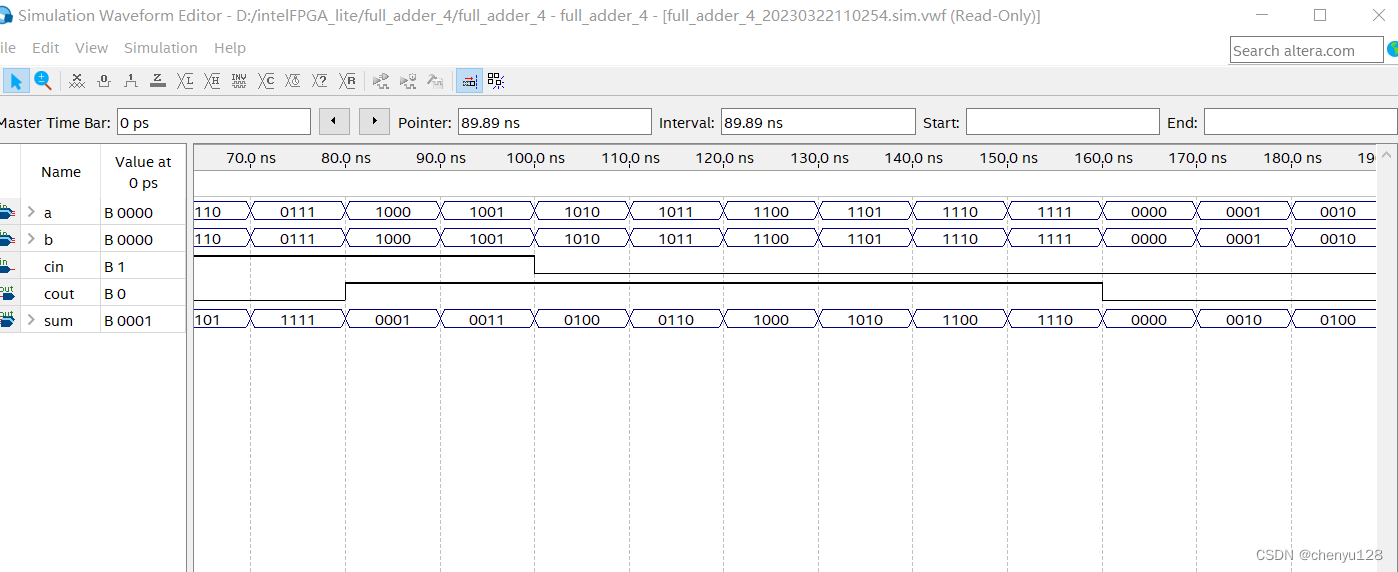

这是四位加法器的仿真波形图,这里使用4位的二进制数字来代表4位的输入信号和输出信号。

五、烧录及实验效果

1、

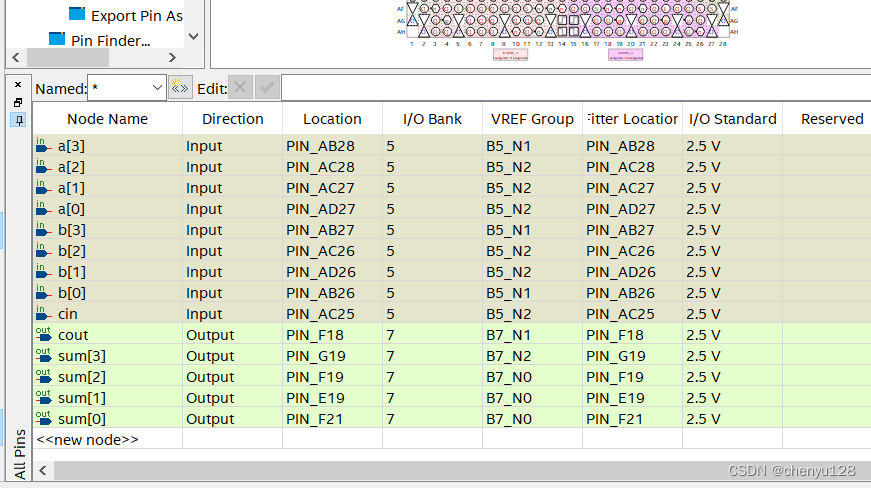

烧录前先要所需的绑定引脚

查询芯片引脚配置图:

将前八个拨片作为我们的2个四位信号输入,第9个拨片作为进位输入,拨片向上代表输入1信号,拨片向下代码输入0信号。

将前四个led作为四位加法器得到的加法sum和,第5个led灯则是进位。

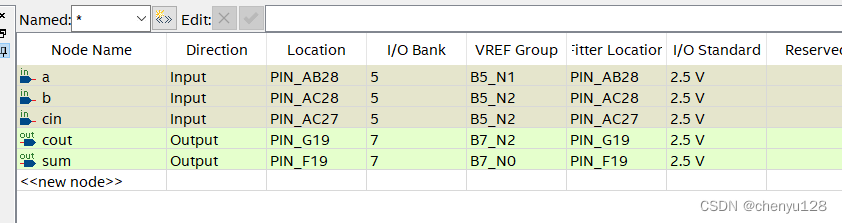

1位加法器的引脚绑定同理如下:

2、实际效果演示

1位加法器

4位加法器

六、总结

这次实验复习了之前学习的verilog语言和Quartus软件的使用,构建1位加法器和4位加法器用原理器件和直接用verilog语言,以及仿真看看是否构建成功。

七、参考链接

https://blog.csdn.net/qq_43279579/article/details/115480406