- 1Three.js Vue 如何加载字体,和遇到问题解决: 中加载字体的问题 Uncaught SyntaxError: Unexpected token = in JSON at position 0_threejs text3d 字体 不显示 vue3

- 2力扣45.跳跃游戏Ⅱ(贪心思路详解)_跳跃游戏 贪心

- 3Python dict字典全部操作方法_python dict操作

- 4linux kernel内存泄漏检测工具之kmemleak

- 52022-年终总结_年终总结 csdn 天津

- 6Flutter与Android混合编码配置笔记

- 7Python上海美食餐厅餐馆商家爬虫数据可视化分析和推荐查询系统 开题报告(1)

- 8不容错过,前端 Code Review 的最佳实践方案来了

- 9CCleaner2024win电脑专用系统垃圾清理与优化工具

- 10【数据结构】纯c语言双向链表_c语言 双向链表

PCIe转28串口8串口CH384设计注意事项

赞

踩

PCI-Express总线转多串口扩展芯片CH864,由于波特率高、外围电路简单、设计到出产周期短、支持平台广泛等,广泛用于工业制造、安防监控、商超结算、教学演示、大屏显示等需多串口的场合。

CH384单芯片包含四个兼容16C550/16C750的异步串口和一个EPP/ECP增强型双向并口,如外加CH438可扩展达28串口。本文将从CH384与PCIe引脚的连接、PCIe原理图设计和PCIe端PCB设计这3方面来分别介绍使用设计中的注意事项:

一、CH384与PCIe引脚的连接

| PCIe Pin Name | PCIe Pin# | CH384 Pin Name | CH384 Pin# |

| PETp0 | 14 | PERP | 18 |

| PETn0 | 15 | PERN | 19 |

| PERp0 | 21(A16) | PETP(+104电容) | 22 |

| PERn0 | 20(A17) | PETN(+104电容) | 21 |

| PEFCLK+ | 24(A13) | PECKP | 11 |

| PEFCLK- | 23(A14) | PECKN | 12 |

注:

- 表中只介绍了CH384和PCIe直接的引脚对接,如使用MiniPCIe或ExpressCard等接口转多串口,请参考《PCI-Express、MiniPCIe、ExpressCard接口转换说明/引脚互换关系》

- 如需配置不同的串口并口模式,请参考《PCI-Express转4串/8串/28串口CH384的硬件配置及设计》

二、PCIe信号设计

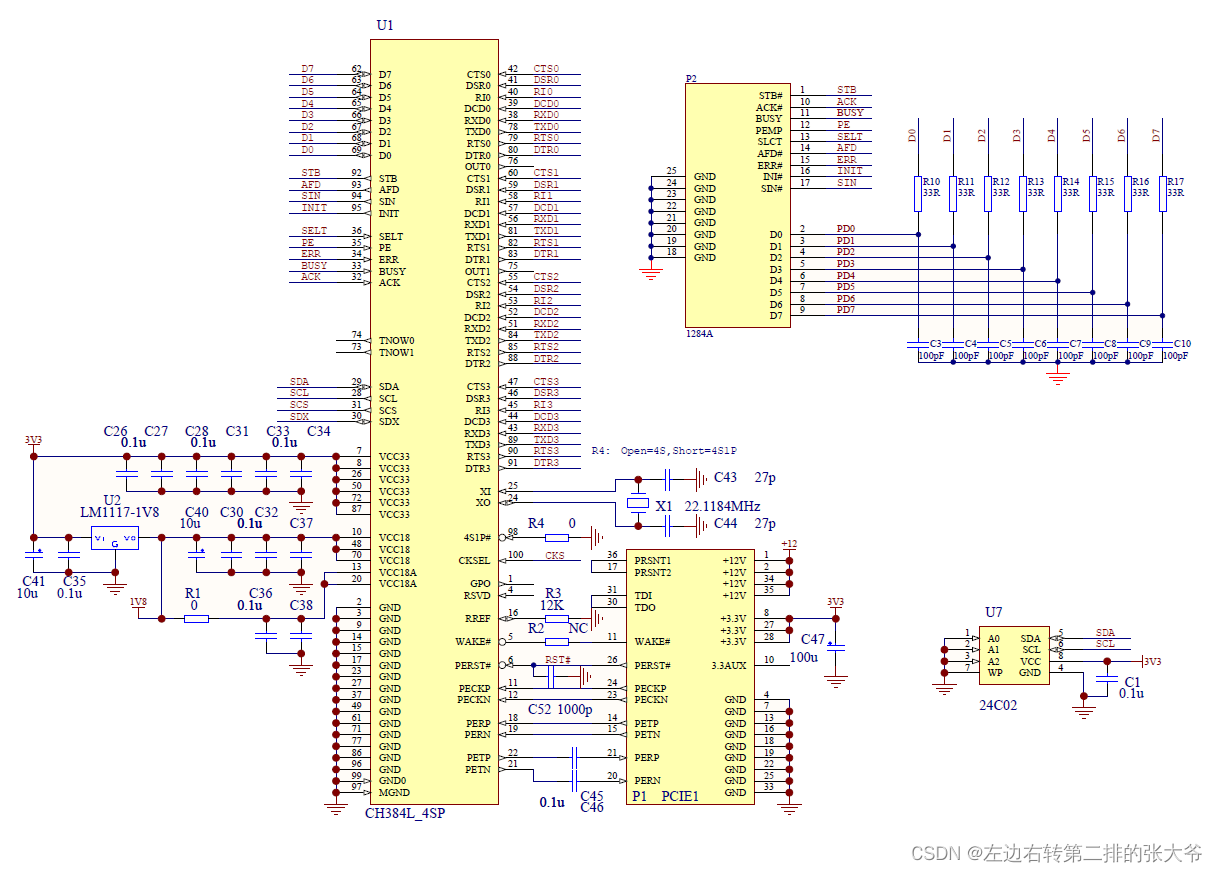

以CH384芯片的PCIe转四串口+并口/打印口的基本电路为例,U7是可选的EEPROM外部配置芯片,可设定PCIE板卡的设备标识(Vendor ID,Device ID,Class Code 等)。IEEE1284 要求打印口信号保持阻抗匹配,所以,打印口并行数据线可能需要串联电阻和并联电容,在要求不高时也可以省掉。晶体X1和电容C43、C44 用于时钟振荡电路。其它电容用于电源退耦,容量为10uF的电容是钽电容,容量为0.1uF的电容是独石或者高频瓷片电容,分别就近并联在CH384的电源引脚上。

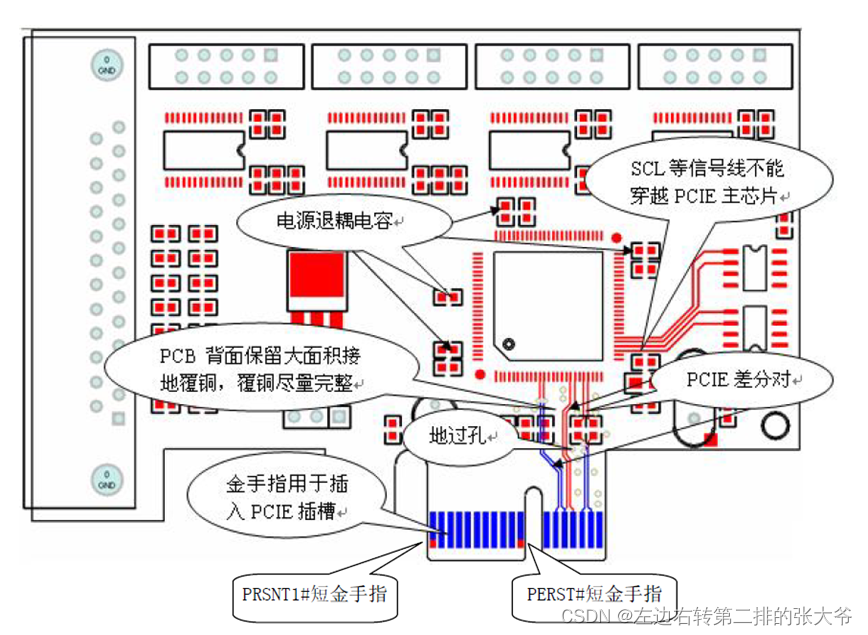

三、PCB设计注意事项

CH384 属于高频电路,传送线在信号线上驱动电压变化时会出现阻抗,信号线的宽度和到接地的距离都会影响阻抗,所以在设计PCB时需要参考PCIE总线规范来注意阻抗匹配,以下为一些注意事项:

- 金手指边缘到PCIE芯片管脚的走线长度应小于100mm毫米;

- PCIE的三对差分线PERP/N(2.5GHz),PETP/N(2.5GHz),PECKP/N(100MHz):差分对线的两条需同步布线,长度差值应小于5mil,如两条走线同步转弯且使用弧线或者钝角转弯;

- 布差分对线尽量避免VIA过孔,如一定要过孔换层,那么同步过孔且靠近孔处放GND地信号过孔;

- 差分对线PCB线宽建议是7mil,两条走线的净间距建议是7mil;

- 两对差分对线之间的距离、差分对线和其它非PCIE信号的距离,建议大于20mil,且之间用GND隔离;

- PCIE信号线的PCB反面避免走高频信号线,最好全GND铺铜;

- 0.1uF的高频退耦电容放置在电源引脚附近;

- PCIE芯片的PERST#引脚与GND间跨接1000pF贴片电容。

布线示例如图:

以上就是CH384与PCIe引脚的连接、PCIe原理图和PCB设计中的注意事项,使用中,如需高波特率或非标波特率,可参考《PCIe转多串口CH382/CH384时钟和波特率、分频与倍频》