- 1Spring源码分析-BeanDefinition_spring源码系列之beandefinition

- 2Mac 解决配置 zsh 后,nvm不见的问题

- 3苹果微信分身双开怎么弄?2024最新苹果微信分身下载教程!

- 4AI代码生成助手Cursor、TabNine 、Cosy使用体验_cursor是基于chargbt的吗

- 5四、Hybrid_astar.py文件中Hybrid A * 算法程序的详细介绍

- 6微信小程序电子签名及图片生成_电子签名小程序

- 7腾讯云认证FAQ | 热门考试方向、考试报名流程、模拟试题等_腾讯云运维工程师认证

- 8Sublime text3 Version 3.22下载安装及注册_sublime 322 注册

- 9详解Python对Excel处理_python能处理xls文件吗

- 10《Flink原理、实战与性能优化》(Flink知识梳理一)

Xilinx 7系列 FPGA硬件知识系列(九)——FPGA的配置_xilinx pudc

赞

踩

1.3 端口配置

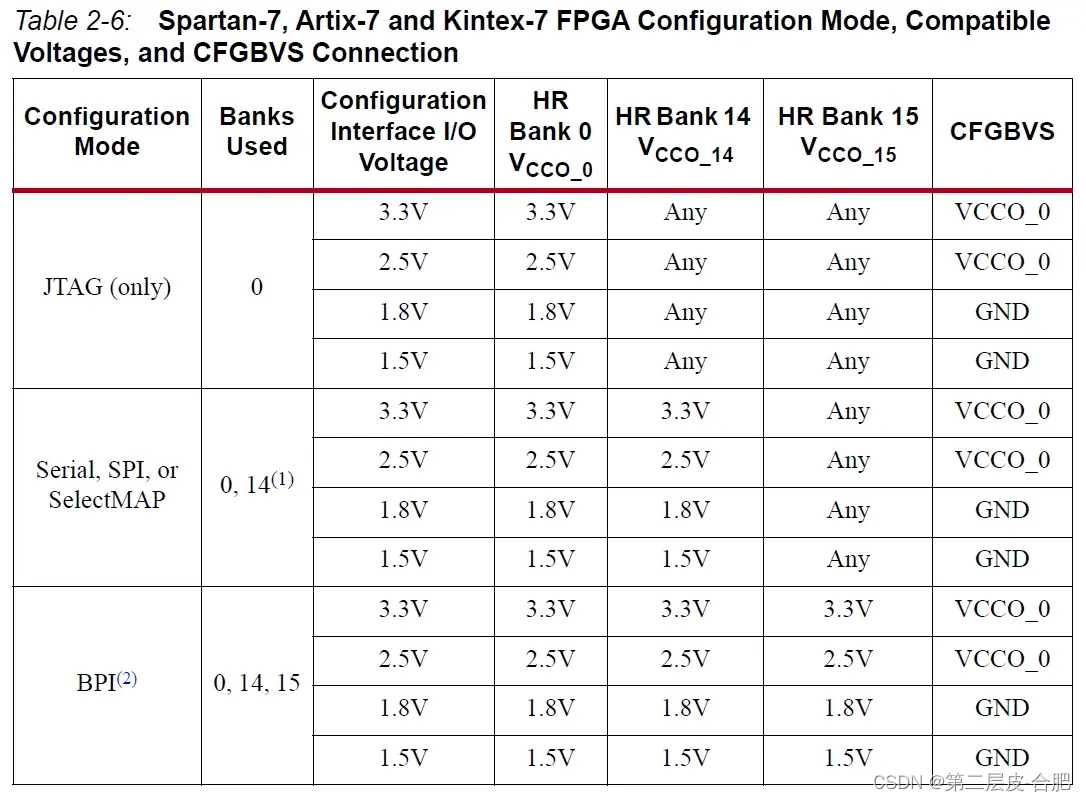

每组配置模式都有一组特定的接口管脚,它们跨越7系列FPGA上的一个或多个I/O BANK。7系列器件支持3.3V、2.5V、1.8V或1.5V的I/O配置,包括:

BANK 0 中的JTAG管脚、BANK0中的专用配置管脚

BANK14和BANK15中与特定配置模式相关的管脚

I/O电压配置由CFGBVS(配置组电压选择引脚)确定:

当CFGBVS为GND,并且配置模式使用到BANK14/15时,VCCO_0、VCCO_14和VCCO_15必须为1.8/1.5V以避免器件损坏。具体的配置关系如下:

在Virtex‑7 FPGA中,BANK14和BANK15是高性能BANK,仅限于1.8V或更低的I/O标准,Virtex‑7 HT器件仅支持BANK0的1.8V操作。

所有专用输入引脚都在VCCO_0为LVCMOS电压电平(LVCMOS18、LVCMOS25或LVCMOS33)下工作。所有有源专用输出引脚均在VCCO_0电压电平下工作,输出标准设置为LVCMOS、12mA驱动、快速摆率。

一般来说专用引脚除了电平外不需要额外进行配置

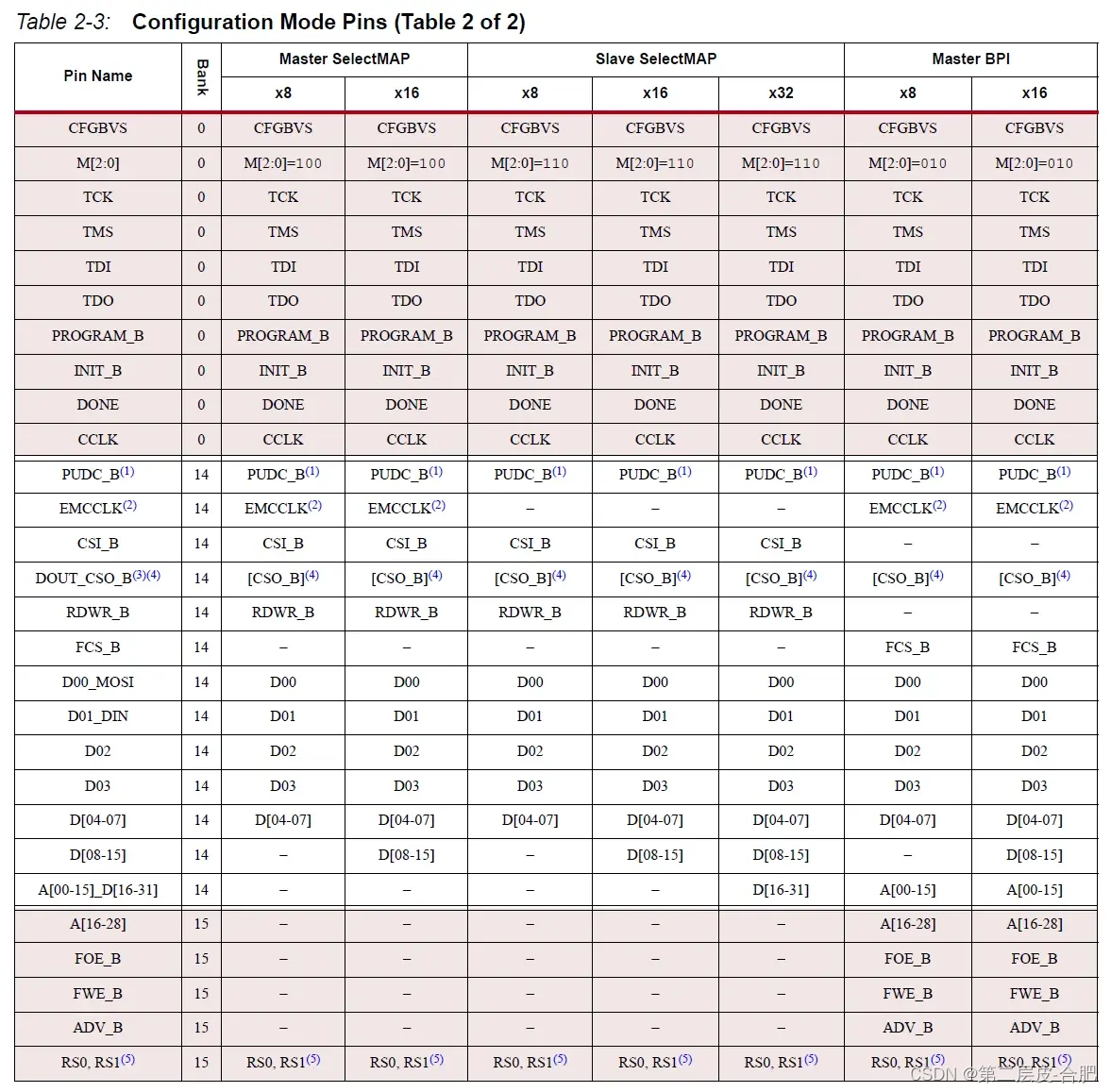

具体的配置模式所对应的管脚如下:

在进行电路板设计时,需要严格对照管脚映射,否则会导致配置失败。

注意事项:

1. PUDC_B在配置过程中具有特殊功能,它独立于所有配置接口,不需要与配置接口中其他引脚电压兼容。

2. 仅当 BitGen ExtMasterCclk_en 选项启用 EMCCLK 作为主配置模式时钟的输入时,才使用 EMCCLK。

3. DOUT 仅用于串行配置菊花链,用于将数据输出到下游 FPGA(或 用于 BitGen 调试比特流 选项)。否则,DOUT 是高阻状态。

4. CSO_B仅用于并联配置菊花链,用于将芯片使能信号输出到下游设备。否则,CSO_B为高阻状态。

5. RS0 和 RS1 仅在启动多重引导事件或启用 BitGen 配置回退选项并发生回退事件时驱动。否则,RS0 和 RS1是高阻状态。使用 RS[1:0]引脚进行配置时,建议不要在用户模式下使用它们。

6. 空单元格表示引脚在配置模式下未使用,在配置过程中被忽略且为高阻。

1.3.1 PROGRAM_B引脚

低电平有效。当PROGRAM_B脉冲为低电平时,FPGA配置被清除并启动新的配置序列。配置复位在下降沿启动,配置(即编程)序列在下一个上升沿开始。

在上电时将PROGRAM_B保持为低电平不会使FPGA配置保持在复位状态。相反,使用INIT_B来延迟上电配置序列。

1.3.2 INIT_B引脚

低电平有效。当FPGA处于配置复位状态、FPGA正在初始化(清除)其配置存储器或FPGA检测到配置错误时,FPGA将该引脚驱动为低电平。

完成FPGA初始化过程后,INIT_B被释放到高阻态,此时外部电阻器应将INIT_B拉高(将INIT_B连接到一个 的上拉电阻到VCCO_0)。当初始化过程完成后在INIT_B输入检测到高电平时,FPGA继续执行由M[2:0]引脚设置指示的配置序列的其余部分。

1.3.3 DONE引脚

高电平有效。DONE引脚上的高电平信号表示配置序列完成。DONE输出默认为开漏输出。