- 1【数据结构】二叉树-堆(下)-链式二叉树

- 2队列的基本操作(C语言链表实现)初始化,入队,出队,销毁,读取数据_请写出初始化队列、销毁队列,入队,出队、判队空、显示队列中的所有元素算法。 voi

- 3谷歌一雪前耻,全新PaLM 2反超GPT-4,办公全家桶炸裂升级,Bard史诗进化_medpalm github

- 4ZYNQ ZCU102视频编码开发_zynq 视频硬编码

- 5Verilog实现正弦电压PWM波生成 嵌入式_verilog pwm发生器

- 6nginx报错:nginx: [emerg] the “ssl“ parameter requires ngx_http_ssl_module in /project/api/nginx.conf:_nginx的[emerg] 53886

- 7Java8新特性——Stream API_java8有streamapi吗

- 8数据结构学习笔记(4)——数组、矩阵与广义表_伪地址法表示稀疏矩阵

- 9软件测试面试题_软件测试测试用例面试题

- 10java opencv配置_java 项目 amd 配置opencv

基于FPGA的高性能硬件EtherCAT主站研究_ethercat fpga

赞

踩

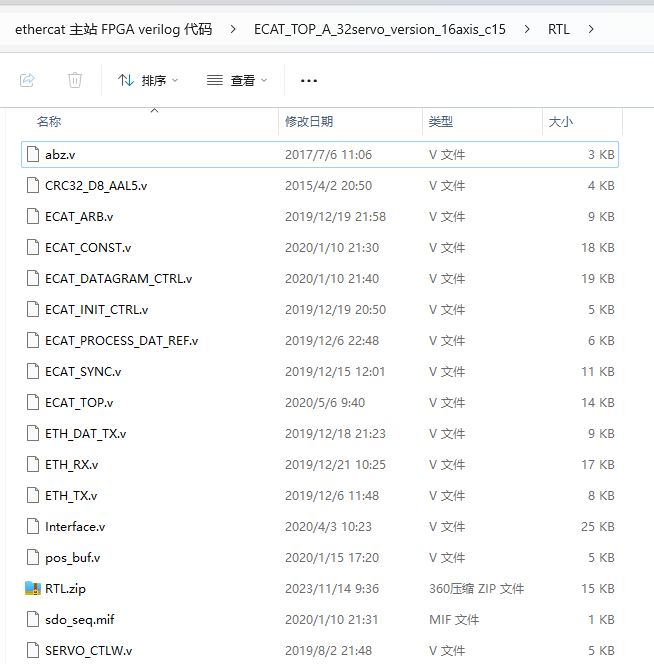

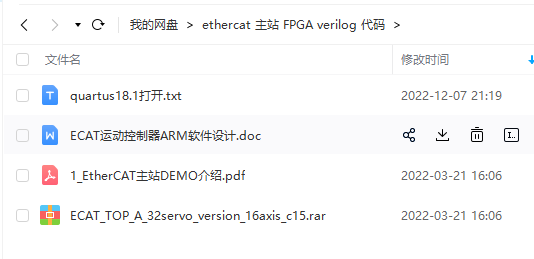

一份EtherCAT主站的FPGA Verilog代码

ethercat 主站 FPGA verilog 代码

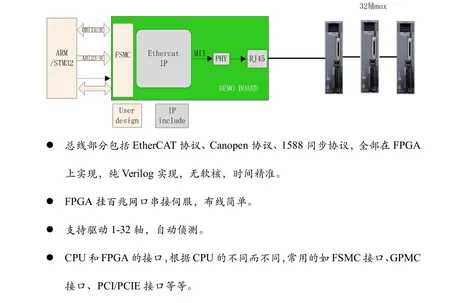

使用FPGA逻辑实现EtherCAT协议,实现主站DC功能。更加突出了EtherCAT现场总线的同步性能及高效性

基于FPGA的EtherCAT主站设计研究

基于FPGA的EtherCAT主站方案

基于FPGA的EtherCAT主站研究

一种基于FPGA实现的EtherCAT主站运动控制器的制作方法

基于FPGA的EtherCAT主站实现与高性能运动控制

基于FPGA的高性能硬件EtherCAT主站研究

基于FPGA的高性能硬件EtherCAT主站研究

摘要:

本文基于FPGA技术,研究并设计了一种高性能硬件EtherCAT主站。通过使用Verilog语言编写代码,实现了主站的数据通信和控制功能。该主站采用了EtherCAT协议,突出了现场总线的同步性能及高效性。本研究旨在提供一种基于FPGA的EtherCAT主站解决方案,为实时运动控制系统提供可靠的通信和控制支持。

1. 引言

EtherCAT(Ethernet for Control Automation Technology)是一种高性能的实时以太网通信协议,适用于工业自动化领域。随着工业自动化的发展,EtherCAT协议得到了广泛应用,并且在实时性、同步性和扩展性方面具有显著优势。本研究旨在使用FPGA技术实现一个高性能的硬件EtherCAT主站,以满足实时运动控制系统的通信和控制需求。

2. FPGA实现EtherCAT主站的设计与原理

2.1 EtherCAT通信协议

EtherCAT协议基于Ethernet技术,采用主从结构,支持多个从站设备连接到一个主站设备。主站负责发送控制指令和接收数据,从站设备负责执行指令并返回数据。EtherCAT协议的主要特点包括实时性、同步性和高效性。

2.2 FPGA设计原理

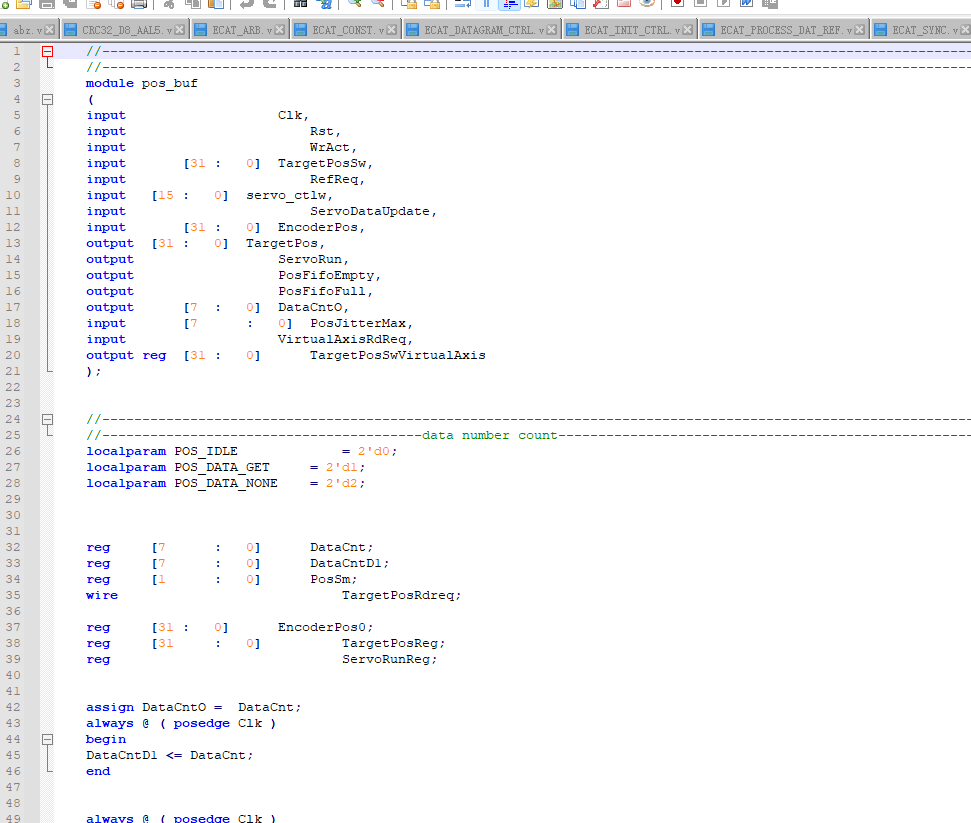

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据需要配置成不同的数字电路。在本研究中,我们使用Verilog语言编写FPGA的逻辑代码,实现EtherCAT主站的功能。Verilog代码包括各种模块,如Ethernet物理层接口、数据处理模块、控制模块等。

3. 硬件EtherCAT主站的实现与测试

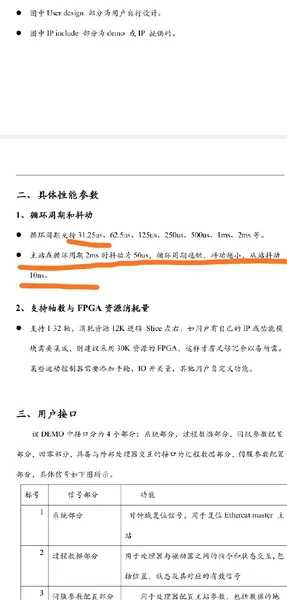

基于FPGA的EtherCAT主站的实现过程主要包括如下几个步骤:设计FPGA的逻辑电路、编写Verilog代码、进行逻辑仿真和测试、进行硬件验证和性能测试等。本研究使用一种基于FPGA的EtherCAT主站运动控制器的制作方法,通过实验验证了该方法的可行性和性能。

4. 硬件EtherCAT主站的性能分析

在性能分析方面,本研究主要从以下几个方面进行了评估:实时性、同步性和数据传输效率。实验结果表明,基于FPGA的EtherCAT主站在实时性和同步性方面表现出色,并且能够实现高效的数据传输。

5. 结论

本研究使用FPGA技术实现了一种高性能的硬件EtherCAT主站,突出了EtherCAT现场总线的同步性能及高效性。该主站具有实时性、同步性和高效性等优势,在工业自动化领域有着广泛的应用前景。本研究为实时运动控制系统提供了一种可靠的通信和控制解决方案。

相关代码,程序地址:http://lanzoup.cn/652098268519.html