- 1YOLOv8 更换骨干网络之 MobileNetV3:轻量级目标检测的新热点_yolov8 mobilenetv3

- 2Java项目入门开发实战_本关任务:用bootstrap实现pc端的博客头部效果

- 3Windows 如何删除右键菜单中的 “Git Gui Here”和“Git Bash Here”_windows右键菜单删除git

- 4区块链的公有链、私有链、联盟链_私链 人员和节点自由进出

- 5玫瑰编程--python_玫瑰花代码

- 6介绍一个成功的 Git 分支模型_功能分支开发模型

- 7【超详细】Jmeter安装配置详细教程_jmeter安装详细教程

- 8硬件描述语言(HDL)基础——基本结构_本关任务:请参考下图,声明必要的内部信号,采用持续赋值语句assign完成电路的建模

- 9在eclipse中用git导入工程问题:cannot open git-upload-pack_sts拉代码报错cannot open git-upload-pack

- 10SLA 是什么?如何实现 SLA 管理_互联网sla

PCIe-403信号处理模块VU_xcvu13p原理图

赞

踩

UD PCIe-403信号处理模块为标准PCIe全高的结构,对外支持PCIe3.0×16通信,也可以采用千兆以太网、万兆以太网接口进行通信,支持多板级联,支持XCVU5P、XCVU7P、XCVU9P、XCVU13P、XCVU190 FPGA。板载两组DDR4的存储器,位宽为64bit,分别容量为4GByte。板载有1个FMC+(兼容FMC子板)全互联的接口,满足VITA57.1和VITA57.4规范,可以适配大多数ADC/DAC FMC或FMC+子卡。全部器件选择工业级和以上质量等级元器件。

应用行业:

-

- 通信、卫星、雷达、视频图像等信号处理

- 数据采集存储、波形生成与回放

- 级联信号处理、多路万兆以太网/光纤分发

- 高速瞬态脉冲处理、测控仪器、软件无线电

- 高性能计算、服务器硬件加速、算法验证平台、Net FPGA

产品特点:

-

- PCIe接口:PCIe3.0×16

- FPGA:可选配XCVU5P、XCVU7P、XCVU9P、XCVU13P、XCVU190 FPGA

- FMC+ HPC,24路GTX,LA、HA、HB都全互联,可适配各种FMC AD/DA卡

- 支持JESD204C

- 单电源+6V~+12V供电,支持插入标准服务器或单独千兆、万兆网口使用

- 板载GPS/BD模块,也支持IRIG-B码时统输入

- 提供接口测试程序,专业团队提供技术支持

- 使用维护说明书详实,方便用户二次开发

- 质量可靠,成熟应用,批量出货,高性价比

UD PCIe-403产品原理框图:

主要技术参数:

产品配置:

- PCIe3.0×16配置,带宽≥10GB/s

- FPGA: XCVU5P-2I、XCVU7P-2I、XCVU9P-2I、XCVU13P-2I可选配

- 2组独立DDR4: 72bit位宽,速率2400Mb/s,4GB、8GB可选配

- GPS/BD定位:中科微电子,带秒脉冲

- 2组4路光纤:QSFP+,支持UDP/IP、TCP/IP、RapidIO、Aurora协议,速率≥12.5Gbps,可用于多板级联

- 温度监控:贴片GX18B20,可以检测PCB板、环境或散热片温度

- 电压监控:FPGA自带电压监控功能

- 板载晶振:50MHz±10ppm

- LED灯:电源指示灯1颗,状态指示灯8颗

- 支持外触发、外时钟功能

FMC功能扩展:

- 标准FMC+连接器,兼容FMC接口,满足VITA57.1、VITA57.4规范

- GTX:24路连接到FPGA速率≥15Gbps,更高速率请沟通

- 注意:80对LVDS的的电平,均为同一电平标准VADJ,默认电平1.8V

对外接口:

- GPIO口:分3组各8路,共34路,支持3.3V或5V,速率最高40MHz

- RS232口:2路标准RS232电平,速率最高120Kbps

- RS422口:1路全双工,速率最高12Mbps,兼容RS485电平

- RS485口:2路半双工,速率最高12Mbps,兼容RS422电平

- 千兆网口:1路,RJ45连接器, 支持10M/100M/1000M BASE-T

- 万兆网口:2组4路,QSFP+连接器,支持UDP/TCP、RapidIO、Aurora协议

- 互联接口:通过8通道光纤接口互联

- 外触发接口:SMA,外接信号经过滞回比较器后再到FPGA,3.3V或5V电平

- 外时钟接口:SMA,外接信号直接到FPGA的全局时钟管脚,单端3.3V电平

- 外接电源口:直流+6V~+12V,

- 输出电源:支持输出(500mA电流)+12V或+5V或+3.3V供外接天线使用

- JTAG接口:支持2.0间接双排14芯IDC连接器连接到下载器

其它特性:

- PCB 板尺寸:111.15mm ×224.66mm

- DC +6V~+12V(±5%),功耗25W~95W(根据FPGA的频率和使用资源消耗)

- 工作温度:‐20~+70℃、‐40~+85℃可选

测试程序:

- FPGA的所有管脚已例化

- FPGA读写DDR4、RS232/485/422/GPIO接口回环、PCIe接口识别到卡、获取GX18B20温度、接收GPS/BD模块数据、千兆以太网络PHY与计算机联通、光纤接口测试、LED跑马灯等

随货文档:

- 模块用户手册(含硬件及软件说明、模块结构及散热注意说明)

- 产品出货:模块1张(带FPGA散热片)、配套连接器(不带线,不含光模块)

- 合格证、测试(试验)报告

FPGA资源对比表参考:

| FPGA 资源对比表 | 7V690T | KU115T | VU9P | VU13P |

| Programmable Logic Cells | 693.12K | 1451.1K | 2586K | 3780K |

| RAM (# 36 Kb Blocks) | 52.92Mb | 75.9Mb | 75.9Mb | 94.5Mb |

| DSP Slices(18x25 MACCs) | 3600 | 5520 | 6840 | 12288 |

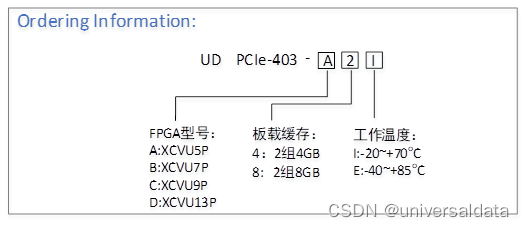

订购信息:

| 典型选型信息 | 配置说明 | 代理价(普票) |

| UD PCIe-403-C4I | XCVU9P, 2组4GB DDR4 | |

| UD PCIe-403-C8I | XCVU9P, 2组8GB DDR4 | |

| UD PCIe-403-D4I | XCVU13P,2组4GB DDR4 | |

| UD PCIe-403-D8I | XCVU13P,2组8GB DDR4 | |

| UD PCIe-403-A4I | XCVU9P, 2组4GB DDR4, 含千兆网和万兆网TCP/IP核 IP |

模块按照自主可控全国产化设计,兼容XCVU13PFHGB2104、JFM9VU13PB2104器件。