- 1【原创】android——SQLite实现简单的注册登陆(已经美化)

- 2【SpringBoot】报错:Property ‘sqlSessionFactory‘ or ‘sqlSessionTemplate‘ are required_springboot升级3.2后 property 'sqlsessionfactory' or '

- 3源码助力,游戏陪玩陪练更轻松

- 4xp系统能不能安装mysql_XP系统不能安装SQL Server 2000?

- 5Makefile的基础知识,看这篇就够了!_makefile文件

- 6CogImageConvertTool工具 图像处理工具

- 7[转]OKhttp 302 死循环

- 8【Python入门】超详细Python+Pycharm安装保姆级教程,Python环境配置和使用指南,看完这一篇就够了_pycharm配置python运行环境

- 92024前端面试题汇总

- 10在Windows10系统下安装SQL Server2000_windwo10 安装sqlserver 2000

JFMK50型号FPGA介绍

赞

踩

1.芯片介绍及主要事项

JFMK50 系列 FPGA 是复旦微电子在 28nm 工艺平台开发的高性能低功耗 FPGA 产品。JFMK50系列产品提供了可编程逻辑单元、数字信号处理单元、存储器单元、高速收发器以及强大的安全防护方案。面向5G通信、视频图像处理、工业控制、各类消费电子市场的需求,支持以下特征:

- LUT5 结构,支持进位链逻辑;

- 可配置存储器;

- 可配置 25 x 18 bit 乘法器,48bit 加法器;

- 输入输出端口支持多种电平标准(1.2V、 1.5V、 1.8V、2.5V、33V),支持差分LVDS;

- 支持高速DDR3接口,可达800Mbps;

- 支持高速收发器UHST,速率范围0.5-12.5Gbps,支持PCIE Gen1/Gen2;

- 可靠的安全方案,可选择 SM4 和 AES 加密方式,抗侧信道攻击;

- 支持片上电压和温度实时监测;

- 支持不同封装形式的9款产品(FCFBGA484、FCFBGA324、 FCFBGA236)。

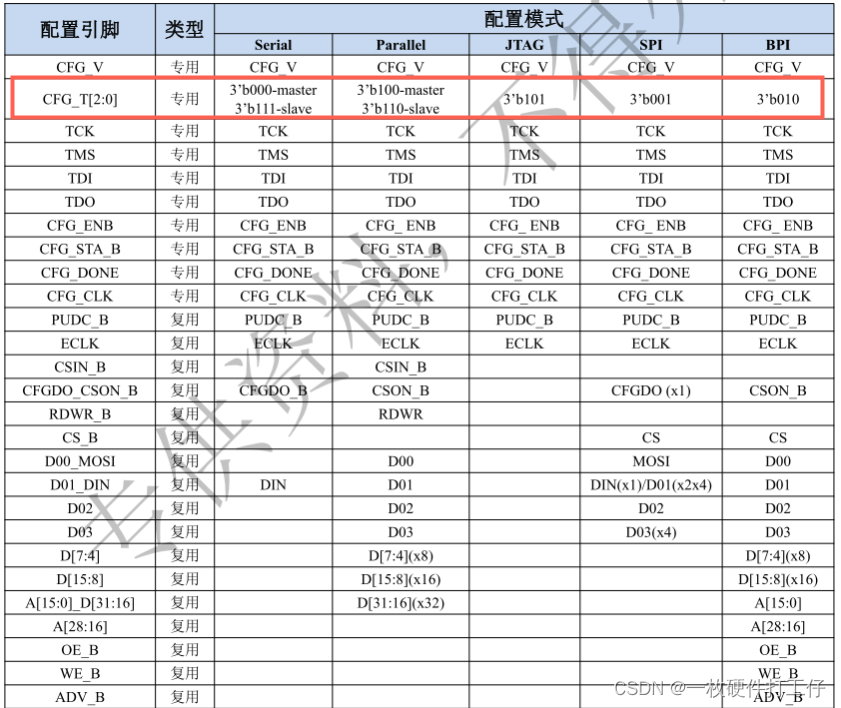

JFMK50的几种加载模式如下图,红色框是配置加载模式的PIN脚。

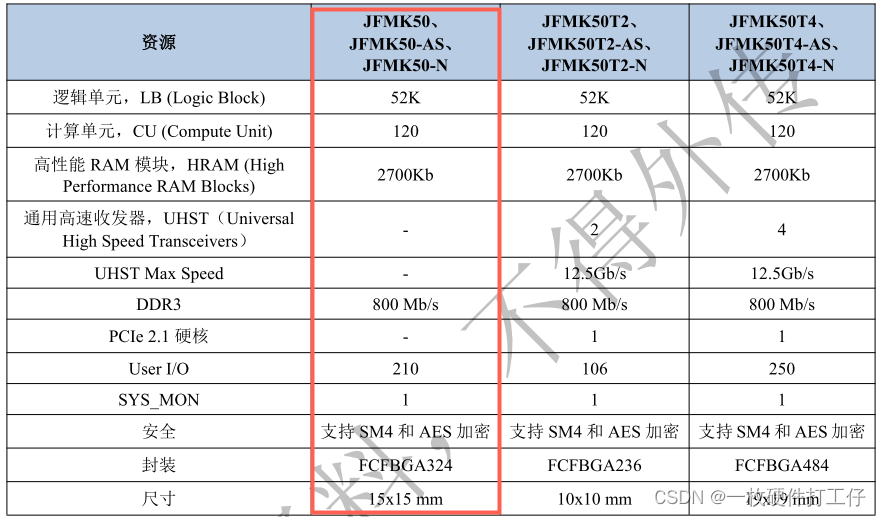

JFMK50的资源数量如下图,型号没有T后缀的是不带serdes的,T后缀是带serdes的。

配置管脚的说明如下图。

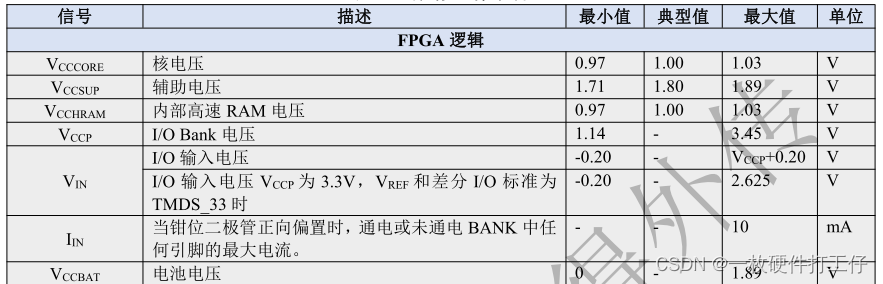

电源供电电压的要求。

- SYS_MON接口访问

SYS_MON模块可以支持JTAG访问或DRP接口访问。但用户在使用时,请勿使用DRP和JTAG接口同时访问SYS_MON。用户设计完成后,在DCLK时钟存在的情况下先对SYS-MON复位,复位释放后再开始使用DRP接口进行数据读写。

- CFG_V 信号接法

FO_VCCP 在任何电源电压下,FO_CFG_V 都上拉(上拉电阻 100Ω)至 FO_yCCP 电源。

- JTAG 信号接法

JTAG连接 FPGA 时,建议通过驱动芯片隔离分支结构对 JTAG 信号质量的影响,尤其以下两种场景务必使用驱动芯片隔离。

- 在JTAG链其中有多个下载口或信号走线有分支时;

- 在FPGA有多个下载口或信号走线有分支时。

此外,在TCK与TMS信号的驱动芯片输入端上拉10K电阻,以保证无Cable接入时,信号维持高电平。

- 上电顺序情况说明

下面两种上下电顺序都支持,为保证CFG_STA_B拉高后(芯片内部初始化完成时),电源已全部建立好,要求 VccP的上电速度<4ms,且FLASH 的电源在 CFG_STA_B拉高之前建立好,若不满足,可能导致SPI、BPI上电加载失败。

方案 1):

上电顺序: Vccsup -> Vccp -> Vcccore -> Vcchram

下电顺序: Vcchram -> Vcccore -> Vccp -> Vccsup

方案 2):

上电顺序: Vcccore -> Vcchram -> Vccsup -> Vccp

下电顺序: Vccp -> Vccsup -> Vcchram -> Vcccore

- 当Vccp大于1.8V时, Vccsup必须先于Vccp上电。

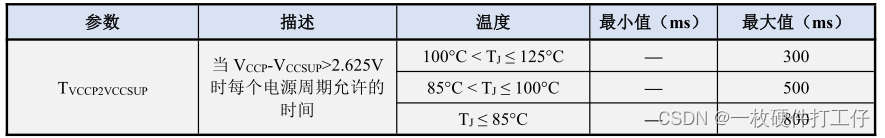

- 当Vccp- Vccsup >2.625V时对Vccp和Vccsup的上电时间关系也有要求,见下表。

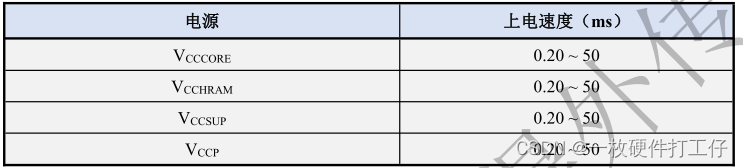

- 电源上电速度表如下表:

2.原理图设计检查

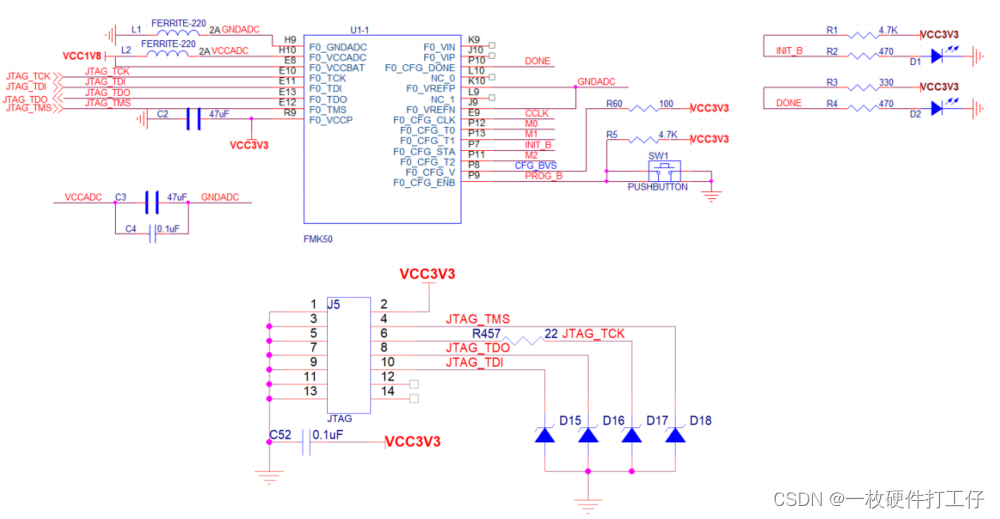

FMK50 系列支持 7 种配置模式,上面有介绍。其中主 SPI模式所需管脚少,加载速度快,应用最为广泛。

FMK50 典型设计参考图如下:

本设计中JTAG只是使用了最简单的连接方式。为增强JTAG电路抗ESD能力和提升信号完整性,JTAG的设计推荐采用隔离buffer方案,具体要求详见3.5节JTAG配置check。

影响主SPI配置的几点:

1.硬件电路设计上不要将CSIN和RDWR信号作为普通1O使用;

2.CFG_V需通过电阻上拉,上拉电阻不大于100欧姆;

3.PUDC管脚不能悬空,上拉或者接地;

4.保证加载模式中的主控器件上电完成时间不要早于从器件。

5·在FPGA工程中不要将配置管脚当作普通1O使用。

6·在位流设置中, CCLK的频率不要高过33MHZ。

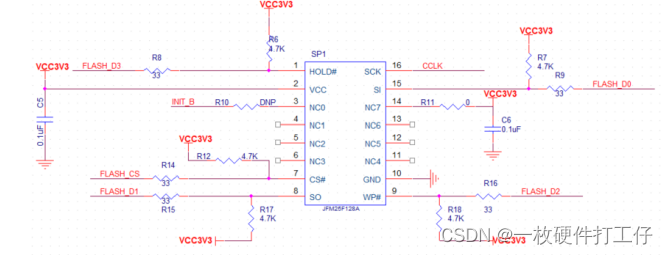

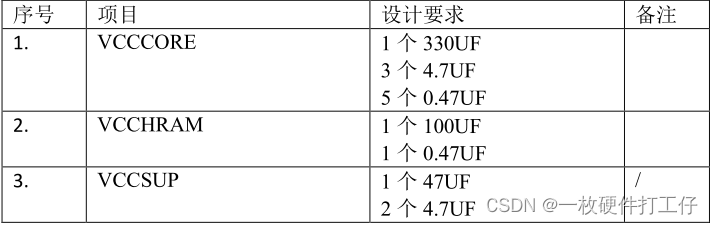

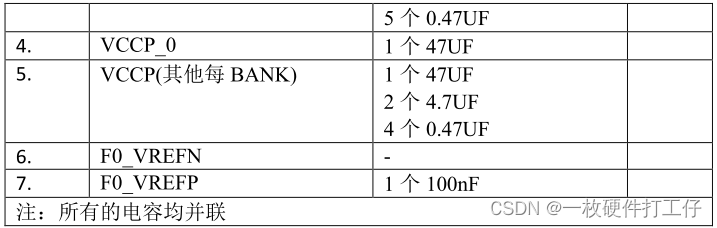

去耦电容设计要求如下图:

JTAG配置电路时,若JTAG链中有多个下载口或者信号走线有分支时,为保证JTAG信号的菊花链结构,建议JTAG信号分支位置在进入菊花链上第一片FPGA前,并且通过Buffer芯片隔离分支结构对JTAG信号质量的影响,示意图如下图所示。并在TCK与TMS信号的Buffer输入端上拉10KΩ电阻,以保证无Cable接入时,信号维持高电平。

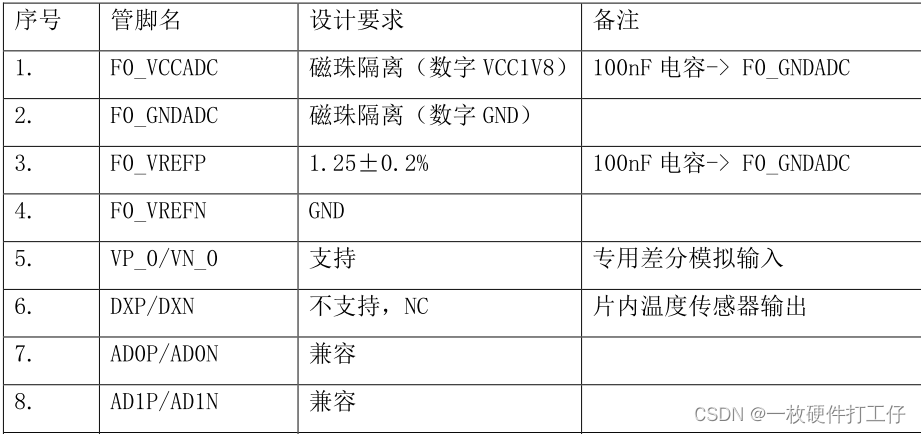

XADC设计要求如下图:

1、专用差分模拟输入通道VP_0和VN_0,若不使用时,这两个管脚可以接GND

2、片内温度传感器输出DXP和DXN功能不支持,为NC管脚,可以悬空或接GND.

特殊管脚F0_VCCBAT接法说明:

我司采用了更安全的加密方案,需存储更多秘钥数据, BBRAM的容量无法满足,故不支持BBRAM加密秘钥存储方案,仅支持EFUSE秘钥烧写方式。

板级F0_VCCBAT电源可以与VCCSUP 1.8V接一起,或者NC。