- 1【YOLO】voc(xml格式)转换成coco(json格式)代码_python voc标注转json

- 2【转载】 腾讯云硬盘不够用,如何对硬盘进行扩容

- 3如何使用电脑连接云电脑服务器(教程)_电脑连接服务器

- 4go技术文章梳理(2018)_j cc……69

- 5Web安全之注入类漏洞详解及预防_注入类安全漏洞

- 6Transformer系列:图文详解Decoder解码器原理_transformer的decoder

- 7(35)远程识别(又称无人机识别)(一)

- 8GIT 拉取或者提交项目时, 遇到长路径提示file name too long_idea git文件路径过长

- 9HBase基本概念与基本使用_hbase scan table family

- 10无法连接至许可证服务器系统。服务器(Imgrd)尚未启动,或SPLM_LICENSE SERVER被设为错误的“端口@主机“。_服务器imgrd尚未启动或splm

FPGA实现基于DDR3的多通道图像数据读写控制模块:纯Verilog代码,清晰接口,高可移植性_soc fpga把ov5640数据写入ddr3

赞

踩

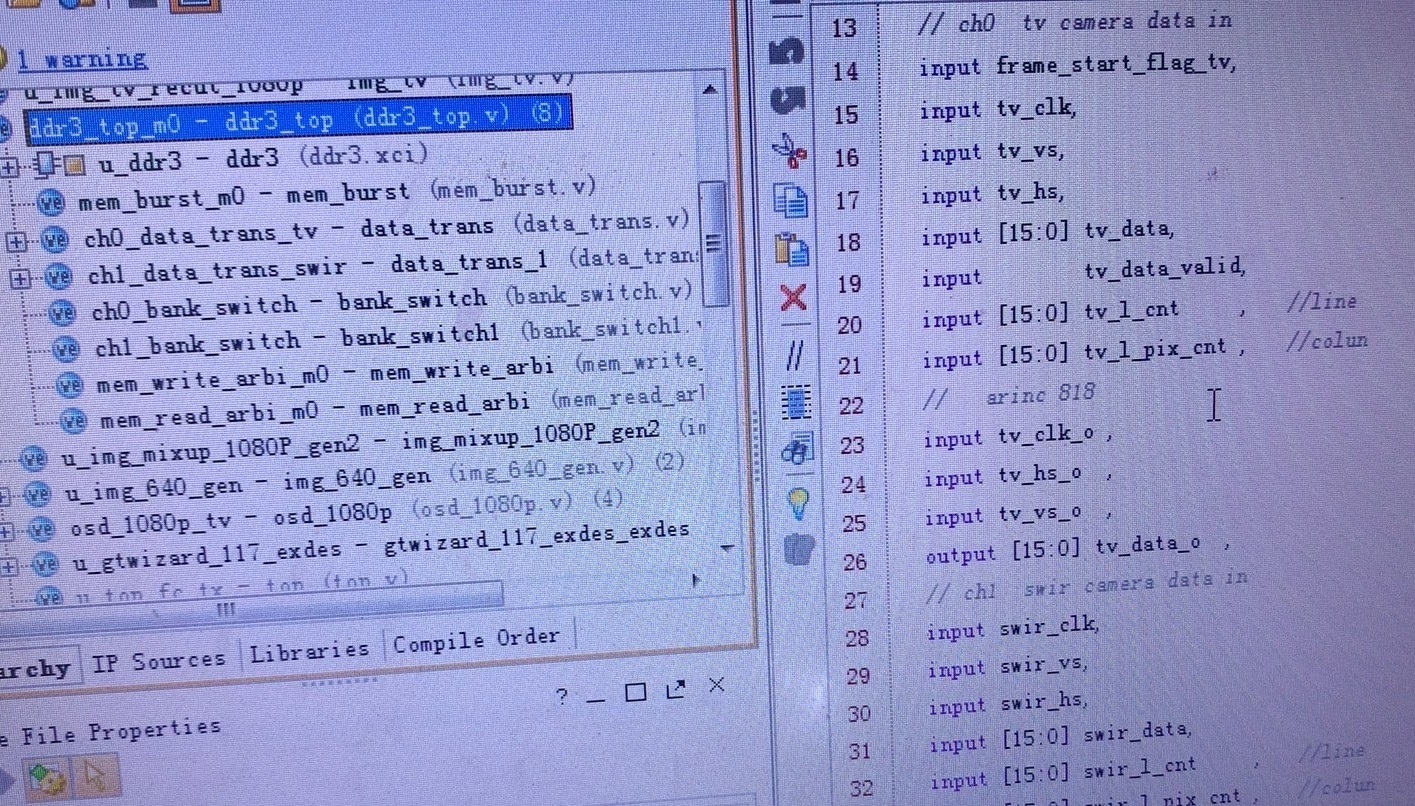

基于fpga的ddr3读写控制,纯verilog实现,能实现多通道图像数据读写控制,模块接口清晰,可移植性高.

ID:77198721821934069

夏日蝉鸣

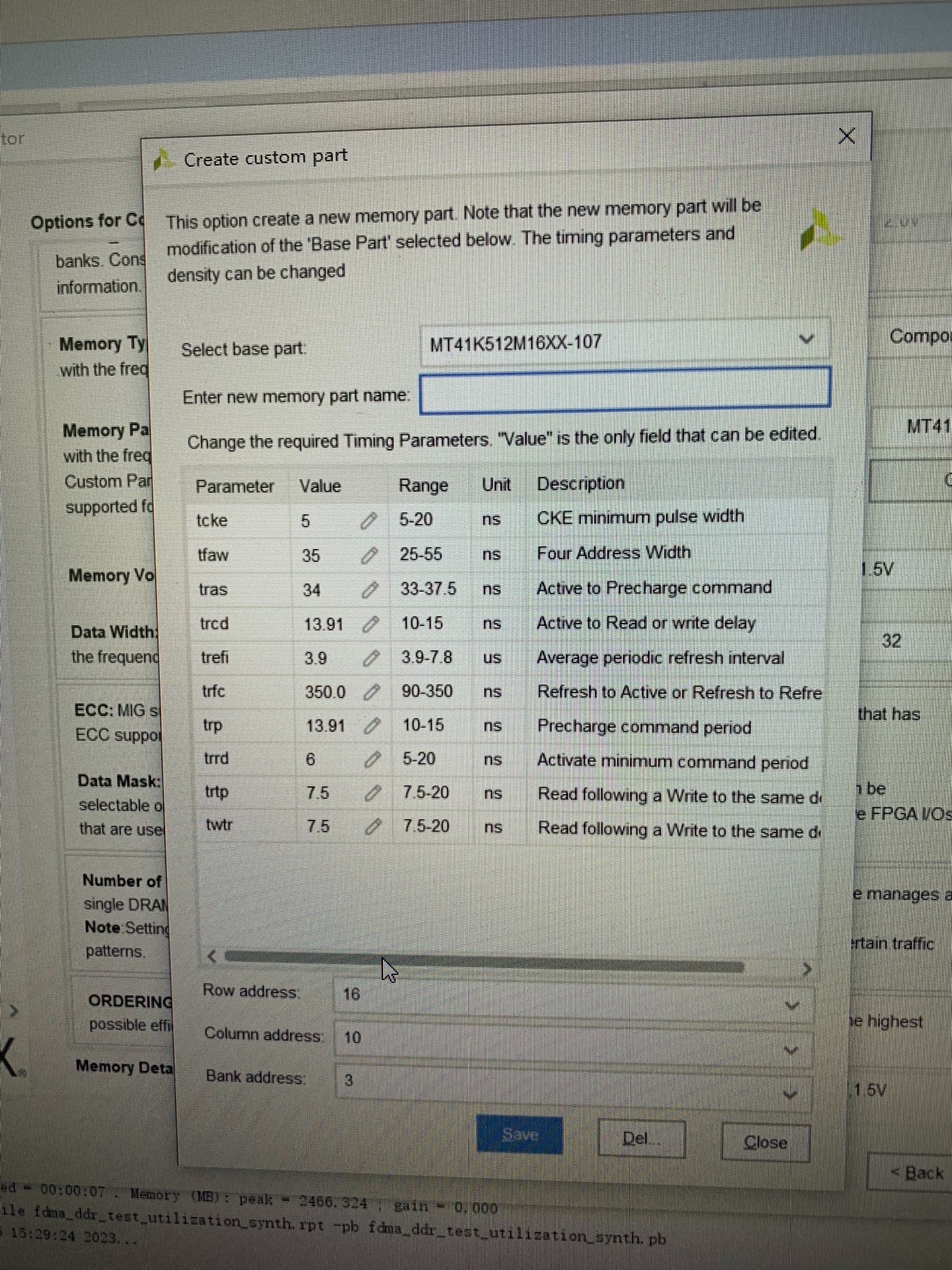

基于FPGA的DDR3读写控制是一项重要的技术,它为多通道图像数据的读写提供了高效的解决方案。本文将介绍一种纯Verilog实现的DDR3读写控制模块,旨在实现模块接口清晰、可移植性高的特点。

首先,我们来探讨为什么选择FPGA作为实现DDR3读写控制的平台。FPGA具有可编程性强、并行处理能力高等特点,能够满足DDR3的高速数据传输需求。相比传统的微控制器,FPGA能够提供更高的数据吞吐量和更低的延迟,为图像数据的实时处理提供了良好的基础。

在实现DDR3读写控制的过程中,我们选择采用纯Verilog的方式,这样可以充分发挥FPGA的硬件特性,提高代码的运行效率。同时,纯Verilog实现也保证了模块的可移植性,可以方便地应用于不同型号的FPGA芯片中。

DDR3读写控制模块的设计中,我们需要考虑多通道数据的读写操作。通过设计合理的模块接口,可以实现同时针对多通道数据进行读写,提高系统的并行处理能力。模块接口的清晰性是实现高效通信的关键之一,我们将通过分析各个接口的功能和作用,确保其清晰易懂。

在实际的设计中,我们需要根据DDR3的时序要求,对读写操作进行控制。通过详细分析DDR3的时序图,我们可以编写Verilog代码,精确控制读写操作的时序,保证数据的正确传输和存储。

此外,设计一个高性能的DDR3读写控制模块还需要考虑其稳定性和可靠性。通过合理的时钟同步和数据校验机制,可以降低因时钟抖动或传输错误而引起的数据丢失或损坏的风险。

在最后的实现中,我们将通过一系列的仿真和测试,验证DDR3读写控制模块的功能和性能。通过编写合适的测试用例,我们可以全面测试模块的各种功能,并对其性能进行评估。只有经过充分的测试,我们才能确保DDR3读写控制模块在不同场景下的稳定性和可靠性。

综上所述,基于FPGA的DDR3读写控制模块以其高效性、可移植性和稳定性,在多通道图像数据的读写应用中展现出了巨大的潜力。本文通过纯Verilog的实现方式,详细介绍了该模块的设计原理和实现方法,旨在为读者提供一个清晰、全面的技术分析,帮助其更好地理解和应用该技术。希望本文对读者在DDR3读写控制领域的学习和研究有所帮助。

【相关代码 程序地址】: http://nodep.cn/721821934069.html