热门标签

热门文章

- 1[ 环境搭建篇 ] 安装 java 环境并配置环境变量(附 JDK1.8 安装包)_如何安装环境1.8

- 2MySQL 约束详解_mysql的约束

- 3HTML期末大作业-小米商城_html期末作业选小米商城的理由

- 4开发模式-敏捷开发_敏捷开发模型

- 5构建大语言模型的四个主要阶段_大语言模型一共要经历几个阶段

- 6互联网工作 常用名词及基础知识扫盲

- 7Eclipse——导出可执行jar包_eclipse导出可执行jar包

- 8Java空指针异常:java.lang.NullPointException_simpledateformat.format java.lang.nullpointerexcep

- 9主成分分析(PCA)中的特征值与特征向量,特征值是不是数据在特征向量方向上的方差_pca 的特征值 特征向量

- 10Gradle和IDEA的匹配关系_idea gradle 版本对照

当前位置: article > 正文

FPGA的仿真介绍_fpga仿真

作者:知新_RL | 2024-03-28 19:28:41

赞

踩

fpga仿真

仿真概述:

由于在FPGA 设计的过程中,不可避免的会出现各种 BUG。

但如果在编写好代码、综合成电路、烧写到FPGA 后才发现问题,此时再去定位问题就会非常地困难。

而在综合前,设计师可以在电脑里通过仿真软件对代码进行仿真测试,检测出 BUG 并将其解决,最后再将程序烧写进 FPGA。一般情况下可以认为没有经过仿真验证的代码,一定是存在 BUG 的。

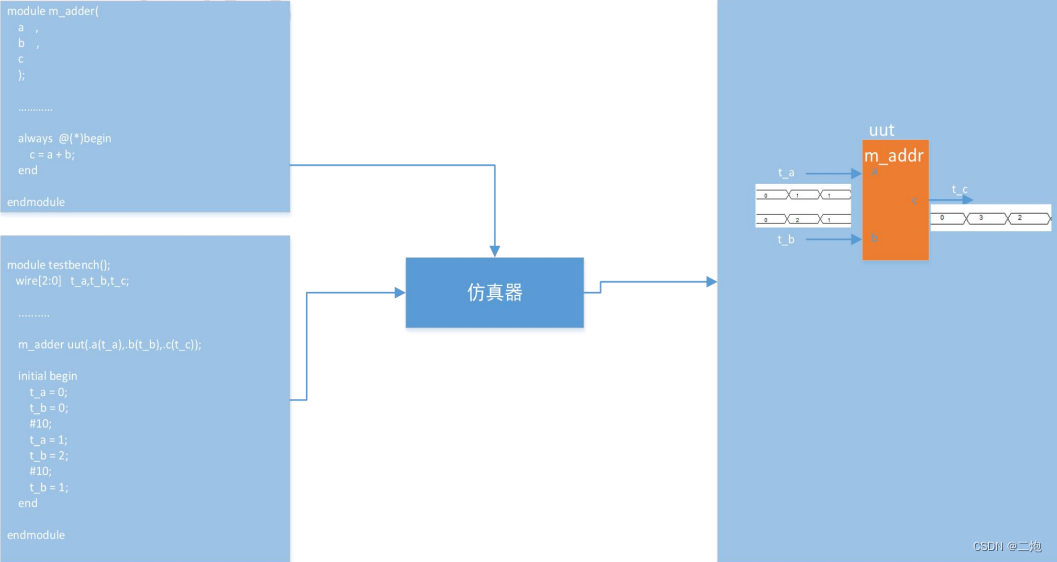

为了模拟真实的情况,需要编写测试文件。该文件是用 Verilog 编写的,其描述了仿真对象的输入激励情况。该激励力求模仿最真实的情况,产生最接近的激励信号,将该信号的波形输入给仿真对象,查看仿真对象的输出是否与预期一致。需要注意的是:在仿真过程中没有将代码转成电路,仿真器只是对代码进行仿真验证。至于该代码是否可转成电路,仿真器并不关心。

由此可见,Verilog 的代码不仅可以描述电路,还可以用于测试。事实上,Verilog 定义的语法非常之多,但绝大部分都是为了仿真测试来使用的,只有少部分才是用于电路设计。Verilog 中用于设计的语法是学习的重点,掌握好设计的语法并熟练应用于各种复杂的项目是技能的核心。而其他测试用的语法,在需要时查找和参考就已经足够了。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/知新_RL/article/detail/330875?site

推荐阅读

相关标签