- 1Python版开心消消乐来了,你能通关吗?_tree = manager.managertree()

- 2Go 语言中的数组:声明、初始化与应用

- 3图形设计软件 CorelDRAW Graphics Suite 2024 v25.0.0.230 中文破解版_coreldraw 2024

- 4零基础小白怎么入门CTF?全网最全CTF入门指南_ctf入门教学

- 5NL2SQL进阶系列(4):ConvAI、DIN-SQL、C3-浙大、DAIL-SQL-阿里等16个业界开源应用实践详解[Text2SQL]_nl2sql 应用

- 6C++结合OpenCV进行图像处理与分类

- 7【MySQL】数据类型_mysql数据库数据保存格式

- 8算法:排序 二叉树深度时间复杂度? 归并和快速排序实践?B树时间复杂度?_二叉树排序的复杂度

- 9后悔买了盗版TeamViewer软件,安全没一点保障_teamviewer有啥危害吗

- 10基于STM32的智能门锁/智能门禁多功能系统_stm32智能门锁

关于IDELAYE2的学习与使用_idelaye2原语

赞

踩

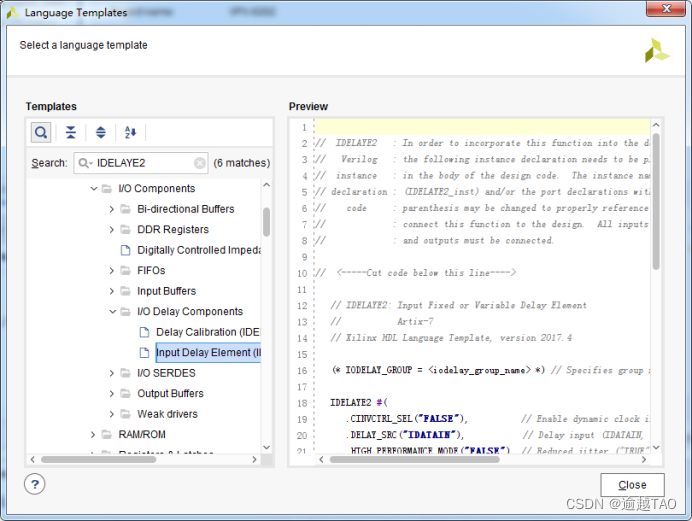

一、IDELAYE2原语调用

选择Tools中的Language Templates即可进行原语的调用;

打开后可以看到Templates栏中是几种语言的原语,根据自己的使用(FPGA类型、语言类型)选择相应即可,在左上角可以搜索需要的原语进行使用,在左边选择需要的原语后,右边会显示出对应的源码,直接复制使用即可;

二、IDELAYE2原语结构

IDELAYE2原语结构,左边信号是输入,右边信号是输出;

三、IDELAYE2相关信号释义

| 信号名称 | 方向 | 位宽 | 说明 |

| C(CLOCK) | input | 1 | 在 VARIABLE、VAR_LOAD 或 VAR_LOAD_PIPE 模式下使用的时钟输入 |

| REGRST | input | 1 | 复位pipeline寄存器,只用在VAR_LOAD_PIPE类型下 |

| LD | input | 1 | 在VARIABLE模式下,加在IDELAYE2延时的值,LD、CD、INC配合使用 |

| CE | input | 1 | 使能增加或者减少的功能 |

| INC | input | 1 | 增加或者减少基数(tap)数量 |

| CINVCTRL | input | 1 | 动态转换时钟极性 |

| CNTVALUEIN | input | 5 | 延迟基数(tap)输入 |

| IDATAIN | input | 1 | 来自IBUF的输入数据 |

| LDPIPEEN | input | 1 | 使能pipeline寄存器寄存器来加载数据 |

| DATAIN | input | 1 | 来自逻辑设计中的数据 |

| DATAOUT | output | 1 | 来自两个数据输入端口(DATAIN或IDATAIN)中的延迟数据输出。 |

| CNTVALUEOUT | output | 5 | 延迟基数(tap)输出 |

四、IDELAYE2属性释义

| 信号名称 | 模式 | 默认值 | 说明 |

| CINVCTRL_SEL | FALSE TRUE | FALSE | 选择FALSE可动态配置输入延迟基数(tap); |

| DELAY_SRC | IDATAIN DATAIN | DATAIN | IDATAIN:来自IBUF的输入数据; DATAIN:来自逻辑设计中的数据; |

| HIGH_PERFORMANCE_MODE | FALSE TRUE | FALSE | FALSE:减少输出功耗; TRUE:较少输出抖动; |

| IDELAY_TYPE | FIXED VARIABLE VAR_LOAD VAR_LOAD_PIPE | FIXED | FIXED:固定延迟值,搭配IDELAY_VALUE信号; VARIABLE:延迟值可以在配置后通过CE和INC端口进行动态配置; VAR_LOAD:在VARIABLE的基础上可通过直接CNTVALUEIN输入设置; VAR_LOAD_PIPE:与VAR_LOAD类似,用于pipe寄存器; |

| IDELAY_VALUE | 0~31 | 0 | 延迟基数(tap)值 |

| PIPE_SEL | FALSE TRUE | FALSE | 选择pipeline寄存器模式,只用于VAR_LOAD_PIPE模式下; |

| REFCLK_FREQUENCY | 190.0-210.0, 290.0-310.0 | 300 | 参考输入时钟范围; |

| SIGNAL_PATTERN | DATA CLOCK | DATA | 数据或者时钟; |

五、IDELAYCTRL说明

在使用IDELAYE2或ODELAYE2原语时,必须同时使用IDELAYCTRL,IDELAYCTRL模块在其区域内连续校准单个延迟点(iddelay /ODELAY),以减少过程、电压和温度变化的影响。IDELAYCTRL模块使用用户提供的REFCLK校准IDELAY和ODELAY。

| 信号名称 | 方向 | 位宽 | 说明 |

| RDY | output | 1 | 选择FALSE可动态配置输入延迟基数(tap); |

| REFCLK | input | 1 | 参考时钟; |

| RST | input | 1 | 高电平复位; |

六、IDELAYCTRL设计仿真

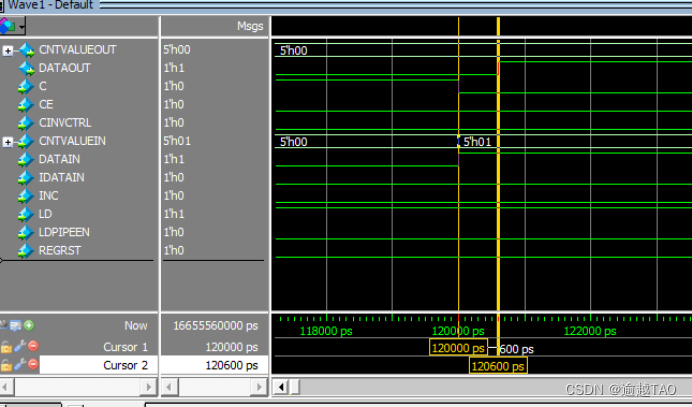

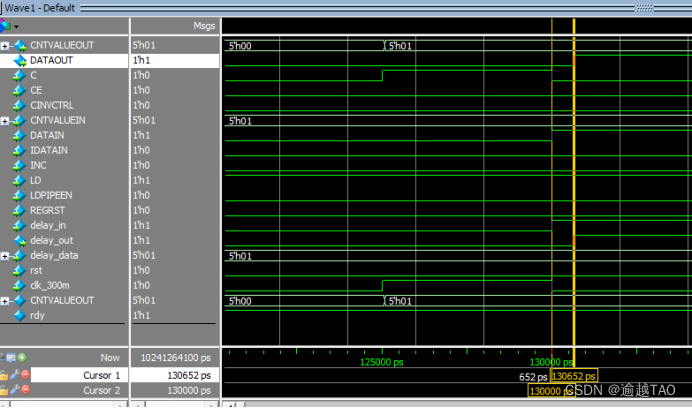

在300M时钟下,当输入CNTVALUEIN为0时,默认输出延迟600ps;可以看到当CNTVALUEIN为1时,输出延迟为652ps,当CNTVALUEIN增加1时,输出延迟就增加52ps;