热门标签

热门文章

- 1python生物信息学数据管理_02第一个python程序_计算胰岛素中的人氨基酸频率python

- 2zookeeper集群搭建

- 3附录5-黑马头条案例,组件库vant_vant案例

- 4黑客帝国中比较酷炫的代码雨的实现_手机黑客代码雨代码复制

- 5AndroidStudio导入程序、项目(教程)_android studio导入idea项目

- 6国产ChatGPT科大星火大模型v3.5使用教程_nas搭建星火3.5

- 7WPF中的文字修饰——上划线,中划线,基线与下划线_wpf textdecorations

- 8yolov9 瑞芯微 rknn 部署 C++代码_yolov9 转rknn

- 9第九章:AI大模型的实践案例9.2 医疗领域9.2.2 药物研发与基因编辑

- 10Hadoop在Ubuntu系统下的安装和部署_ubantu下载的hadoop压缩包放在哪个文件夹里

当前位置: article > 正文

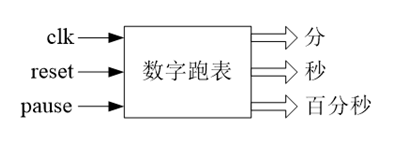

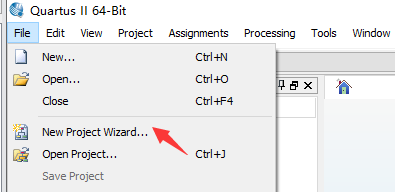

基于Verilog HDL的数字时钟_verilog数字钟实验报告

作者:知新_RL | 2024-06-15 10:32:52

赞

踩

verilog数字钟实验报告

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/知新_RL/article/detail/721972

推荐阅读

相关标签