热门标签

热门文章

- 1设置Linux时区和时间_linux 修改时区为北京

- 2嵌入式系统在工业自动化中的智能化和自适应控制_自适应嵌入式控制

- 3Golang | Leetcode Golang题解之第229题多数元素II

- 4应急响应-战后溯源&IP&ID追踪&URL反查&攻击画像_追踪溯源ip

- 5顶会ICLR2024论文Time-LLM:基于大语言模型的时间序列预测_松鼠ai首席科学家文青松

- 6贪心法之柠檬水找零_贪心法柠檬水找零

- 7python中列表(list)拼接的三种方法_list拼接

- 8Android Studio中Gradle依赖详解

- 9PCA算法原理_pca算法的基本原理

- 10什么是百度快照劫持?百度快照劫持原理和解决办法

当前位置: article > 正文

后仿真中《SDF反标必懂连载篇》之 timing violation 你读对了?_后仿violation分析

作者:神奇cpp | 2024-08-14 11:14:48

赞

踩

后仿violation分析

大家好,今天主要记录和大家分享一下,最近一直在搞的GLS,一点点仿真心得。对于第一次实战门级网表仿真的朋友,肯定内心有一万个疑问不解。其实没有别的办法,向有经验的老师傅请教,是一个不错的渠道。另外,我们要自己上心,有疑问,解决疑问,才能真正的成长。

一 问题背景

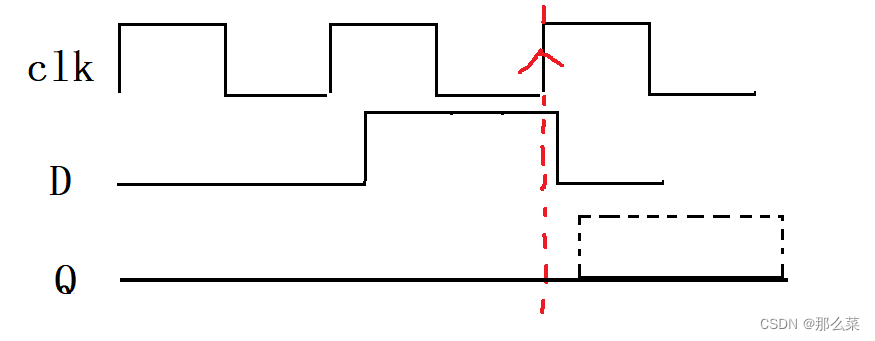

实际GLS仿真中发现,DFF 的输入 为D, 输出为 Q,在clk 上升沿处采样。

惊奇发现,在没有报该DFF hold timing violation 的前提下,竟然出现数据采样错误。

这里发生了什么?

这里疑问:

(1)假如这里不满足时钟上升沿处 hold timing 时序要求, 那么log 中应该报出该DFF的 hold timing viloation 信息。但是,查看 log, 并没有报时序违例。

(2)假如按照 setup/hold 检查设置,如果不满足其一,那么会VCS 工具会进行随机采样0、1 的?

二 Standard Cell的仿真模型

首先我们先看一个stand cell的仿真模型。一般情况下,仿真模型包括两个部分:

第一个部分是功能部分也就是这个standcell的功能,可以用udp元件或者逻辑功能做表述;

第二个部分是时序反标和时序检查部分,这部分主要是提供sdf反标

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/神奇cpp/article/detail/979489

推荐阅读

相关标签