- 1居然才发现!字节跳动旗下国产AI绘画工具Dreamina,这么好用居然还免费!(强烈推荐)_dreammina

- 2k-modes聚类算法及python代码实现

- 3COLMAP的安装_虚拟机安装colmap

- 4androidstudio升级2.2出现导入第三方库出错解决方法_android studio引入第三方库后the binary version of its

- 5json转换成excel在线js小工具分享【不限制大小】_json在线转excel 子对象

- 6【微信小程序开发实战项目】——如何制作一个属于自己的花店微信小程序(1)

- 7树--二叉树理论基础

- 8JVM之内存与垃圾回收——JVM与Java体系结构_创建一个初始类来完成的,这个类是由虚拟机的具体实现指定。

- 9tkinter入门(9)--布局管理器(pack,grid,place)_tk pack 两个组件并排

- 10Android实现WebServer(服务端)之AndServer_android andserver

STM32F103 最小系统 PCB 设计与原理_stm32f103cbt6最小系统

赞

踩

这篇文章是来自我学习:

带着你从手册开始画板 STM最小系统板教程系列(一)_哔哩哔哩_bilibili

这套教程的笔记,同时本文中也参考了其他教程以及我遇到的困惑与自答,最终汇总。

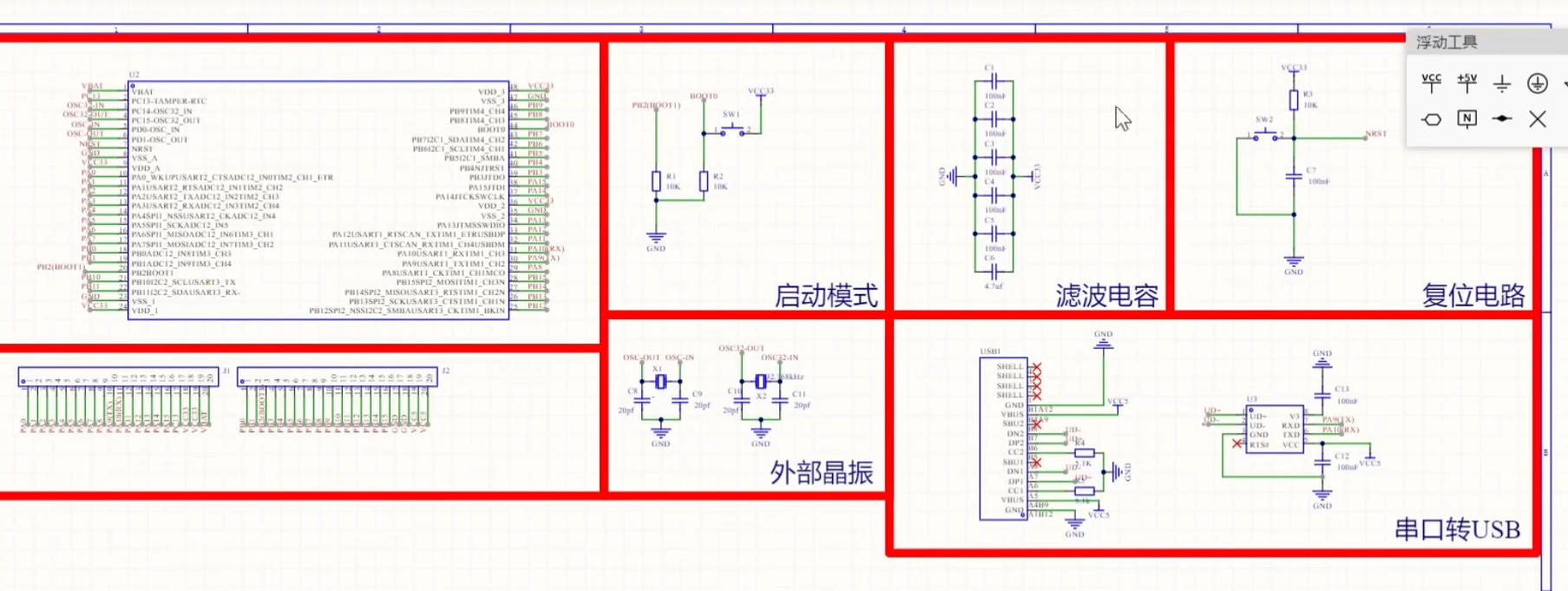

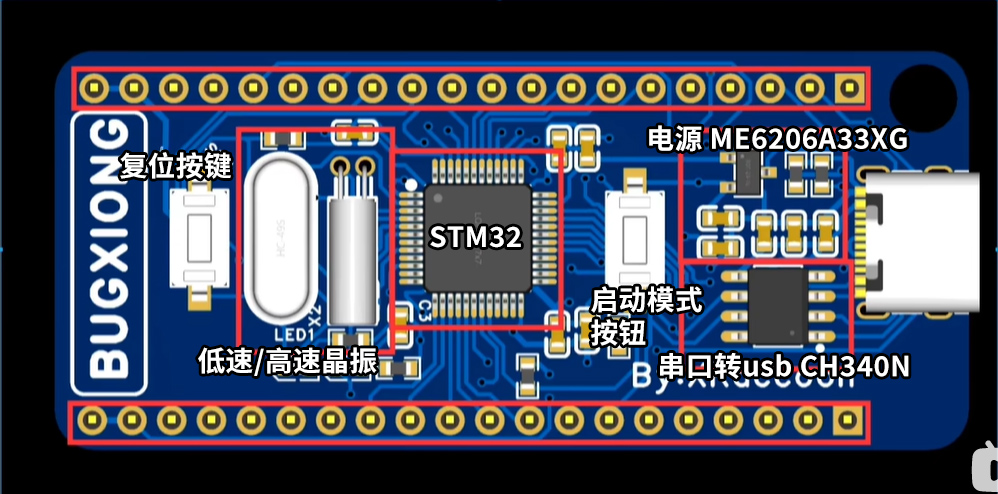

一、单片机最小系统

单片机最小系统是由芯片外部接上时钟电路、复位电路和电源构成的一个基本应用系统。主要包含的部分,单片机、时钟电路、复位电路、电源电路、程序加载口。

下图就 是PCB 最终效果。

二、主控芯片

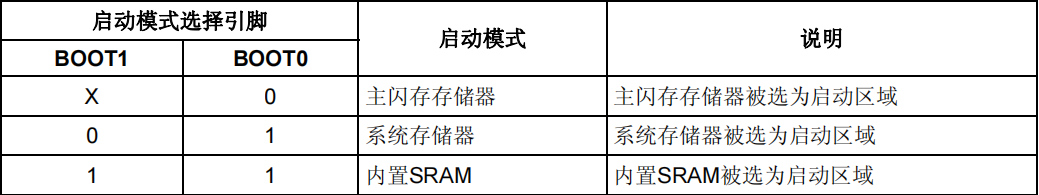

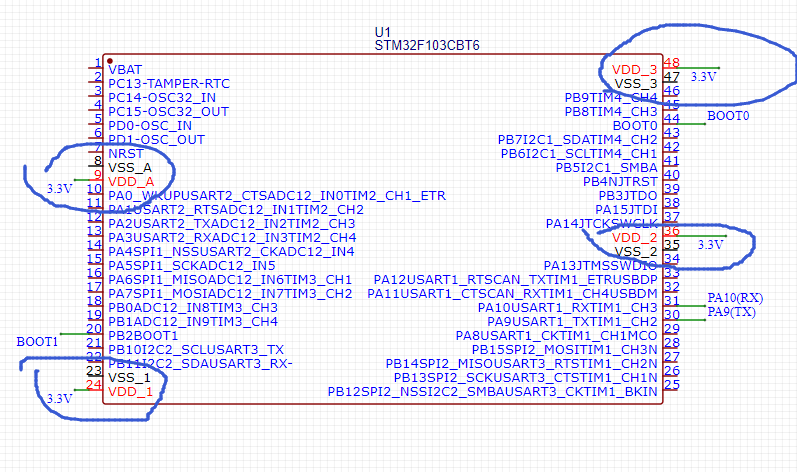

这里使用 STM32F103CBT6,首先应该设置启动模式电路,在STM32 都有 BOOT1 和 BOOT0 两个引脚,接低或者高电平即可配置。

在系统复位后,SYSCLK的第4个上升沿,BOOT引脚的值将被锁存。用户可以通过设置BOOT1和BOOT0引脚的状态,来选择在复位后的启动模式。

一般来说,我们都使用主闪存模式 (flash),来作为启动区域。

不过在烧录串口程序中,我们则需要系统存储器启动系统。系统储存器在出厂时设定了 bootloader (引导程序),用此方式启动,向 STM32 串口写入代码,引导程序将会帮我们把把代码写入到 flash 中。之后将引脚转化到主闪存模式 (flash),复位即成功烧录代码并运行。

当然如果我们使用 stlink、DAP 之类的调试器,则不需要设置这些,并且它还具有代码断点查看内存等功能。不过本教程并没有板载内置调试器,如果想用则只能外置了。

2.1 主控芯片 PCB 设计

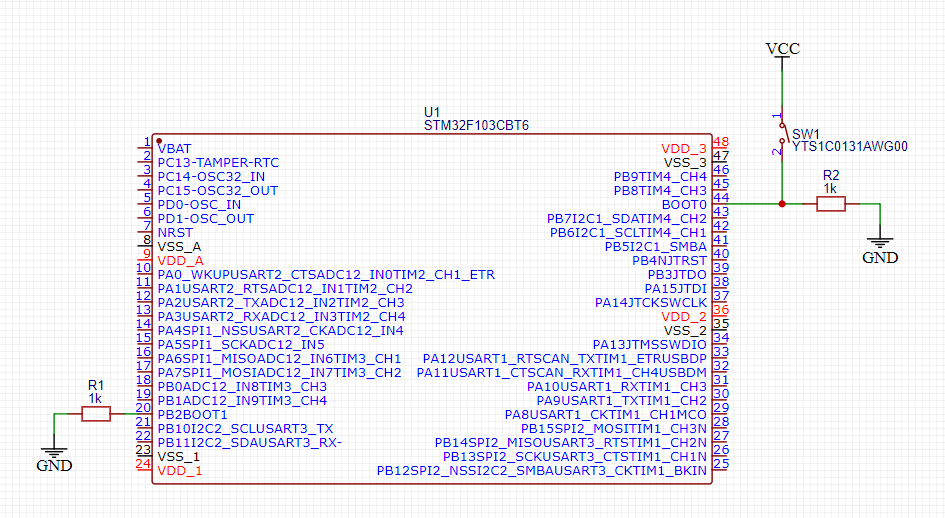

以下便是 STM32F103CBT6 的 BOOT1 和 BOOT2 引脚原理图。

在 BOOT1 处接入了一个按钮,使得我们可以切换主闪存和系统储存。

最后我们把电路整理成这样:

三、复位电路

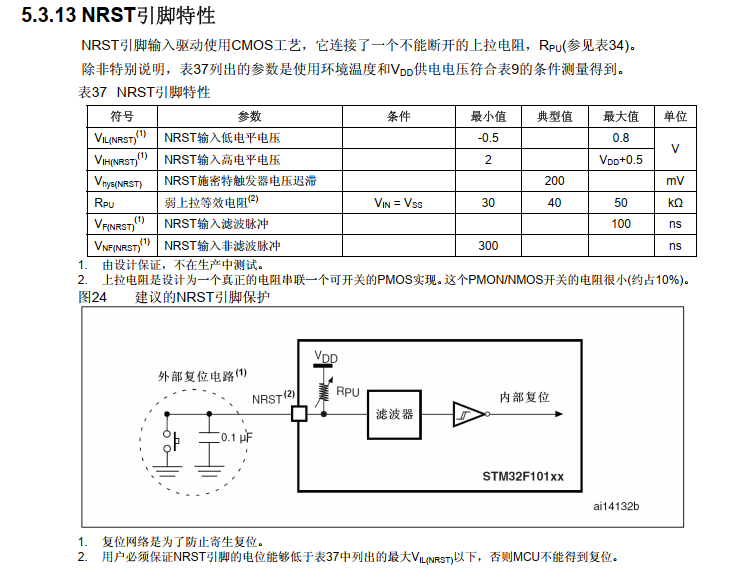

根据 STM32F103x8B 数据手册 5.3.13 章节提示,复位引脚在芯片内部以及接了一个永久上拉电阻。也就是通上电此引脚将永久处于高电平。同时也给出了推荐电路设计。

3.1 复位电路 PCB 设计

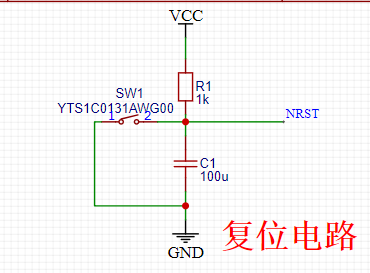

我们并不使用手册中建议的复位电路,而是采用这样的结构:

上图复位电路,在刚上电时c1电容需要一定时间充电,在此时 NRST 处于低电平。低电平时系统复位,这样每次上电系统就能自动复位一次。或者我们摁下按钮,也会使得电路接地,进行复位。

四、外接晶振

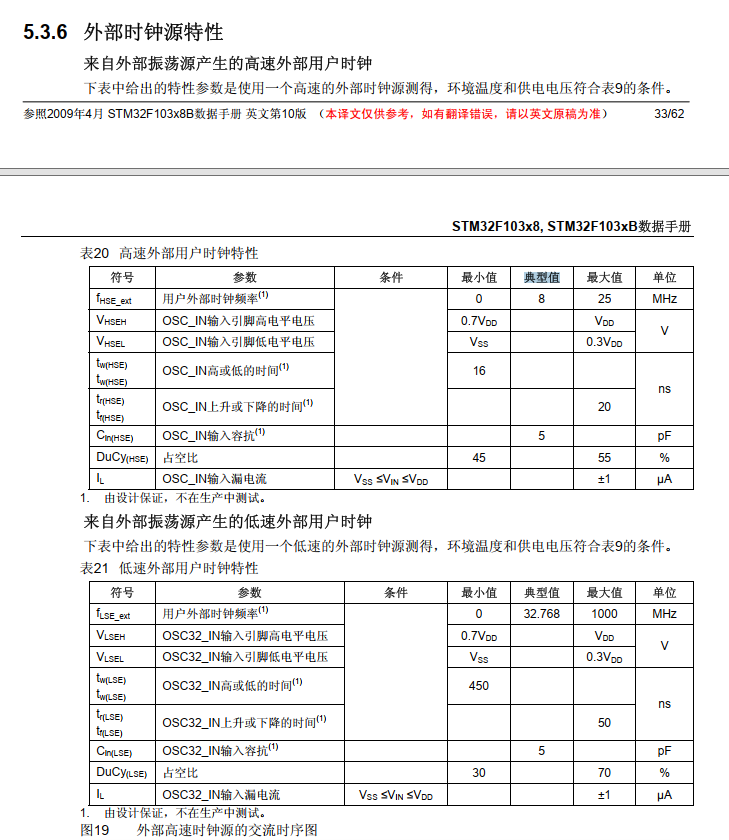

根据 STM32F103x8B 数据手册 5.3.6 章节提示,高速外部时钟 (HSE) 的频率应该在 0~25MHz 之间,低速外部时钟 (LSE) 应该在 0~1000KHz 之间。在这里我们使用其中的两个典型值 8MHz 和32.768KHz。

32.768KHz 在 15 次二分频后即可得到 1Hz 很适合作为时钟使用。

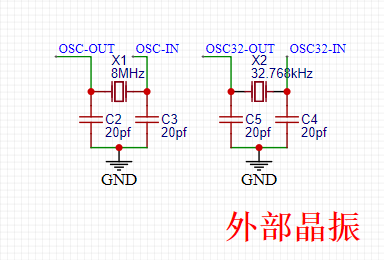

4.1 外接晶振 PCB 设计

晶振电路需接入两个 20pf 电容。

五、电源

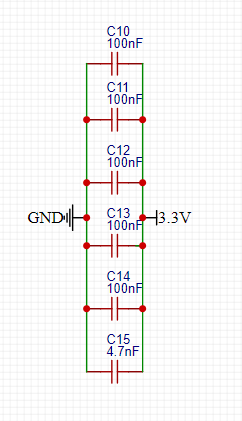

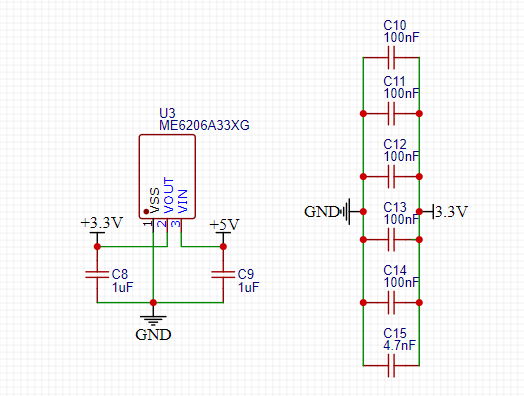

5.1 线性稳压器 (LDO)

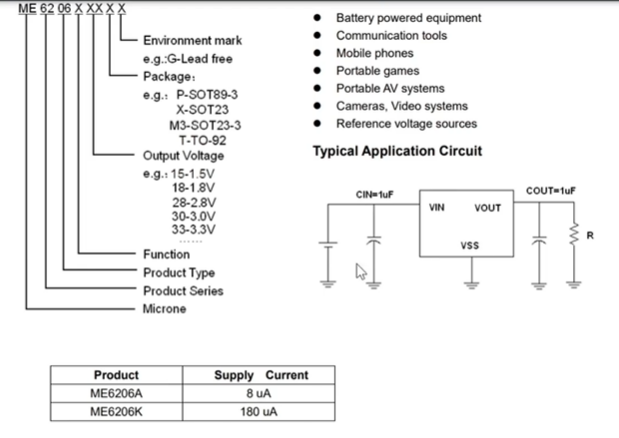

在这里使用了 me6206a33 作为稳压电源,主要是因为他体积小,比较适合这个板子。

根据参考手册提示,VIN 和 VOUT 都需要接入 1uF 的电容。

pcb设计如下:5V 为输入电源,3.3V 为输出。

5.2 STM32 电源引脚配置

其中名词解释:

| VCC | 电路的供电正电压 | VDDD | 芯片的工作数字正电压 |

| GND | 电路的供电负电压 | VSSD | 芯片的工作数字正电压 |

| VDD | 芯片的工作正电压 | VREF+ | ADC基准参考正电压 |

| VSS | 芯片的工作负电压 | VREF- | ADC基准参考负电压 |

| VDDA | 芯片的工作模拟正电压 | VBAT | 电池或其他电源供电 |

| VSSA | 芯片的工作模拟负电压 | VEE | 负电压供电 |

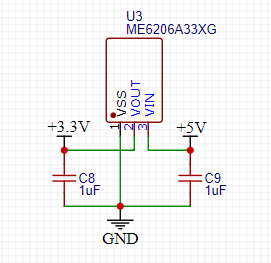

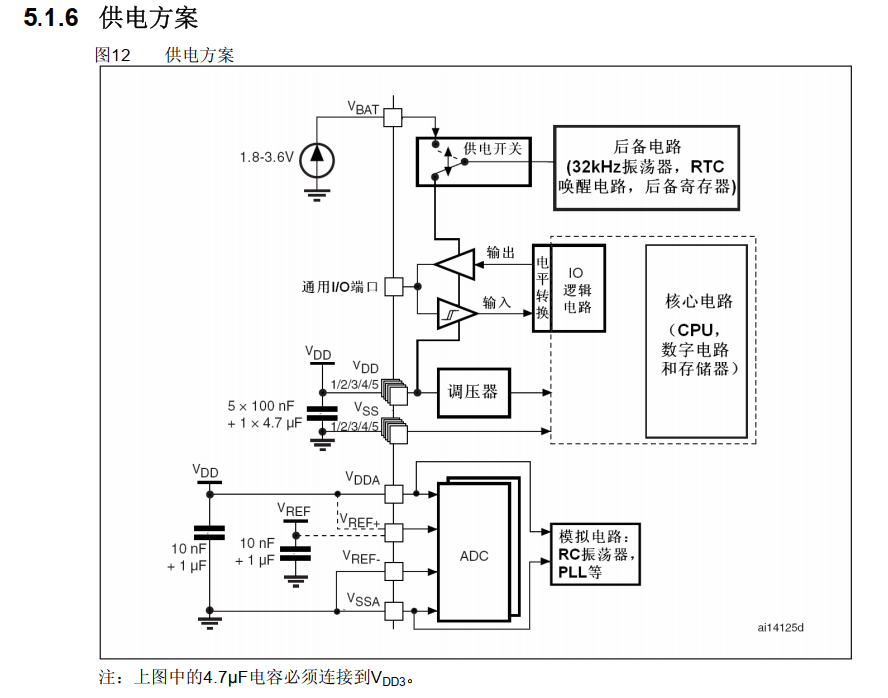

在图中提示出很重要的一点:VDD 被要求接入 5x100nf + 1x4.7uf 共六个电容。VDDA 和 VREF+ 也被要求接入特定的电容。 所以我们构建电路:

我在观察一些开源项目时,发现很多项目并没有按照这手册说明给足电容。关于这个问题我特地咨询了一位工程师:

并接入 STM32:

并接入 STM32:

5.3 电源的 pcb 设计

六、串口转 USB

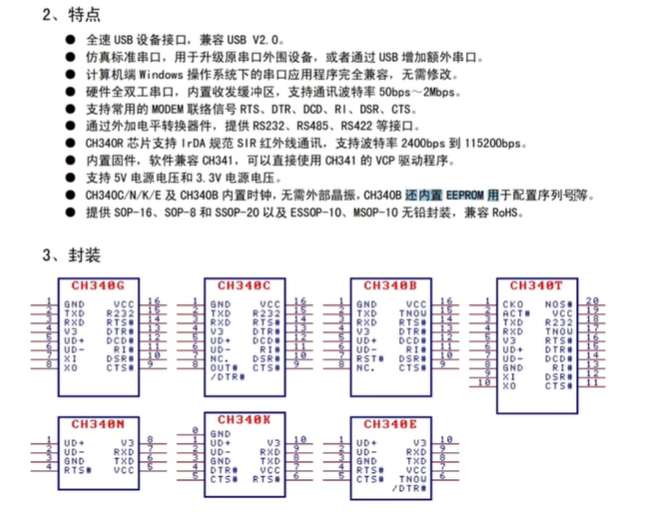

6.1 CH340N 概述

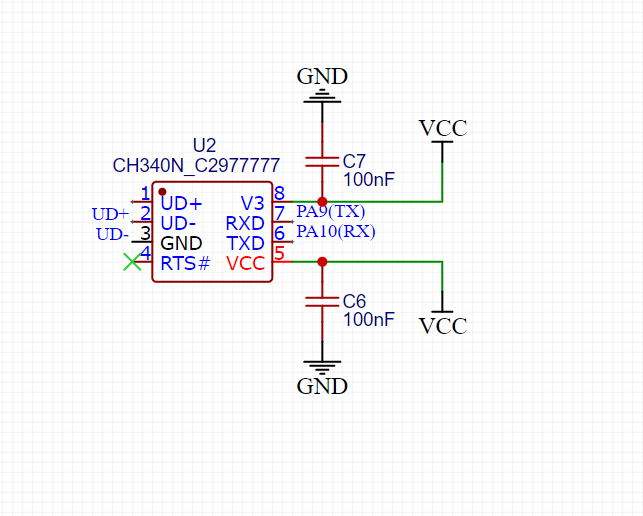

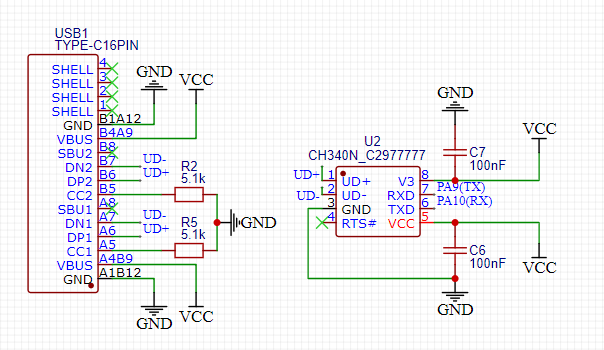

首先我们需要使用一颗 CH340N 将串口转化为差分信号,这样才能输出到 usb 中。

CH340 内置时钟,不需要外接晶振。同时 CH340 也作为一个系列出现,我们在这里使用最小封装CH340N。

手册说明,VCC 需要外接 0.1uF 的电容。同时 UD+ 和 UD- 可直接接入到 usb 无需电阻。

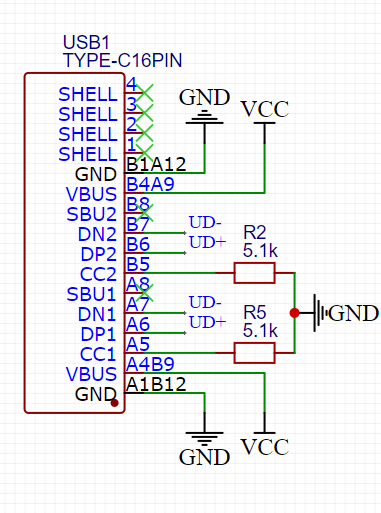

电路实现如下:

6.2 Type-C 接口

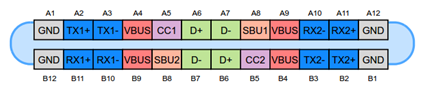

标准的 type-c 接口是 24PIN,我们不需要这么多,只需要去掉 tx 和 rx 的 16 PIN 版即可。

通过 CH340N 将数据转化为差分信号,后接入 type-c 的 A6、A7、B6 和 B6 差分口。其中最重要的 type-c 的CC1 和 CC2口,这两个数据口决定了插入方向,插入的版本等。

CC1 和 CC2 都接入下拉电阻即可配置 type-c 为 UFP 模式,即为被供电设备,下表中说明了 UFP 几种子模式。图中说的 Ra下拉是 1.2k 下拉电阻。Rd 下拉是 5.1k 下拉电阻。

我们需要使用的是 debug mode (调试模式),即 CC1 和 CC2 都接入 5.1k 下拉电阻。至于其他几种模式用途我还没有完全搞懂,不做介绍。

PCB 接线如下:因为正反有两排接口,所以无论是vcc、接地和差分均有一对口。

6.3 串口转 USB 的 pcb 设计

七 总结