- 1js动态创建html元素的方法_js 动态创建html元素

- 2【Android Studio】在Mac中更换JDK Location_mac 更换android studio 默认jdk版本

- 3唯众高职物联网应用技术专业解决方案_物联网应用技术专业群 组群逻辑

- 4mac 升级系统至10.14.4后打开vscode报git not found

- 5后端开发工程师vue2初识的学习

- 6超细节的QT设计完整界面布局的流程-新手向_qt界面设计教程

- 7【史上最全】国内外常用精品API汇总_免费新华词典api

- 8AI本地绘画软件(无需联网)+7Glatest模型+10G数据整合包_本地ai绘画软件

- 9基于NLU的智能对话系统_nlu协议

- 10机器学习笔记 - 生成对抗网络 (GAN)概述和入门示例_gan网络实例

FPGA入门系列13--异步串口通信_串口通信的异步通信格式

赞

踩

文章简介

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。

第十四章:异步串口通信

UART 串行接口简称串口,是我们各类芯片最常用的一种异步通信接口,通过串口我们就可以建立起计算机和我们实验板之间的通信和控制关系,也就是我们通常所说的上下位机通信。

串口传输特点是数据一位一位的按顺序传输,按照接口标准划分为同步通信(spi)和异步通信(uart),本章重点讲解异步通信中的 rs232 标 准。

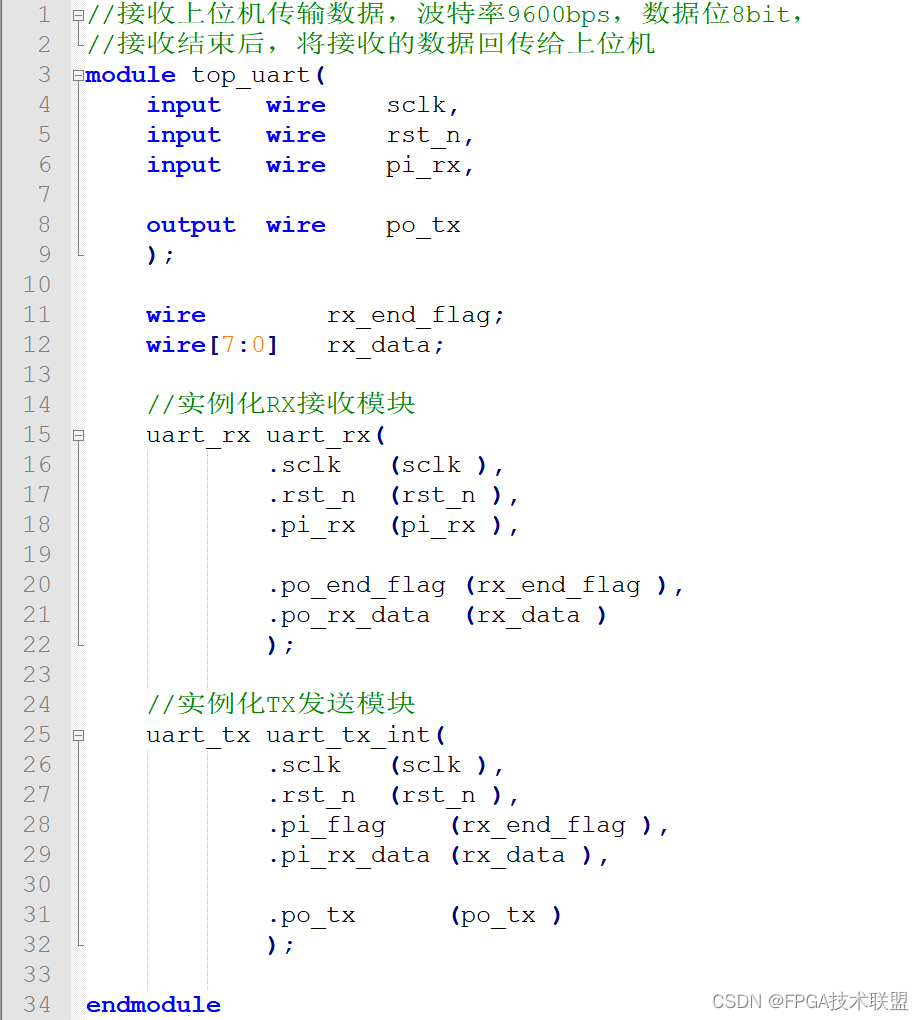

在串行通信中,rs232 是常用的一种总线,在工业控制中 rs232 总线的 rxd 和 txd 两根线经常被用到。如图 1 所示:

图1 通信结构示意

由图1可以看出,要实现 PC 机与 FPGA 之间的通信,FPGA 需要控制的其实也就是两条信号线:rxd 和 txd,分别为数据接收线和数据发送线。FPGA 可以通过两根总线做到同时收发数据,因此它是一种全双工的通信总线。

了解了 UART 的数据格式,那么,传输速率如何 控制呢?这就涉及到了一个波特率的概念:波特率是衡量数据传输速率的指针。表示为每秒钟传送的二进制位数(bit), 例如传送速率为 120 字符/秒,而每一个字符为 10 位,则其传送的波特率为 10*120=1200 波特(bit)。假设我们通过 PC 端发送一个 8bit 的数据到 FPGA 端,由于 FPGA 的接收总线 rxd 只有 1bit,所以需要将 PC 端发送的 8bit 数据分成 8 次发送,发送的频率称为比特率,比特率=波特率*N,其中 N 指的是数据的位宽,在此由于传输的数据位宽为 1,所以波特率和比特率相等。

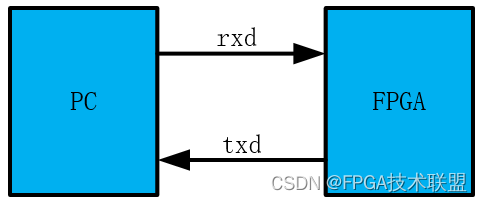

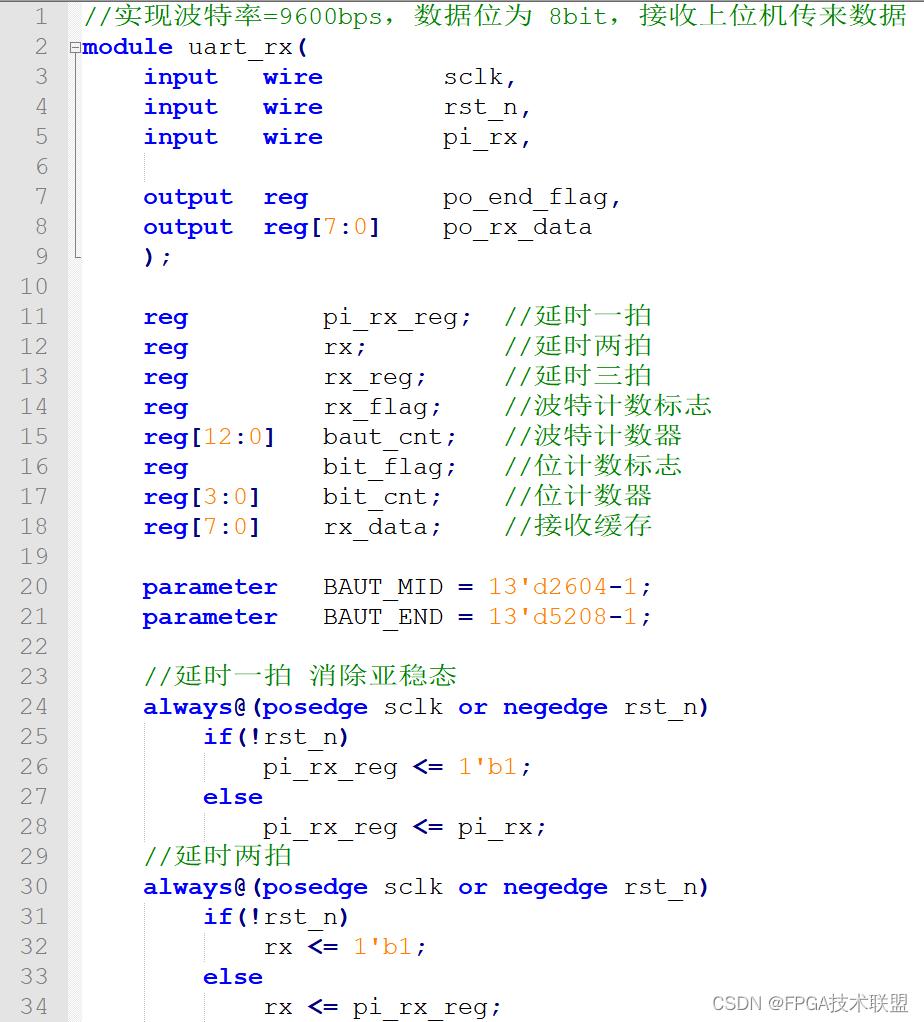

我们设定 PC 与 FPGA 间通过uart 通信的波特率为 9600bps,被传输数据的位宽 8,完成从 PC 端传输数据到 FPGA 端,FPGA 端将接收后的 8bit 数据通过 txd 返回给 PC 端,若 PC 端发送的数据与接收的数据相同,则认为传输正确。uart通信协议如图2所示:

图2 通信协议

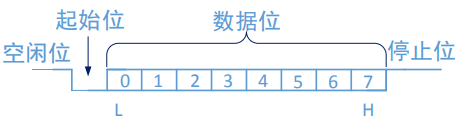

在接收数据时,采集一帧数据的中间 8 位有效位,忽略开始位与停止位;在发送数据时,将发送的并行 8 位数据转为串行数据,并添加开始位与停止位。UART 中的一帧数据为 10 位,空闲时均为高电平,在检测到开始位(低电平) 之后,开始采集 8 位有效数据位(低位在前),再将停止位置为高电平。uart数据格式如下:

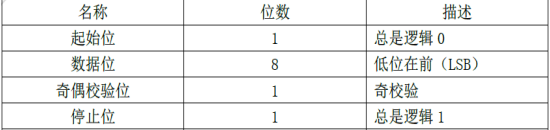

图3 uart数据格式

说明:在此实验中,无奇偶校验位,则一帧数据为十位。(奇偶校验是一种校验代码传输正确性的方法。根据被传输的一组二进制代码的数位中“1”的个数是奇数或偶数来进行校验。采用奇数的称为奇校验,反之,称为偶校验。采用何种校验是事先规定好的。通常专门设置一个奇偶校验位,用它使这组代码中 “1”的个数为奇数或偶数。若用奇校验,则当接收端收到这组代码时,校验“1” 的个数是否为奇数,从而确定传输代码的正确性。)

要求:设置一个 UART 控制器,波特率9600bps,当控制器从上位机接收到数据以后,马上将数据输出,发送回上位机。通过判断发送的数据与接收的数据是否一致来验证传输的正确性。

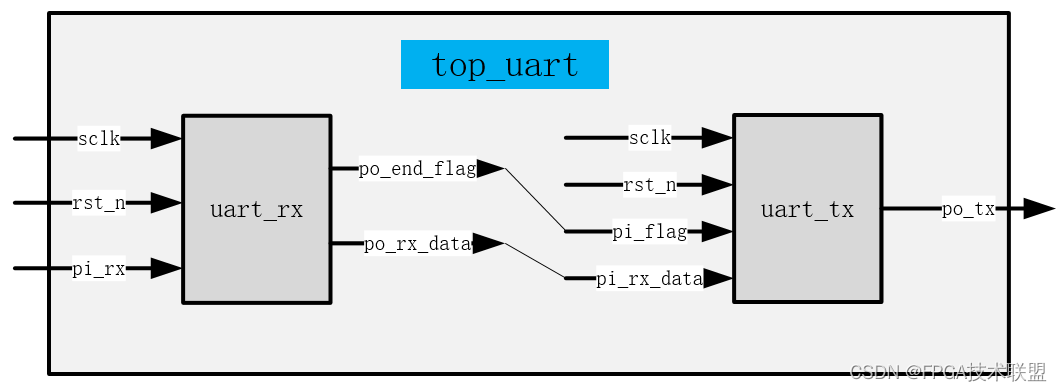

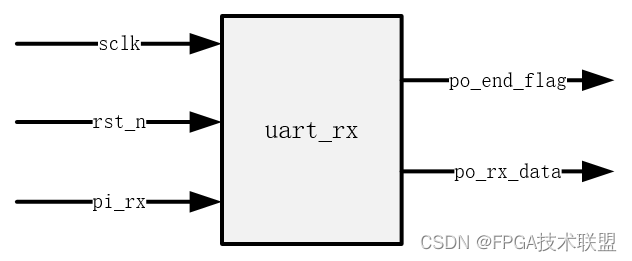

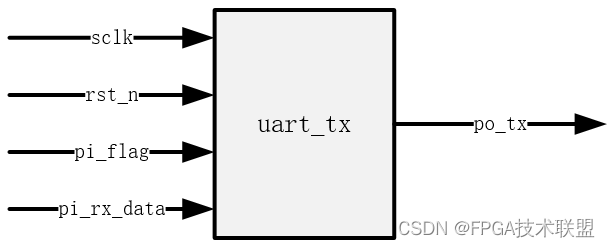

设计系统模块图如下:

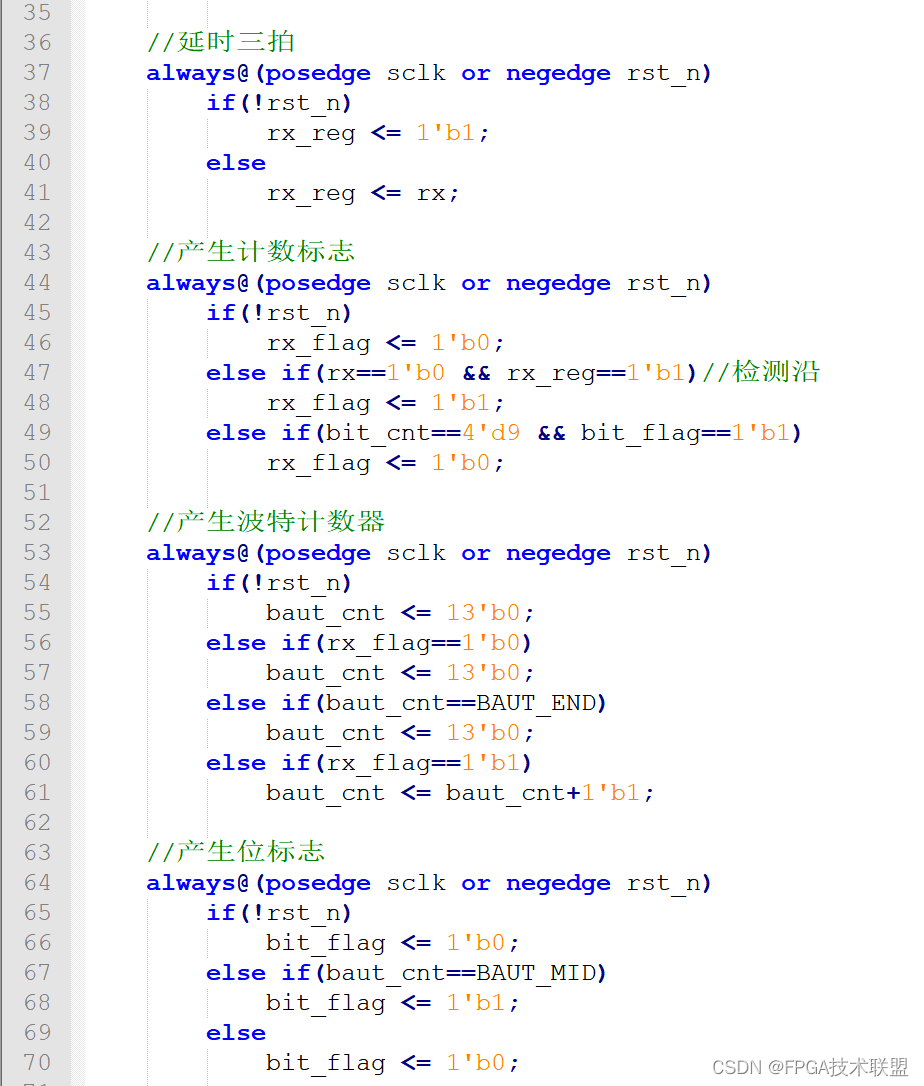

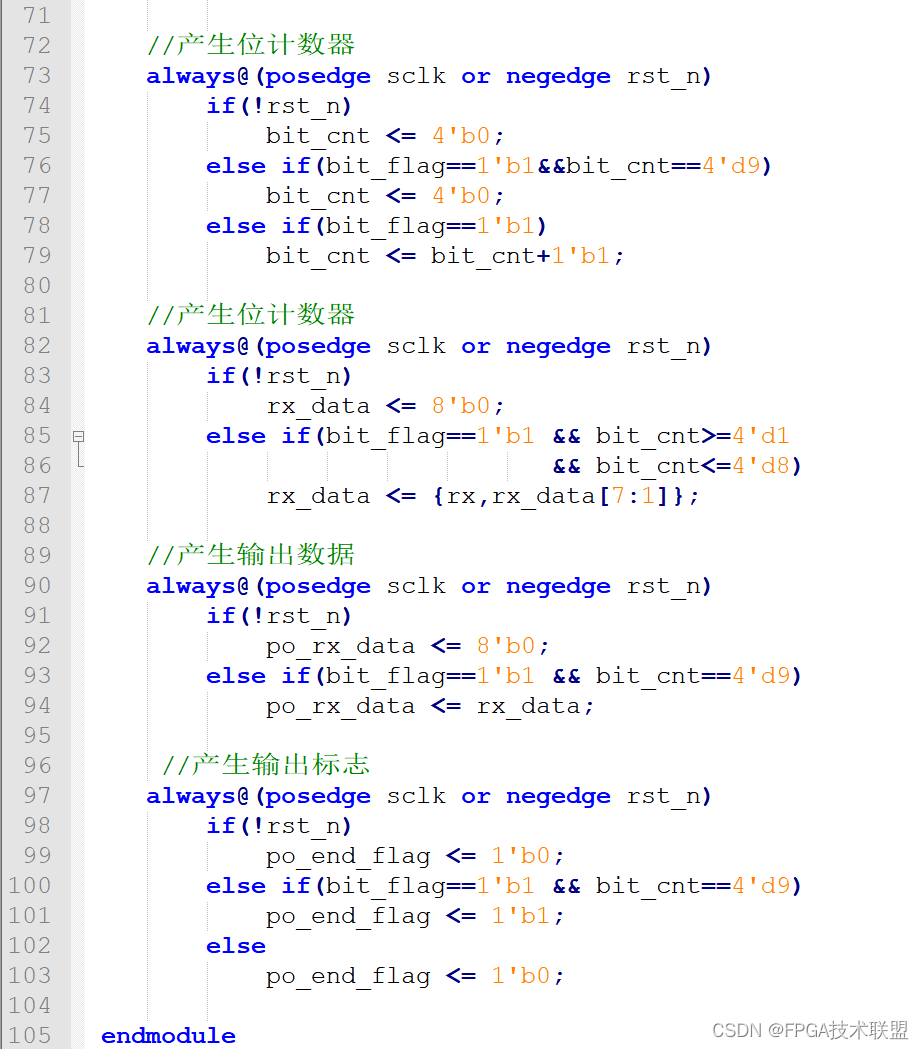

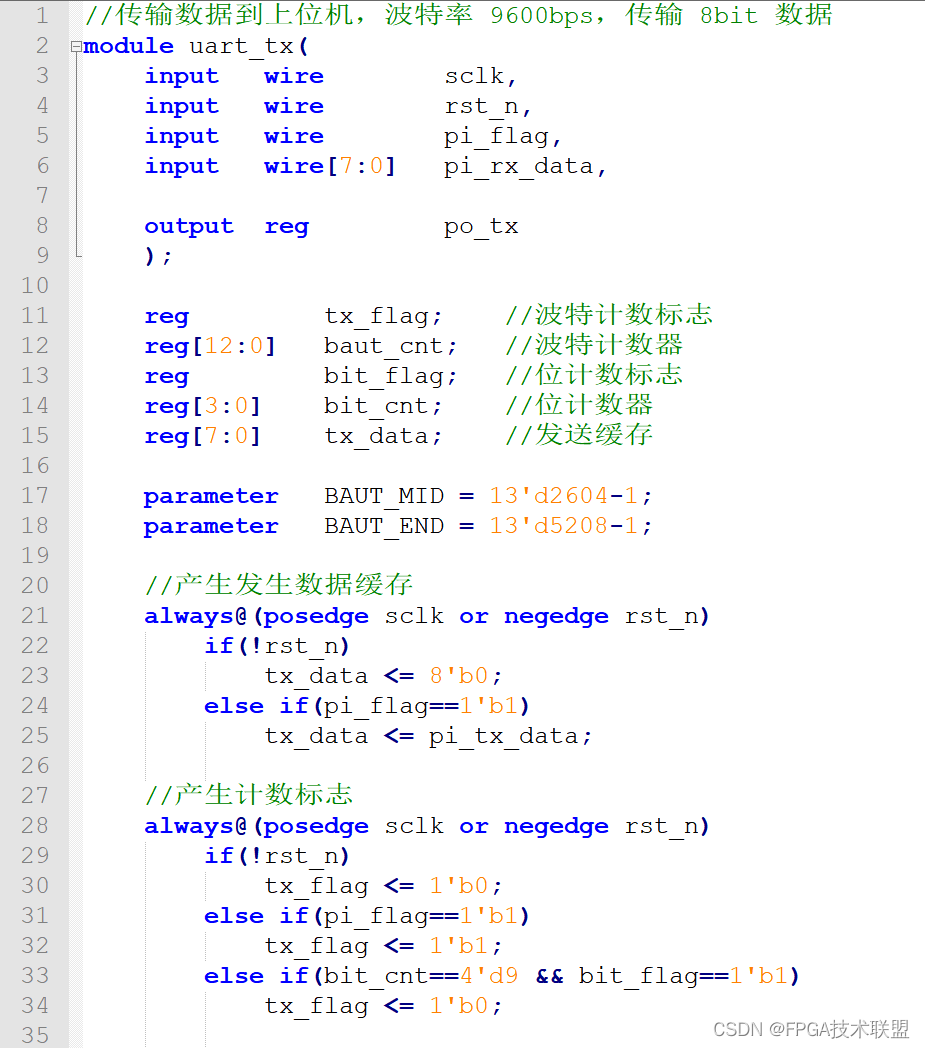

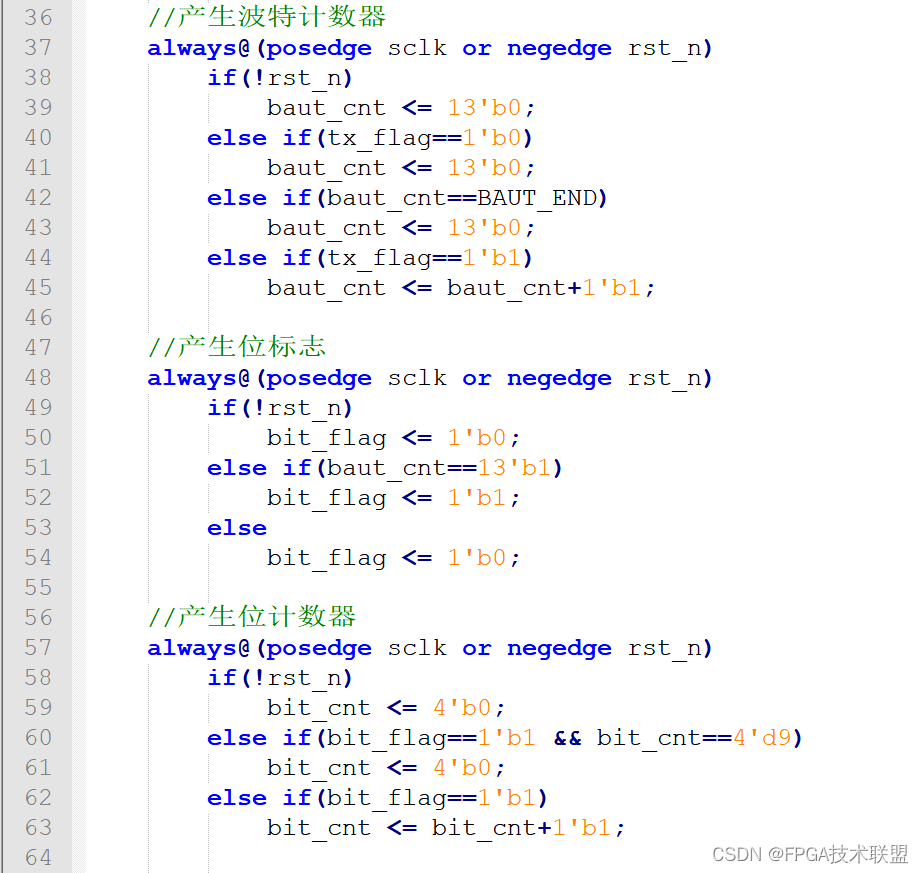

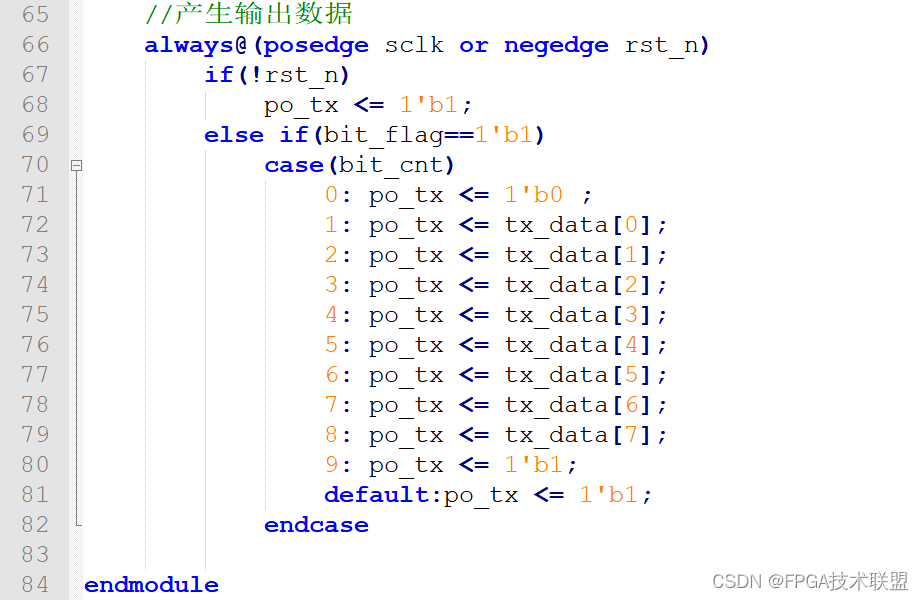

代码示例2:tx模块

代码示例3:top模块