热门标签

热门文章

- 1日常运维(1)w命令,vmstat命令,top命令,sar命令,nload命令_vmstat -w 1

- 2git pull 提示Not possible to fast-forward,无法提交也无法更新

- 3Tensorflow--MNIST分类模型_mnist模型

- 4Flink checkpoint机制_flink sql采集checkpoint

- 5大模型从入门到应用——LangChain:模型(Models)-[大型语言模型(LLMs):基础知识]_langchain model适配

- 6JDBC 设置超时时间,避免sql查询时时间过长_jdbc超时时间

- 7MySql事务_read view 匹配条件规则

- 8Oracle 数据去重_oracle去重查询

- 9深入OceanBase分布式数据库:MySQL 模式下的 SQL 基本操作_oceanbase mysql

- 10实用干货丨Eolink Apikit 配置和告警规则的各种用法

当前位置: article > 正文

逻辑设计中关于延时n拍的设计方法_芯片设计中时序设计延迟一拍

作者:空白诗007 | 2024-08-04 16:40:14

赞

踩

芯片设计中时序设计延迟一拍

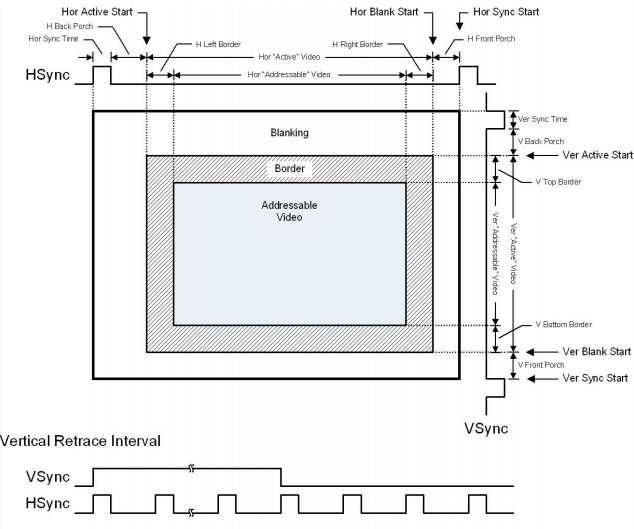

引言:在像素领域处理hsync,vsync,active,以及rgb888并行数据。因为Display Monitor Timing标准,控制信号(hsync/vsync/active)以及数据rgb888之间存在着某种特定的关系,其关系大体如下图所示:

图1 : Hsync Vsync Active 与像素之间的关系

在实际使用的过程中,像素数据需要经过buffer来缓存,逻辑设计经常使用FIFO做数据缓存,而FIFO对像素数据是有延迟的。为了达到hsync vsync与像素数据的同步,并不适合将控制信号也通过FIFO,合适的方法是将控制信号延时固定的时钟节拍,就需要有控制延时N(N>=1)个时钟节拍的逻辑控制。

下面就介绍一些关于固定时钟节拍的延时RTL实现。

方法一:触发器

当N<=2的,适合用D触发器做时钟节拍延时,这样最简便,也节省相应的逻辑资源。

- input d,

- output q,

- input clk,

- input rst_n

-

- reg q_t;

- always @ (posedge clk or negedge rst_n)

- begin

- if(!rst_n)

- q_t <= 1'b0;

- else

- q_t <= d;

- end

-

- assign

推荐阅读

相关标签