热门标签

热门文章

- 1R语言学习(用read.csv()读取csv文件)_r语言read.csv函数

- 2helm:Error: could not find tiller

- 3Linux之进程间通信_linux进程通信

- 4Hibernate在控制台打印sql语句以及参数_hibernate 打印参数

- 5AD各种布线方法总结_adpcb连线怎么倒角

- 6mtk android 4.4 audio framework 代码分析(未完成)_getpresentationposition getrenderposition

- 7最小二乘法计算CCM_ccm的计算

- 8服务器安全与网络安全监测_服务器安全监测

- 9Android平台中调用串口功能时报错:java.io.IOException: read failed: EBADF (Bad file descriptor)_java.io.ioexception: bad file descriptor

- 10Unity 禁用 多点触控

当前位置: article > 正文

关于异步FIFO的时钟同步问题分析_异步时钟延迟两个时钟

作者:笔触狂放9 | 2024-03-07 17:30:47

赞

踩

异步时钟延迟两个时钟

1.时钟同步原理

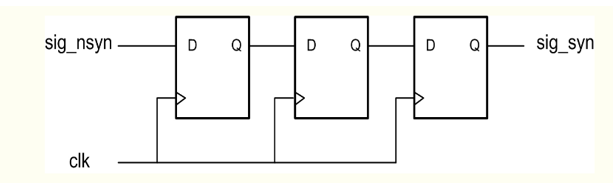

通过增加两个寄存器来实现时钟同步

对于fifo来说,无论是写地址在读时钟下同步,还是读地址在写时钟下同步,被同步地址都会是延迟两个时钟周期之前的地址,所以在进行比较判断的时刻,参与判断的同步地址总是小于等于当前时刻的真实地址。那么,

对于判断满信号full,由于满信号判断条件为写地址是否追上读地址,即rd_addr - wr_addr == 0, 在判断条件中,rd_addr 应该是领先的一方,否则将会出现超前写数据的情况,所以应该将读地址同步到写时钟下。同步后的判断条件则变为:rd_addr_syn - wr_addr == 0,由于rd_addr_syn <= rd_ addr(当前时刻),所以不会出现写数据超前情况。当rd_addr_syn < ad_addr时,此时为“虚满”状态。

对于判断空信号empty的情况,与上面分析类似 ,由于判断条件为wr_addr - rd_addr == 0,那应该将写地址同步到读时钟下,才不会出现超前读数据的情况,当然也会出现“虚空”状态。

还有就是。fifo满是对于写操作有用的(因为满了就不可以写了),所以满信号必须同步到写时钟之下。而fifo空是对读操作有用的(因为空了就不可以读了),所以空信号必须同步到读时钟之下。

写完之后看到一篇解释特别好的博客,链接:

https://blog.csdn.net/moon9999/article/details/77943407

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/206711

推荐阅读

相关标签