- 1AI聊天伴侣的语料采集大揭秘:OpenCV如何轻松识别聊天图片?_图像识别聊天框

- 2开源项目——ROSECHO 中文ROS语音交互模块(一)_ros语音控制命令前往指定地点

- 3体感游戏开发:体感游戏常用技术

- 4Edge-TTS 语音朗读

- 5国考【行测】类比推理真题分析——2023.12.27更新_显示屏计算机手机类比

- 6【华为机试】2024年真题C卷(c++)-机器人搬砖_华为od 机器人搬砖,一共有n堆砖存放在n个不同的仓库中,第i堆砖中有bricks[i]块砖

- 7【EduCoder答案】git相关实训答案_#请在下面的begin/end内填写语句以将远程版本库clone到本地 #********** be

- 8【前沿技术杂谈:NLP技术的发展与应用】探索自然语言处理的未来

- 9正样本和无标签学习(PU Learning):使用机器学习恢复数据的标签

- 10VRRP实验(eNSP)_ensp vrrp

RIFFA架构_riffa详解

赞

踩

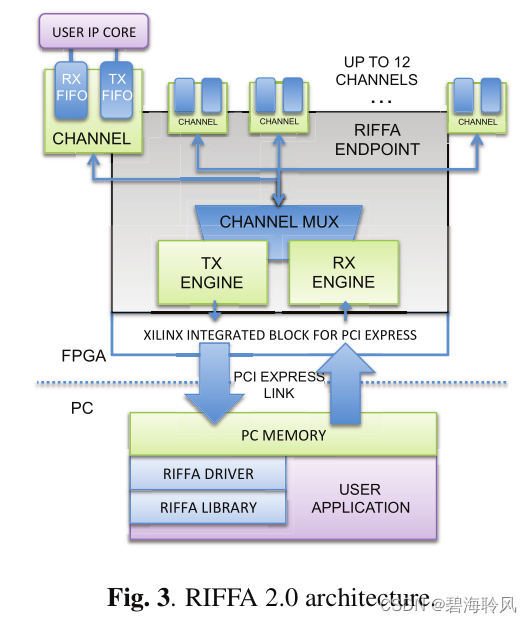

用户侧通过Channel和Riffa交联,Channel是被用来处理异步时钟域,其含有FIFO来接收发送数据。

RX引擎用来提取和多路分解收到的PCIe负载数据。TX引擎用来将负载数据格式化为PCIe包,并且提供对PCIe链路的多路复用访问。

pcie链路配置决定了数据总线宽度。这个宽度可以是32,64,128bit。Riffa对其都支持。但是不同的宽度在提取和格式化pcie数据时要求不同的逻辑。

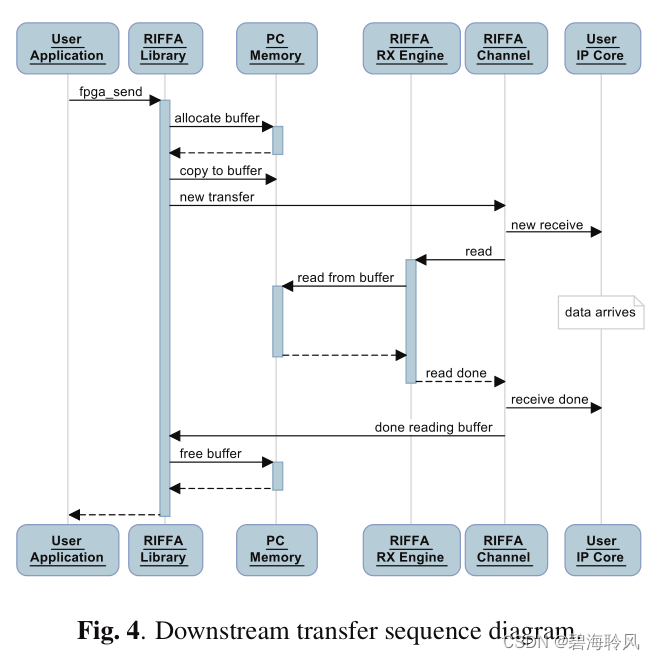

上层应用调用用户库函数fpga_send,线程进入内核驱动并且获得了一块预分配的buffer来暂存用户数据。一旦获取了buffer,数据就会被复制到buffer中,以便Endpoint可以访问它。

对Endpoint配置空间的写入触发一个新的下行传输。写入包含len、offset、last参数,以及包含数据的buffer地址。

数据通过大量PCIe TLP包被从缓冲区读取到通道中。如果数据大小超过了单个buffer,driver会获取另一个buffer,将数据拷贝到新的buffer中。

为了提高传输性能,Endpoint只要认为它需要,就请求下一个buffer。这个流程持续直到所有数据被传输。

Endpoint释放最后一个buffer标志到驱动程序的传输结束。然后,驱动程序释放最后一个buffer并解锁用户线程。

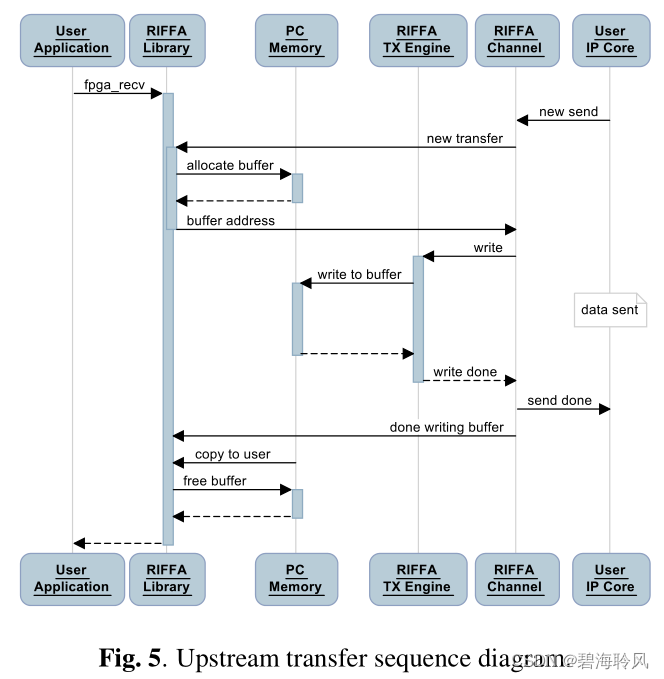

Upstream transfer的主要不同在于,Endpoint Core 向内核buffer写入数据,由驱动将数据拷贝到用户提供的字节数组中。

此外,Upstream transfer的发起者是User core,而不是软件线程。这就意味着数据传输可以在上层应用调用fpga_recv之前开始。

内核缓冲区在系统启动时预先分配,以避免动态内存分配造成的延迟