- 1腾讯云网络云产品介绍第三章-负载均衡服务_腾讯云 弹性负载均衡

- 2Mac M1/M2 安装Tensorflow教程_mac在已经创建好的环境上如何再安装tensorflow

- 3vue回调函数中调用data中的数据的解决方法_vuedata调用data里面数据

- 4[刷机] 9008 刷机救砖笔记

- 5Kotlin 协程:深入理解 ‘lifecycleScope‘_kotlin lifecyclescope

- 6IDEA项目如何上传至GitHub(保姆级教程)_idea怎么上传github

- 71235813找规律第100个数_数学基础知识点类总结,解题规律典型应用题可收藏

- 8使用TortoiseGit如何回退代码版本_tortoisegit回退到指定版本

- 9ARM架构下部署docker_dockerarm 18.09.0.200 版本下载

- 10神经网络与深度学习(一)_神经网络 各模块贡献度分析

【小技巧】vivado中功能仿真和时序仿真_vivado时序仿真

赞

踩

目录

1.1功能仿真和时序仿真概述

Vivado是Xilinx公司的一款集成开发环境(IDE),包括用于FPGA设计、仿真和验证的各种工具。在Vivado中进行功能仿真和时序仿真的操作方法如下:

功能仿真:

操作方法:

a. 打开Vivado,创建一个新的工程。

b. 在工程中添加设计文件和仿真文件。

c. 在仿真文件中添加仿真测试向量。

d. 运行仿真。

功能仿真主要用来验证设计的逻辑功能是否正确。在功能仿真中,输入信号被赋值给设计的输入端口,然后仿真器会模拟设计的逻辑,输出信号被读取并与预期的输出进行比较。如果输出与预期的输出相同,则说明设计的逻辑功能正确。

时序仿真:

操作方法:

a. 打开Vivado,创建一个新的工程。

b. 在工程中添加设计文件和约束文件。

c. 运行时序分析,生成时序报告。

d. 运行时序仿真。

时序仿真主要用来验证设计的时序是否正确。在时序仿真中,输入信号被赋值给设计的输入端口,然后仿真器会模拟设计的逻辑,并计算出每个时钟周期的输出信号。时序仿真可以检测出时序问题,如时钟频率过高或过低、时序路径过长等。

功能仿真和时序仿真是验证FPGA设计的重要步骤,它们能够分别验证设计的逻辑功能和时序正确性。对于实际的FPGA开发过程,通常需要先进行功能仿真,再进行时序仿真。

1.2vivado中功能仿真和时序仿真操作方法

在vivado中我们一般需要首先对程序进行功能仿真,其操作方法如下:

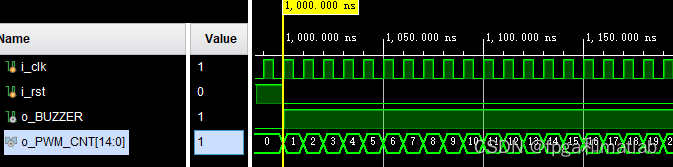

此时,功能仿真的效果如下所示:

下一步,如果有需要,我们对程序进行时序仿真,此时,操作步骤如下:

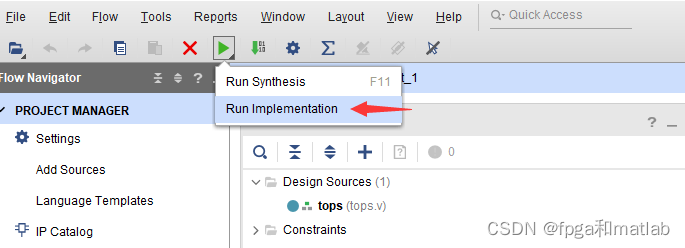

先进行综合布局布线操作:

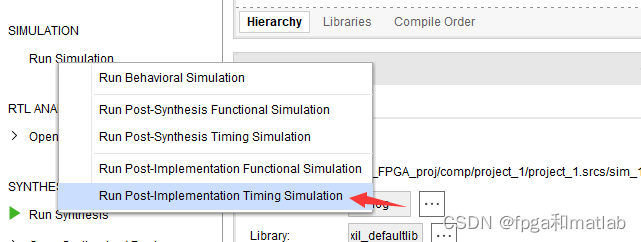

然后进行时序仿真,操作如下:

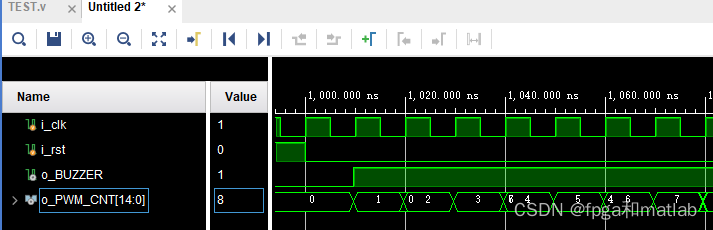

可以看到,在完成布局布线之后,可以点击时序仿真,仿真结果如下:

时序仿真和功能仿真区别,我们将上述仿真结果放大可以看到:

在两个数据的变化中间,会有一个0不稳态输出。这个也是实际FPGA开发过程中需要主要的问题。