热门标签

热门文章

- 1【实例分割】转换YOLO格式标注至COCO格式JSON

- 2用离散数学知识对AI最难替代的职业进行数学建模,推导证明出最难被AI替代的职业是什么_数学建模ai

- 3华为策略路由引流旁挂防火墙_防火墙旁挂配置案例

- 4unbuntu里面没有ip_抖音怎么打造个人ip,如何打造抖音个人IP

- 5腾讯TDSQL:带你认识真正的金融级自主可控分布式数据库_建立本地金融数据库软件

- 6tx2 ubuntu1804 opencv3.4 cuda10 compile_qwebphandler_p.h:49:10: fatal error: webp/decode.h

- 7华为安全-防火墙-双向NAT_华为防火墙双向nat配置

- 8云计算与软件即服务(1)

- 9计算机网络_给数据分节进行排序,并使用累计确认保证数据的顺序不变和非重读

- 10软件工程-小米便签部署,代码结对泛读_小米便签github项目

当前位置: article > 正文

24、江科大stm32视频学习笔记——SPI通信协议原理_江科spi模式1

作者:笔触狂放9 | 2024-04-20 12:44:34

赞

踩

江科spi模式1

一、SPI简介(serial Peripheral Interface(串行 外设 接口))

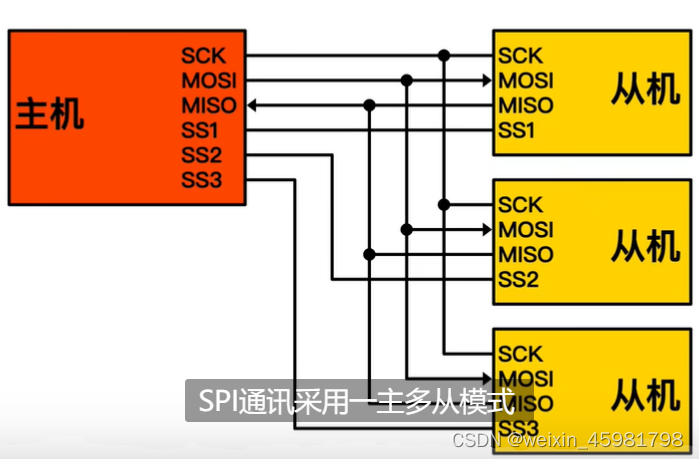

1、电路模式(采用一主多从的模式)、同步,全双工

- 所有SPI设备的SCK、MOSI、MISO分别连在一起

- 主机另外引出多条SS控制线,分别接到各从机的SS引脚

- 输出引脚配置为推挽输出,输入引脚配置为浮空或上拉输入

- 推挽输出:高低电平都有很强的驱动能力,使得SPI引脚信号的下降沿和上升沿非常迅速

- (IIC因为要实现半双工,经常切换输出输入,IIC又要实现多主机的时钟同步和总线仲裁,若使用推挽输出任意电源短路)

- SPI的MISO可能有冲突,一位内主机是输入,三个从机都是输出,若三个从机始终是推挽输出,势必会导致冲突。

故SPI有个规定:

当从机的SS引脚为高电平时,即从机未被选中,其MISO引脚必须切换成高阻态,高阻态相当于引脚断开,不输出任何电平,这样可以防止一条线有多个输出,导致电平冲突问题

SS为低电平时,MISO才允许变为推挽输出(切换在从机中,不需要关注)

2、4条信号线

- SS(片选信号线(理解为从机选择线)、Slave Select):单片机通过给片选信号线高低电平来确定哪一个从机通讯,一般当这根线为低电平时,片选才有效

- SCK(时钟信号线、Serial Clock):主设备产生

- MOSI(发送信号线、Master Output Slave Input):主设备从MOSI输出数据,而从设备通过MOSI接收数据

- MISO(接收信号线、Master Input Slave Output):主设备通过这根线接收数据

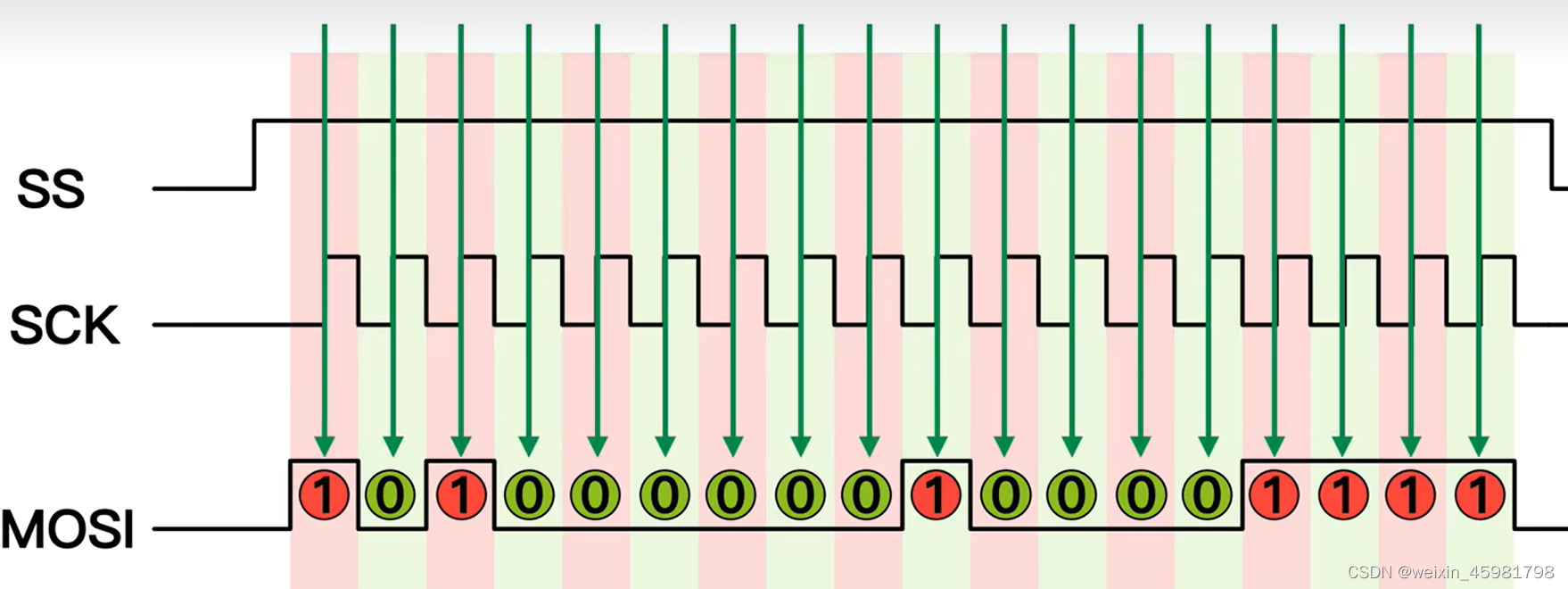

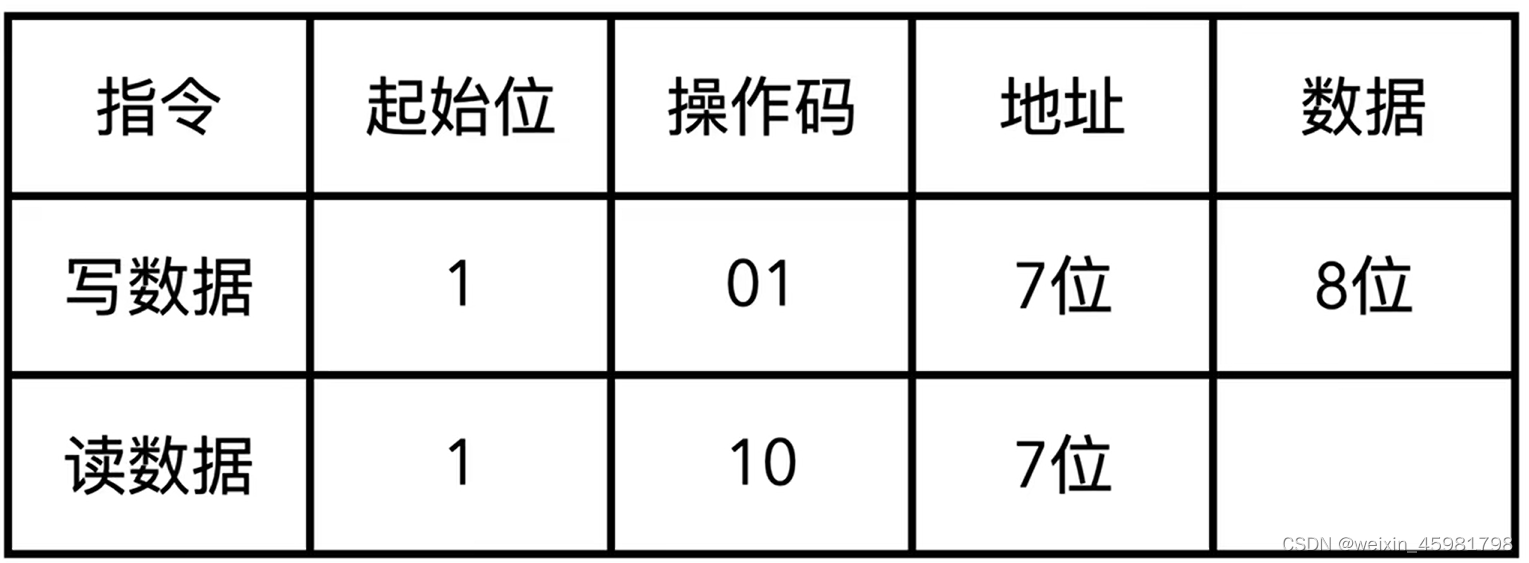

3、通信过程

- 写数据:在地址为0x01处写数据0000 1111

- 给存储器发送起始位1,然后发送操作位01,然后地址0x01,数据0000 1111,则存储器的地址0x01就会保存0000 1111数据。

- 读取数据:

- 首先先写起始位1,然后操作码10,最后传递要取的地址符号

- spi是串行同步通信,因此数据线要和时钟线配合使用,才能给存储器发送数据

- 93C46是一个EEPROM存储器,有1024位存储空间,也就是128个字节,每个字节都有属于它的地址,刚好是7位数的二进制数

- SSI大部分时候是低电平有效,但在93C46中是高电平有效

- 四种采集模式:

- 1、只有在上升沿的时候采集数据(空闲时钟低电平)

- 2、只有在下降沿的时候采集数据(空闲时钟低电平)

- 3、只有在上升沿的时候采集数据(空闲时钟高电平)

- 4、只有在下降沿的时候采集数据(空闲时钟高电平)

4、I2C和SPI的比较

(1)I2C

- I2C在硬件和软件电路设计都比较复杂,但可在消耗最低硬件资源的情况下,实现最多的功能

- 由于I2C开漏外加上拉电阻的电路结构,使得通信线高电平的驱动能力比较弱,这会导致通信线由低电平变到高电平的时候,上升沿耗时比较长,限制了IIC的最大通信速度

- 故IIC的标准模式只有100kHz的时钟频率,快速模式只有400kHz

(2)SPI

- SPI传输更快,没有严格规定最大传输速度,最大传输速度取决于芯片厂商的设计需求,即看手册

- SPI的设计比较简单粗暴,实现的功能没IIC多,硬件开销比较大,通行线的个数比较多哈,并且通行过程中,经常会有资源浪费的现象

- SPI的风格:最简单最快速的完成任务,没有应答机制

二、软件读写W25Q64

1、W25Q64介绍

W25Q64是一个Flash存储器芯片,内部可以存储8M字节的数据,并且是掉电不丢失,若在项目中需要存储大量的数据,可以考虑此芯片。

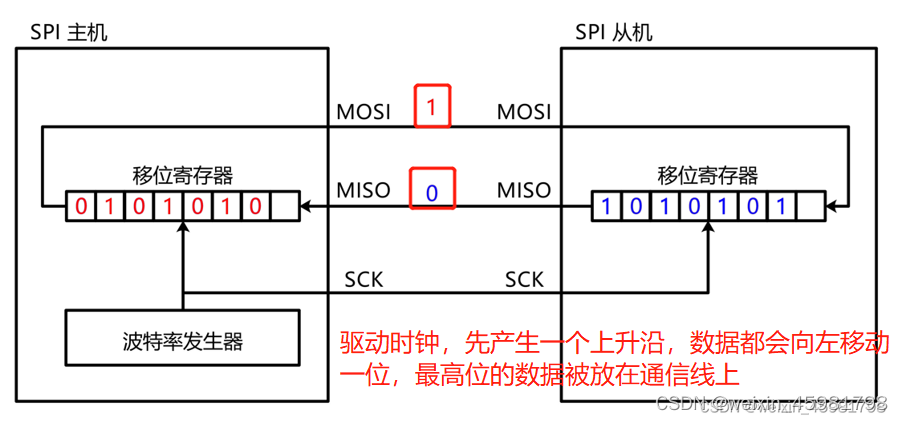

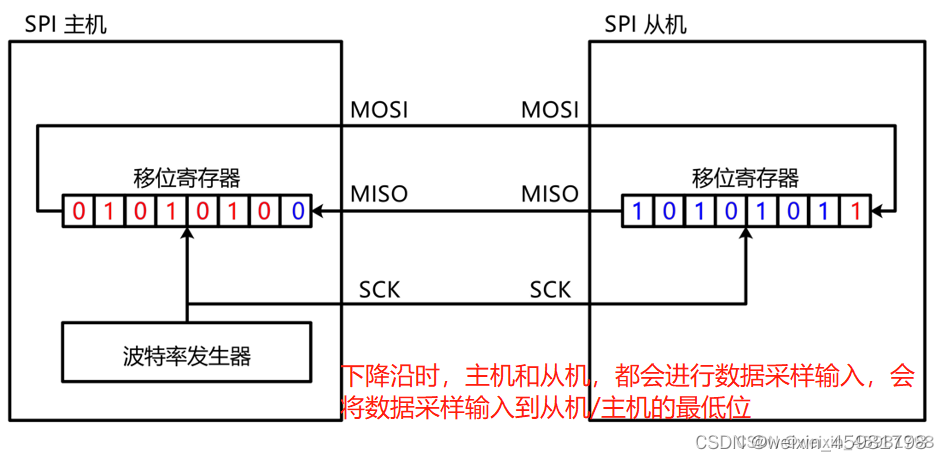

2、移位示意图

(1)SPI的基础是交换一个字节

(2)SPI时序基本单元

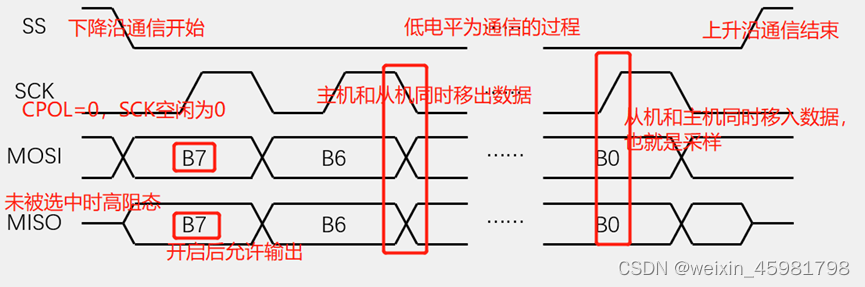

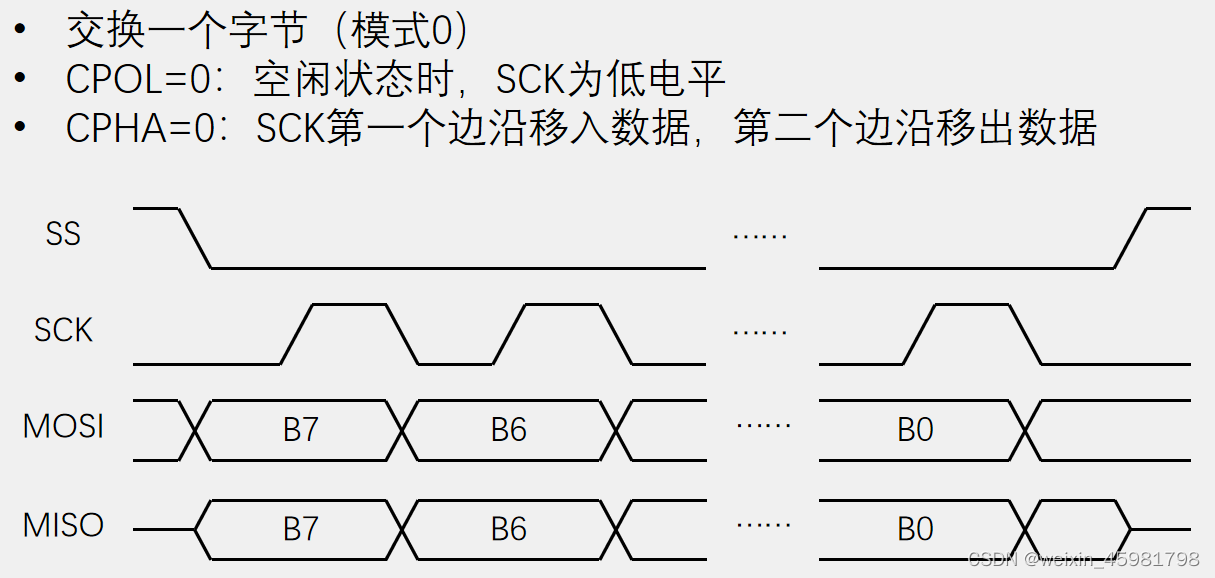

交换一个字节(模式0)(应用最多)

CPOL=0(时间极性):空闲状态时,SCK为低电平

CPHA=0(时钟相位):SCK第一个边沿移入数据,第二个边沿移出数据四个模式

模式0:CPOL=0:空闲SCK为0,CPHA=0:SCK第一个边沿移入数据,第二个边沿移出

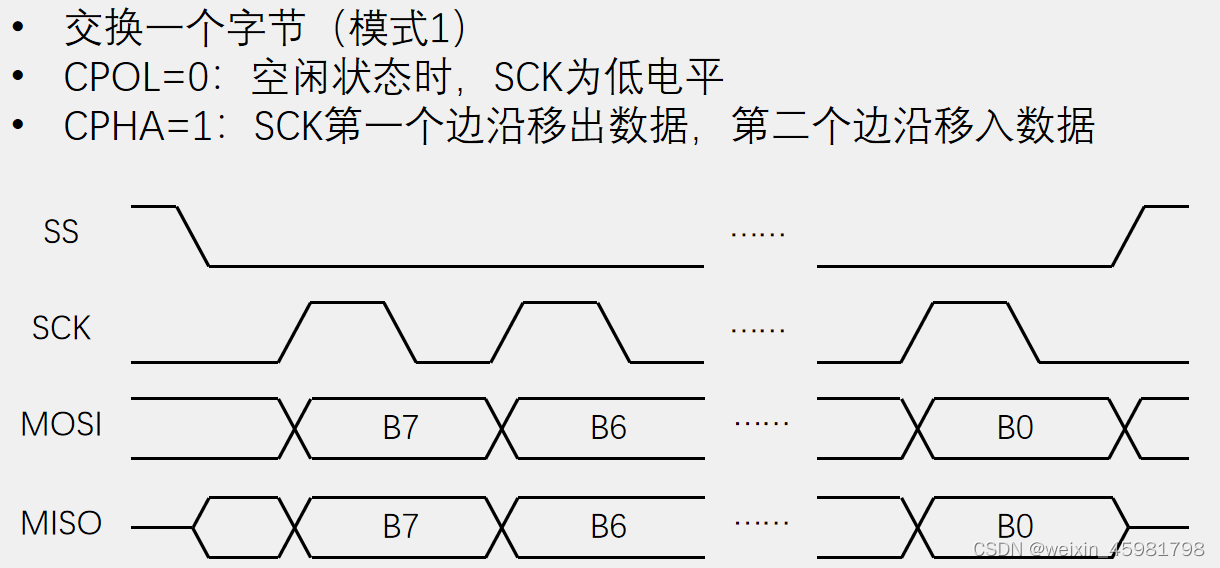

模式1:CPOL=0:空闲SCK为0,CPHA=1:SCK第一个边沿移出数据,第二个边沿移入

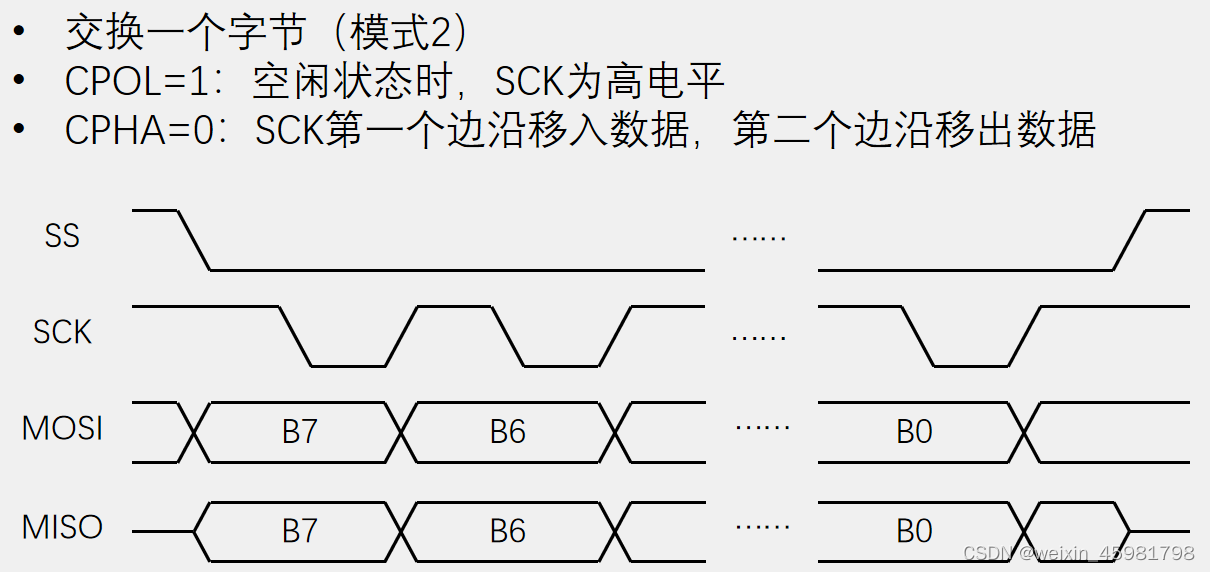

模式2:CPOL=0:空闲SCK为1,CPHA=0:SCK第一个边沿移入数据,第二个边沿移出

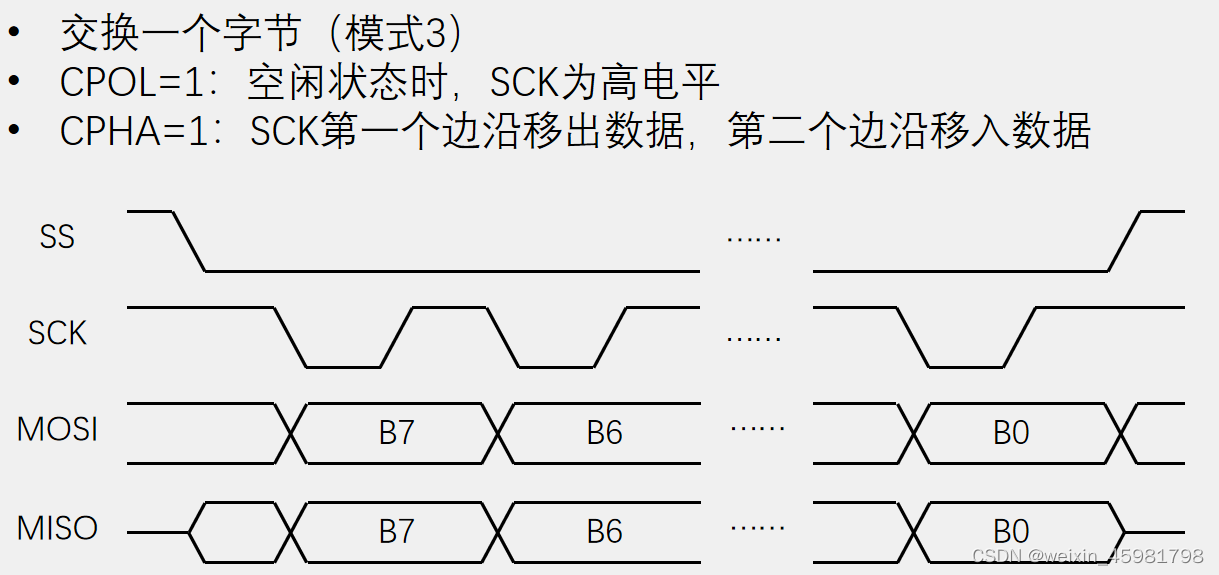

模式3:CPOL=0:空闲SCK为1,CPHA=1:SCK第一个边沿移出数据,第二个边沿移入

上述MOSI、MISO为两条线表示发送的既有可能是高电平又有可能是低电平

(3)SPI时序

1、发送指令(实现向从机的0x123456的地址上发送0x55)

(1)主机向SS指定的设备发送指令码0x06(写使能的指令)

(2)发送指令0x02,表示要写入

(3)指定地址0x123456:发送0x12(高位地址)、0x34、0x56(低位地址)

(4)发送指定数据0x55

2、指定地址读数

(1)主机向SS指定的设备发送指令码0x06(写使能的指令)

(2)发送指令0x03,表示要读取

(3)指定地址0x123456:发送0x12(高位地址)、0x34、0x56(低位地址)

(4)主机为高电平,从机发送数据

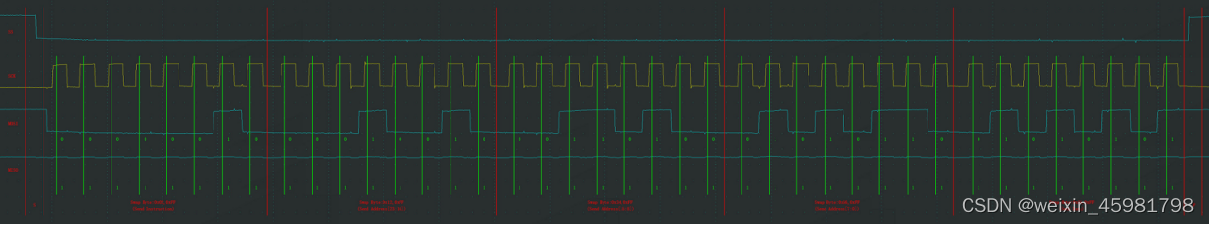

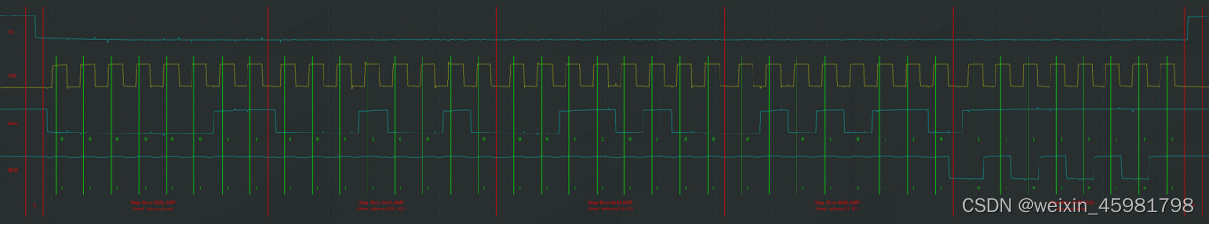

附:4种模式的图

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/457364

推荐阅读

相关标签