《数字集成电路物理设计》学习笔记:第一章_集成电路物理设计方法(持续更新中)_数字集成电路物理设计pdf百度云

赞

踩

参考书籍:

目录

第1章 集成电路物理设计方法

《数字集成电路物理设计》学习笔记:第一章_集成电路物理设计方法(持续更新中)-CSDN博客![]() https://blog.csdn.net/qq_36045093/article/details/136900673?spm=1001.2014.3001.5501第2章 物理设计建库与验证

https://blog.csdn.net/qq_36045093/article/details/136900673?spm=1001.2014.3001.5501第2章 物理设计建库与验证

第3章 布图规划和布局

第4章 时钟树综合

第5章 布线

第6章 静态时序分析

第7章 功耗分析

第8章 信号完整性分析

第9章 低功耗设计技术与物理实施

第10章 芯片设计的最终验证与签核

前言

集成电路数字系统芯片的设计,从系统设计、功能验证和逻辑综合到物理实施,每阶段的重要性已经越来越被人们认识。然而,关于集成电路设计,目前非常缺少侧重于工程内容的教材和参考书籍,尤其是关于物理实施过程、设计方法和设计流程,以及实施细节、相互间的内在依赖关系等方面。近十年来,从深亚微米到纳米设计中出现了许多新技术方案和设计流程,人们迫切需要有关专著进行讲解。

今天的数字集成电路设计显然要比十年前或者五年前复杂得多,过去人们将数字集成电路的物理设计与实施简称为后端设计,或被解释为逻辑综合、布局与布线三步曲。事实上,在当代的集成电路设计中,这三步工作更加依赖于EDA工具的自动化,工程师要花费更多的时间分析设计数据、设计方案和设计结果,不断地调整布局与布线中的各种参数,以使设计达到时序收敛。

作者试图将已经广泛应用的物理设计方法以及纳米设计中面临的一些问题和新的设计思路和设计方法,结合从事过的设计和多年的EDA培训及教学经验,编著成书。希望能补充这一学科的部分空白,和有志于进人这一实践领域的专业工程师共享,也希望本书能成为具有一定物理设计基础和想从事物理设计的工程师有用的参考书。

第1章 集成电路物理设计方法

集成电路的设计工程绝对不同于软件设计或机械工程,它不希望设计者程序化或机械化地按照流程图去处理复杂的芯片设计,而是首先需要了解当今集成电路设计的复杂性和挑战性(见1.1节),再去参考相关的设计流程(见1.2节),在实施过程中不断理解、分析并解决其中出现的问题,使设计尽快得到收敛(见1.3节)。

本章将依次讲解这些内容,并将近年来集成电路设计中人们关心的与设计复杂性相关的数据库方法(见1.4节)在本章末尾介绍,以协助读者理解复杂的设计本身与设计工具和环境的相互关系。

1.1 数字集成电路设计挑战

集成电路的设计技术不断改进,对工程师提出了艰巨的技术挑战:

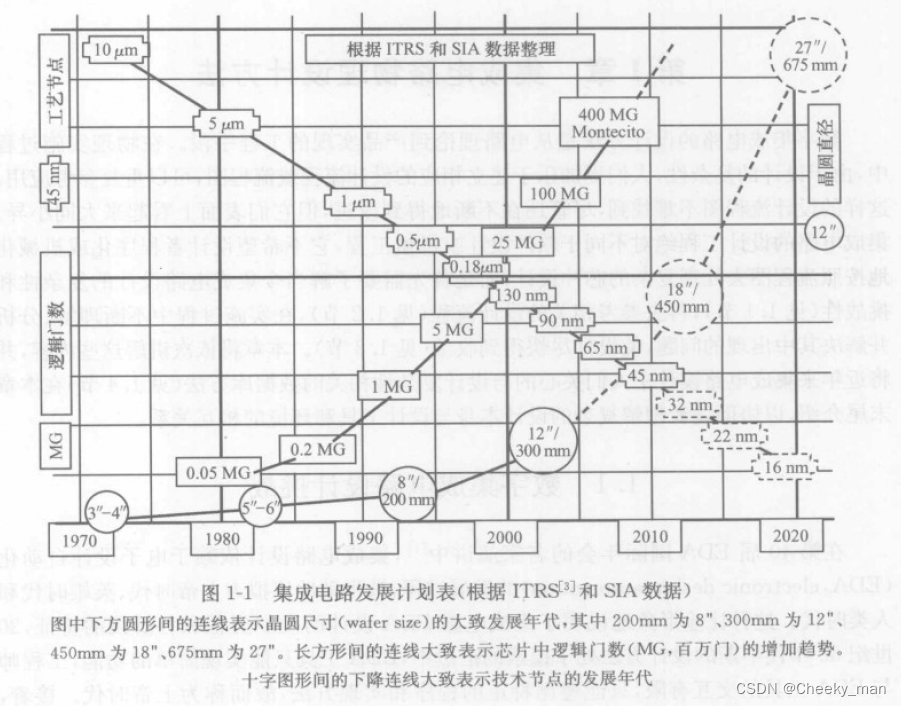

- 芯片上的晶体管数量按照摩尔定律(Moore law)的发展已达到10亿个;

- 晶圆尺寸从3"(英寸,1英寸=2.54厘米)到目前的12";

- 晶体管的特征尺寸或者技术节点(technologynode)已经发展到65nm并已建立45nm 设计流程。

1.2 数字集成电路设计流程

集成电路从RTL到GDSI的设计发展过程又被分作三个“I”年代,它们是发明、实施和整合(innovation,implementation,integration)。

发明年代包括布局布线的基本算法、时序分析和逻辑综合(logicsynthesis)的发明;

实施年代开始于FPGA中门阵列的实现,ASIC设计中同等高度标准逻辑单元库的设计,它们使得EDA的方法得到充分的发展和应用;

当集成电路设计变得越来越大,即出现了在RTL和逻辑综合时,先将设计经过分配(partition)变成模块化(module)的设计和优化方案,在布局布线时采用自底向上的堆砌法(bottom-up),这也是一种展平的设计方法(见1.2.1节)。所有模块完成后,最后再将它们整合在一起。

在布局布线时的另外一种模块化设计方案则是和综合相似的方案,实行自上向下(top-down)分配,变成模块化再将它们整合在一起(见1.2.3节)。

在布局布线阶段,无论是自底向上或自上向下进行设计,都需要较长周期才能完成一轮的实验方案。因此,结合两者的特点,人们又提出了第三种快速实施方案,称之为硅虚拟原型设计(见1.2.2节)。为了便于初学者理解,我们将先介绍自下向上,而后介绍硅虚拟原型设计,最后介绍自上向下的实施方法。不管采用哪一种实施方案,为了适合处理复杂的设计,EDA 工具也随之按照整合的方案在发展。因此,各种工具是整合式的,它们是模块化的,它们相互间的匹配应用具有延续性和递增性。

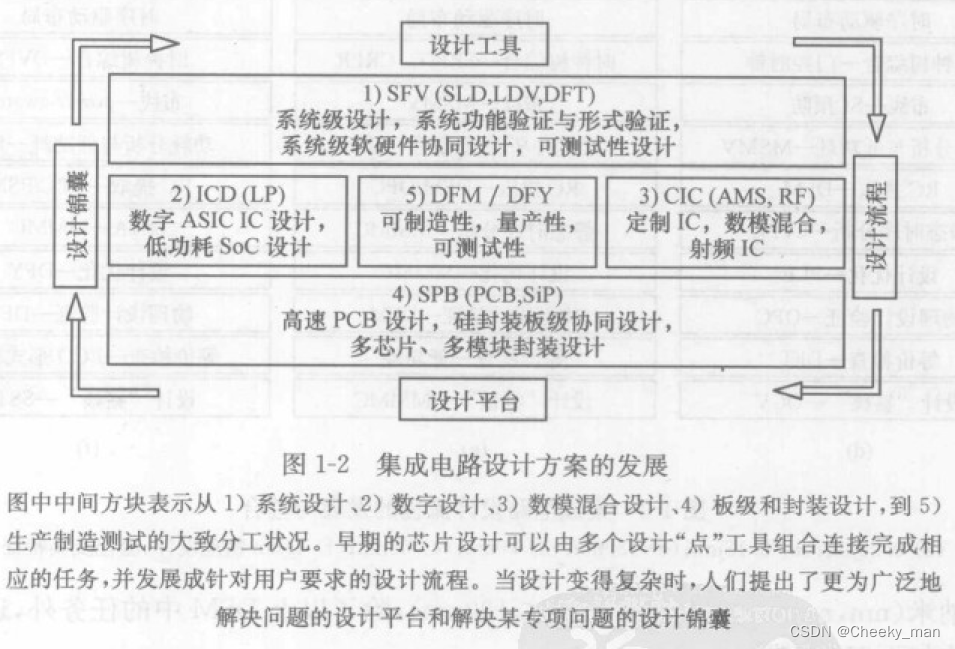

早期的集成电路物理实施方法只能由工程师通过指令窗(CIW,commandinwindow)读写数据,并通过几个引擎分别进行设计的布局布线处理,这几种引擎也叫做“点工具”(point tools)。将点工具串接在一起,添加了图形界面(GUl,graphic user interface),使得用户设计变得极为直观,根据设计类型(数字、模拟、数模混合)从而建立了不同的设计流程(flows)。为了在不同设计流程间的数据交换方便,又将设计流程扩展建立了多个设计平台(platforms)。当代的片上系统芯片(SoC,system-on-chip)的设计需要由设计公司(fabless)、IP供应商、晶圆代工厂(foundry)和EDA供应商在设计生产链(design chain)上共同配合。这些复杂的方法和概念,有时使得初学者无所适从,,因此人们又提供了设计“锦囊”(工具箱,kits)供选择。

图1-2是从点工具到设计工具箱之间的示意图。

对于深亚微米(DSM,deep sub-micron)芯片(例如,0.35um、0.25um、0.18um)的物理实施,在设计中要重点解决的任务和内容有如下三点:

(1)解决时序驱动设计(TDD,timing-driven design)的方法

(2)防止工艺天线效应(PAE,process antenna effect)。

(3)进行信号完整性(Sl,signal integrity)分析。

名词解释:

IPO:In-Place Optimization,原地优化

DRV:Design Rule Violation,设计规则违反

BC:Best-Case,最佳条件

WC:worst-case,最差条件

CWLM:定制(custom)WLM

partition:分割,分块

MSMV:multi-supply,multi-voltage,多供电电压

PLE:physical layout estimator,物理布图参数

CMP:chemical mechanical polishing,化学机械抛光

SRPG:state retention power gating,状态保持电源门控

CRPG:clock reconvergence pessimism removal,时钟再收敛悲观消除法

CPF:common power format,通用功耗格式

DFM:design for manufacuribility,可制造性设计

OPC:optical proximity correction,光学临近修正

MMMC:multi-mode multi-corner,多模式多端角

PSO:power shutoff,电源关断

SiP:silicon in package,多芯片(系统级)封装

DVFS:dynamic voltage frequency scaling,动态电压频率调节(动态电压调频)

PSM:phase shifting masks,移相掩模

SSTA:statistical STA,统计静态时序分析

DFY:design for yield,考虑良率性设计

在纳米(nm,nanometer)的设计中(<130nm),除了以上DSM 中的任务外,还需要考

虑和解决如下三类问题:

(1)功耗分析和低功耗设计,并要统一考虑它的功能验证、逻辑综合和形式验证

(2)实施纳米设计中的光学近似检查(OPC,opticalproximitycorrection)和移相掩模(PSM,phase shifting masks)的实现,考量增加设计产额(DFY)和可制造性设计(DFM)分析。

(3)更加复杂的统计静态时序分析(SSTA,见第6章)和多模式“多端角”(MMMC,见第 10 章)分析。

其中,光学近似检查是指通过光刻分辨率增强技术(RET,resolutionenhancementtechnology)进行光刻失真的光学校正;在65nm设计中还要进行移相掩模的处理。

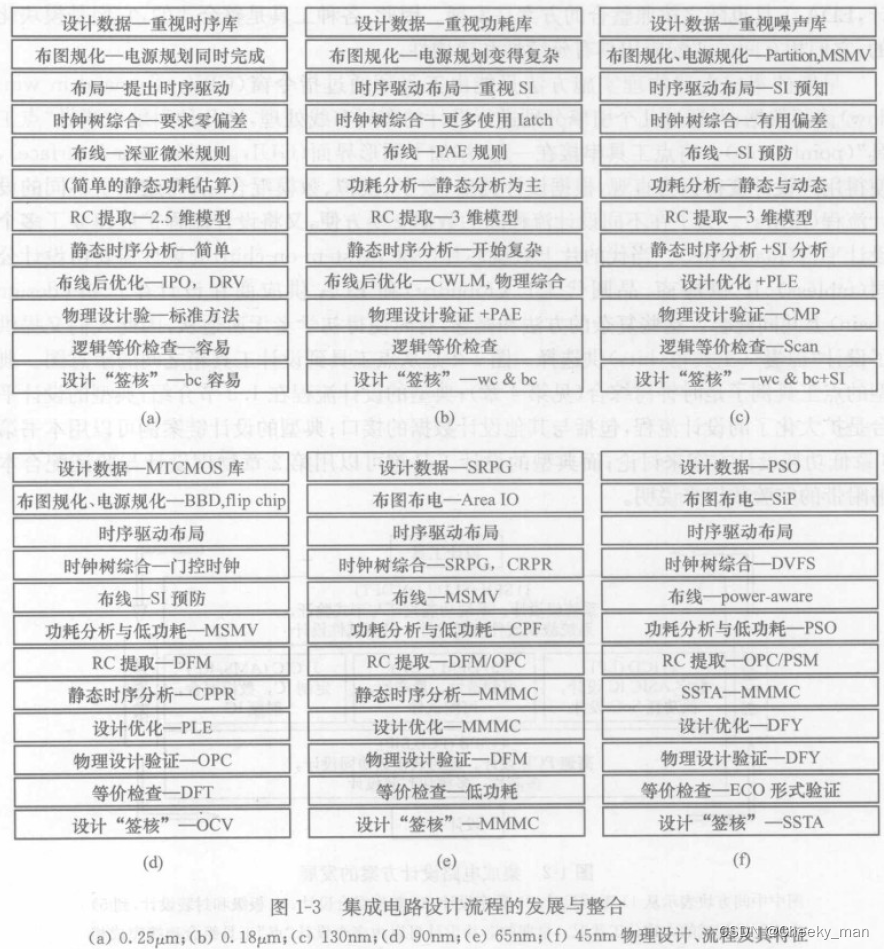

图1-3(a)所示的250nm设计流程,提出了时序驱动设计(TDD)的物理实施概念,并逐渐使用 TDD以及时序驱动布线(timing-drivenrouting),这种方法于1997年后逐渐成为标准流程。布图(floorplan)设计中的电源网格(power grid)设计较易实现,时钟树综合的焦点是追求理想化的零偏差(zero skew),同时提出了静态功耗分析。用于RC寄生参数的提取模型为2.5维,静态时序分析(STA,static timing analysis)、最终时序检査和“签核”(sign-off)不太复杂,用最差(WC,worst-case)时序库进行建立时间(setup time)的检查,保持时间(hold time)很容易满足。布线后的优化方法为原地优化(IPO,in-place optimization)和设计规则违反检查(DRV,designrule violation)。

对于1999年前后主流为180nm的设计,如图1-3(b)所示,电源布置变得复杂,电压降(IR drop)成为关心的对象,“电源规划”的概念和布图规划相互呼应,要求更加准确地计算功耗,时序库中要包括功耗信息。时序驱动布局时要求考虑信号完整性SI分析(注:近年来SI常被称为噪声分析)。时钟通常快于200MHz,时钟树结构中更多的应用锁存器(latch)来设计。在布线时要预算和防止芯片生产过程中的工艺天线效应(PAE)。在RC提取时,为了求得更准确的最终时序结果,电容空间的三维分布模型得到普遍应用。在做时序分析时,要同时分析噪声,最差和最佳(BC,best-case)时序库要分别用来检查时序。同时发现基于(互连)线负载模型(WLM,wire loadmodel)综合得来的设计网表经常不能收敛,往往要反复更新产生定制线负载模型(CWLM,custom WLM),或多次迭代(iteration)后才能收敛。这时,物理综合(physical systhesis)的概念被提出并得到应用;由于这种方法会对逻辑结构进行结构化再处理(restructuring),优化后的网表或物理综合产生的新网表,必须要通过设计逻辑等价验证(logic equivalence checking)去检查。

图1-3(c)所示的130nm流程, 其技术节点于2001年前后开始形成。这时, 基于多电源电压(MSMV,multiple-supply multiple-voltage)的低功耗设计成了重要的设计方案,功耗分析和噪声分析是必不可少的要求。时钟树的收敛变得困难, 人们提出了有用偏差(useful skew)的解决办法。由于半导体工艺中化学机械打磨(CMP,chemical mechanicalpolishing)的要求, 布线后都要进行CMP的处理和检查。另外, 在布局时还要处理扫描链, 在最终时序检查时要结合噪声对时序的影响。同时, 采用纳米技术的系统芯片SoC逻辑门数量迅速增长到数百万门(MG,milliongates), 用于DSM 设计的展平物理设计方法(见1.2.1节)完成设计时间周期太长, 因此人们提出了硅虚拟原型(SVP,silicon virtual prototyping)的快速设计方案(见1.2.2节)。为了解决时序收敛太慢的问题, 层次化的物理设计方法(hierarchical partition,见1.2.3节)也与SVP方法同时确立。

纳米技术的真正挑战是2003年前后从90nm的设计开始的, 如图1-3(d)所示。低功耗的设计成为主要需求, 要求提供多组MTCMOS逻辑单元库(见9.2.2节), 多电源多电压MSMV的实施, 在布图时要将不同电压区域(powerdomain)隔开。由于在掩模(mask)中需要对纳米的光刻作 OPC, 从单元库到RC提取, 从布线到物理验证, 都要采取额外的措施。这时, 布线后的优化和逻辑综合结合得更加紧密, 全局物理综合(GPS,global physical synthesis)的方案, 结合物理布图参数(PLE,physical layout estimator)用于加快时序收敛。DFT在设计中更加复杂, 逻辑验证周期也加长了。在静态时序分析时,人们开始考虑到片上误差(OCV,on-chip variation)的影响。

2005年前后进入65nm的设计, 如图1-3(e)所示。低功耗设计在原来的多电压多值及门控时钟等技术基础上, 增加了电源关断(PSO,powershut off)技术, 它通过状态保持电源门控(SRPG,state retention power gating)的实现, 增加了物理设计的难度。这时的时序检验更加复杂, 人们提出了多模式“多端角"(MMMC,multi-mode multi-corner)条件的分析方案。由于纳米工艺中OPC和PSM校正的要求, 人们提出了更加系统的可制造性设计及其检验程序。

2007年第一个45nm的设计参考流程已经发表并付之于实施, 如图1-3(f) 所示。从芯片到板级设计以及多芯片封装(SiP,siliconinpackage)技术的应用, 将设计数据(例如, 应用 OA 数据)和标准时序约束(SDC,standard design constraints)从芯片到封装设计流程上完全连接了起来。低功耗设计则采用了时钟的动态电压频率调节(DVFS,dynam-ic voltage frequency scaling)技术。统计静态时序分析方法(SSTA,statistical STA)得到广泛地应用。可制造性设计成为设计流程的重要步骤。

1.2.1 展平式物理设计

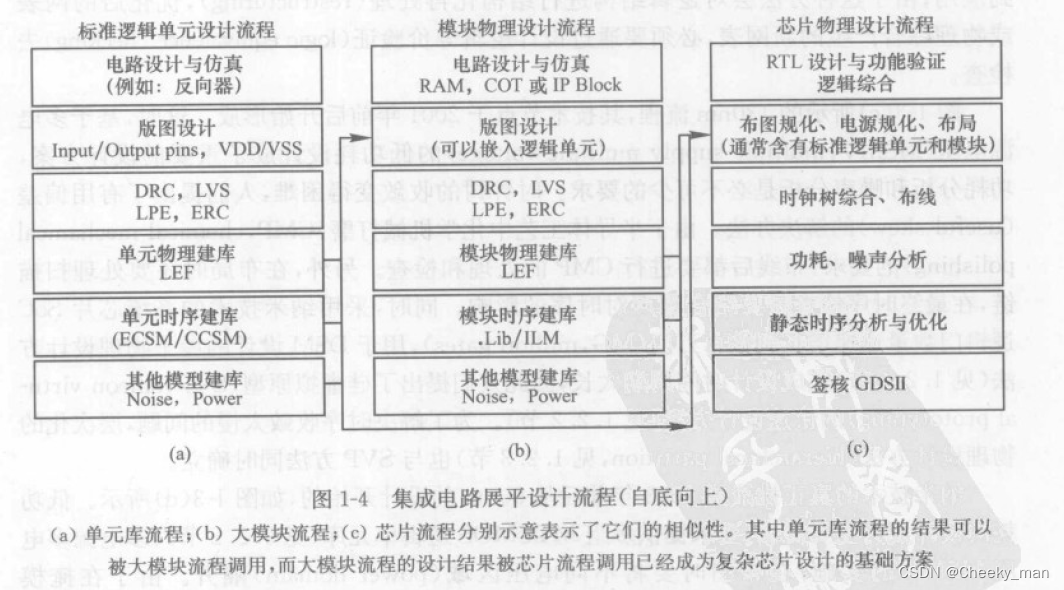

展平式物理设计是集成电路中最基本的一种方法, 最常见的例子是标准逻辑门单元库的建立。它采用了自下而上的方法, 先将晶体管设计好, 经过仿真, 版图建立, 再对逻辑门单元仿真建模, 如图1-4(a)所示。

这个方法进一步推广, 可以用在大模块设计, 比如COT模块、IP模块、存储RAM 或ROM模块等, 先经过设计仿真, 再调用基本单元并实现版图设计, 再对大模块仿真建模,如图 1-4(b)所示。

对于芯片设计, 它同样采用了这种自下而上的展平物理设计方案:

芯片经过RTL设计仿真, 通过逻辑综合产生门级网表以及相应的标准时序约束SDC文件, 再调用由上述方法产生的基本单元(标准单元库)和大模块单元(包括COT、IP、RAMROM、DSP), 以及这些单元的时序库, 通过布局布线实现物理设计, 提取RC参数进行时序分析(类似建模的过程), 最后产生GDSII文档完成全部过程,如图1-4(c)所示。

第2章所讲述的单元库建立, 其设计过程也适用于大模块的设计。它们都是从底向上的展平物理实施过程。芯片的逻辑设计和物理实施可以采用硅虚拟原型设计(见1.2.2节)方案先进行预估结果, 再采用展平式设计(1.2.1节)方案和流程或者采用层次化设计(见1.2.3节)方案和流程来实现。本书的第3~10章则重点讲述了芯片展平式设计方案的每一步原理和实施细节。

1.2.2 硅虚拟原型设计

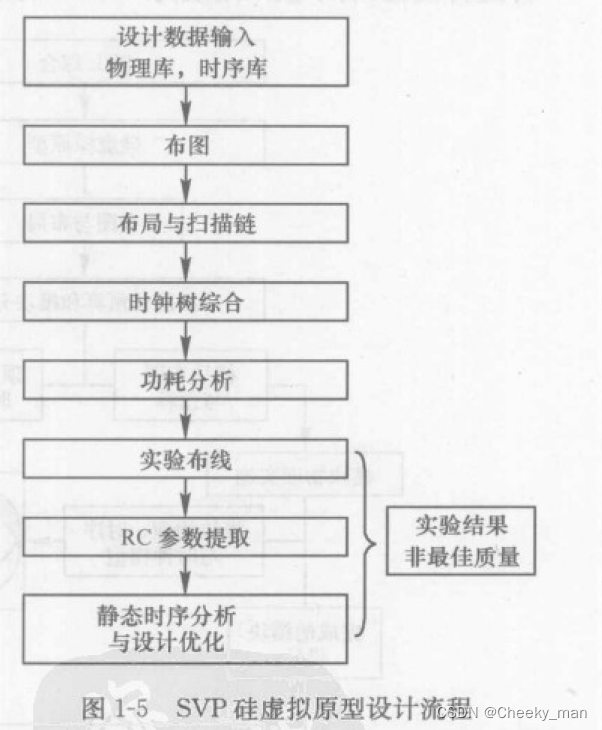

人们在物理实施中发现, 展平化的过程每一步工作都要仔细认真、反复进行, 最终达到时序收敛。由于在大多数情况下, RTL设计、功能验证和物理实施三项工作是在同时进行的, 我们往往希望尽早预估该设计能否大致实现时序收敛, 硅虚拟原型设计实现了这个目标, 其设计流程如图1-5所示。

硅虚拟原型物理设计方案与展平化的物理设计流程的区别在于以下几点:

(1) 在布图阶段, 可以考虑将整个设计进行分割(partition)

(2) 布线时用了快速近似的实验布线法(trialroute), 该算法的实施所使用的时间约为详细布线的1/10左右, 经过诸多的设计检查,与最终的结果在性能上的差距为5%~10%,从而使快速地设计收敛评估成为可能。

(3) 在作 RC提取时,可以用集总电容模型(lumped capacitance)和定制连线负载模型(CWLM)作为时序预估计算, 从而达到快速提取。

1.2.3 层次化物理设计

单个芯片所含有的逻辑单元已经从1984年的大约4万门增加到了2000年的大约4000万门, 根据摩尔定律, 从片上系统芯片设计到未来的片上网络(NoC,networkonchip)芯片的设计, ITRS预估在2010年将达到2亿5千万门(250MG或10亿个晶体管), 时钟频率快于10GHz。因此, 从RTL到GDSI过程的每一步,对于EDA 工具、工程师和计算机硬件都是巨大的挑战。

芯片设计的最终检查标准之一为, 是否实现了时序收敛, 而完成时序收敛的关键问题往往集中在某些模块。因此, 将庞大的设计在物理设计时分割成数个分割块(partition), 重点处理时序复杂的分割块或模块, 就会缩短设计收敛的周期, 使时序问题局部化。

在1.2.1节讨论了展平化物理设计, 实际上它也是一种层次化设计,不过它是自下向上的模块化方法。在这里我们专门讨论自上向下的层次化物理设计方法, 它先将设计分成数个分割块, 然后对每个分割块进行展平化处理, 包括独立的布局布线等过程, 直到完成相应的建模, 最后在顶层完成组装设计。

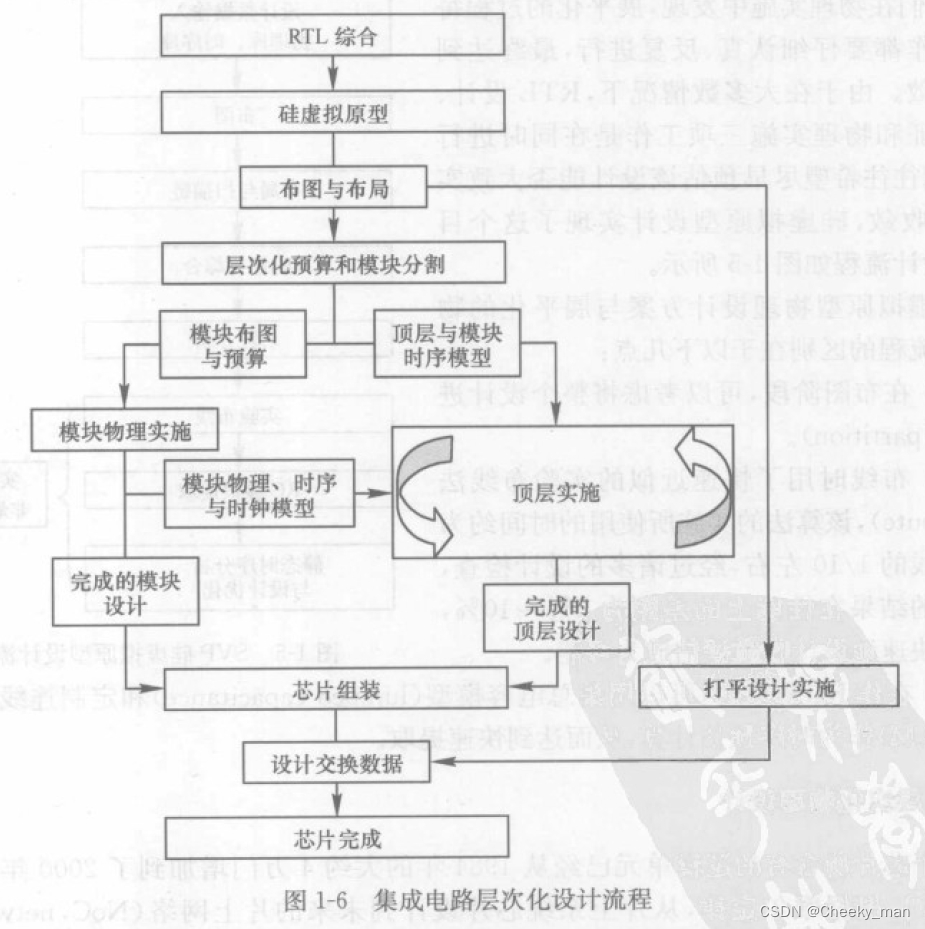

如图1-6所示,在设计之初采用硅虚拟原型设计快速的评估性能, 然后将其分割成个物理模块由不同的设计人员并行完成设计, 分割后相应的数据包括顶层为n+1组, 每组数据包括:

当前模块的网表(门级netlist和DEF)、物理库(LEF)、时序库(.lib)以及分配到模块级的标准时序约束SDC文件。

顶层模块的数据类型与模块保持一致, 所不同的是它采用原始的SDC文件。

层次化物理设计方法最早建立的例子是同时用三个不同的设计进行检验, 后来被采用成为TSMC的早期设计参考流程之一

每个模块的物理设计过程都是一个完整的展平化物理设计过程, 它根据顶层分配的数据进行物理布图规划、布局、布线,经时序优化达到时序收敛后, 产生满足物理和时序要求的一组新数据供顶层组装使用。在做顶层的布图、布局、布线时,它假定每个模块都是已收敛的黑匣子, 其物理布图最终覆盖在n个物理模块的上方, 并占据整个芯片的面积范围。当最终顶层的时序及优化达到要求时, 整个设计完成。

层次化物理设计方案的最大优点是它将很大的设计化成多个小设计, 如果有时序问题可能存在于个别模块, 再去重点解决, 则复杂性变小, 而且是局部的。同时, 每个工程师分担的工作量也变小, 完成设计的时间周期会缩短, 从而加快了设计收敛。如果某些模块(如时序)不能达到要求, 在顶层再作时序调整或重新分割, 也可以局部重新采用物理综合。

展平的设计方法和层次化的设计方法各有利弊, 其应用也根据设计者的喜好和设计公司的特点而选用。

对于较大的设计, 展平设计的实施周期较长, 其优点是不用分配边界约束, 所以能够在芯片的全局范围内进行优化, 与自上而下的层次化设计相比较, 比较容易获得更好的时序结果;

而层次化设计能够将串行作业转变为并行实施, 很大程度上能够节约设计的周期, 从而缩短芯片产品的面市时间。但是,层次化设计需要较丰富的设计经验, 当时序约束分配到底层大模块单元后, 每一个模块与其他相关大模块和顶层之间的时序约束需要各自独立实现收敛; 如果某些模块不能收敛, 它会要求在顶层重新作约束分配。所以当设计的规模没有达到无法采用展平的设计方法完成时, 设计者会偏向于采用展平的设计方法来实施。当公司的工程人力资源和软硬件资源都比较充分时, 一般会发挥并借助于EDA公司已经建立的层次化设计流程, 并沿袭至每个设计的芯片。

层次化设计需要对模块的时序建立它的文档, 通常用接口逻辑模型ILM(interface logic model)来表示, 见第2章2.5.4节。近年又提出了基于设计(要求)驱动时序图(CDTV,context-driven timing view)的设计方法, 其指导思想是在顶层设计和模块设计之间早早地建立一个连接的时序图桥梁, 从而避免当模块设计完成后回到顶层无法收敛而造成大量的设计迭代。

其具体的做法是: 将模块级的实施分成多个阶段, 如时钟树综合阶段、详细布线阶段、布线优化阶段等, 当每个阶段完成后, 都返回到顶层检查顶层设计是否满足设计收敛, 当设计出现违例时, 在顶层重新调整模块的布局, 重新分配底层模块并进一步实施。这种方法的提出主要针对目前自上而下的层次化设计收敛问题所提出的一种解决方案, 具体效果有待更多的工程实践来检验。CDTV方法的提出试图在展平设计方法和层次化设计方法中寻找一个完美的结合点,我们也期待它的良好表现。

1.3 数字集成电路设计收敛

当代集成电路从概念到方法, 实现设计收敛任务是复杂艰巨的, 它通过三大部分工作来完成[:①数据系统;②优化引擎;③分析引擎。数据系统由读取、处理和储存的功能组成(见1.4节)。优化引擎主要是指基于算法去实现逻辑优化、布局优化和布线优化的EDA工具方法。分析引擎主要是指由设计工程师借助EDA工具用于时序分析、功耗分析和噪声(信号完整性)分析的EDA工具。很显然, 对于物理设计而言, 完成设计收敛的关键是借助分析引擎的功能, 分别对时序、功耗和噪声分析过程有所了解。以下分别介绍这三种分析方法的基本原理。

1.3.1 时序收敛

在物理设计中, 通过对布局布线后的数据进行静态时序分析STA, 当满足要求后则认为实现了时序收敛。时序的要求是通过SDC去表达、约束和检验的。

- 静态时序分析的最主要方法为经典的“项目评审技术”(PERT, program evaluation and review technique)或“关键路径方法”(CPM,critical pathmethod), 今天这两种方法已合二为一。

- 在静态时序分析中, 最重要的任务是寻找最长延时路径以及最坏情况下的延时。总延时由逻辑门(也称作器件)延时和互连线延时组成。

- 逻辑门的延时大小不仅取决于输人信号的转换(transition)时间和负载电容大小, 还取决于输出信号的状态(上升或下降)以及其他管脚状态(高电平或低电平)。

- 有关器件延时模型的基本方法和建库见第2章2.5.4节。

在纳米设计中互连线延时已超过总延时的50%以上, 它主要由三维空间的RC分布来决定。有关互连线延时中的RC提取见第6章6.1节,互连线延时计算见第6章6.2节。

静态时序路径有两种, 即组合逻辑电路(combinational logic circuit)和时序逻辑电路(sequential logic circuit)形成的路径。

时序收敛的工作侧重于时钟时序逻辑电路。

由于硅晶片尺寸的增大带来的片上误差(OCV), 所以需要在静态时序分析时考虑其影响。最近又提出了统计静态时序分析SSTA的概念, 它对于实现时序收敛、提高芯片性能、增强良品率等问题提出了新的分析理念。

上面所提到的芯片物理实施的静态时序分析概念和详细方法将在第6章6.3节和6.4节中介绍。在小于180nm设计中的噪声分析已经成为设计的常规分析手段之一。噪声分析和时序分析相互关联, 相互影响。关于噪声分析的完整方法在第8章中介绍。

1.3.2 功耗分析

1. 功耗分析

功耗分析包括比较简单的静态功耗分析和复杂的动态功耗分析。

在许多DSM(深亚微米)设计中, 常用的静态功耗分析能提供平均功耗的预估值, 其方法迅速简洁。在从DSM到纳米以下的设计过程中,静态功耗与动态功耗两种分析方法都受到了更多地重视和应用, 并成为纳米设计中必须采用的完整的步骤, 尤其是在低功耗设计纳米工艺中已经不可或缺。

静态功耗分析方法简单, 用时序库提供的器件功耗数据就可以进行计算。

同样, 对于电压降(IR drop)和电迁移(EM,electromigration)效应, 它可以由物理库提供的金属物理工艺数据就可以进行分析。

动态功耗分析需要提供设计仿真的数据, 早期的方法是采用仿真产生的 VCD文件(value change format), 或通过时钟翻转计数格式文件(TCF,toggle count format)来计算。在应用中,VCD文件太大会造成使用不便, TCF的结果比较粗糙, 与电路的实际工作情况会有差异。适用于从功能验证、RTL综合、形式验证、到布局布线约束的通用功耗格式文件(CPF,commonpowerformat)目前正得到极大重视和应用。

从设计收敛来看, 低功耗设计是降低功耗的一种主动手段。关于数字集成电路功耗分析的方法和意义将在第7章中介绍。关于低功耗设计和分析以及通用功耗格式文件在集成电路设计的完整过程中使用见第9章。

2. 低功耗设计

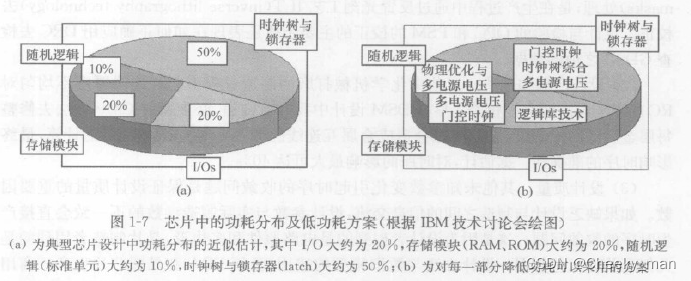

低功耗设计的要点是减小时钟电路的功耗。在典型的芯片中, 时钟电路的功耗约占总功耗的一半, 存储模块和I/O功耗各约占20%, 其余10%的功耗为随机逻辑电路, 分布如图1-7(a)所示。

降低时钟电路功耗的主要技术是采用时钟门控电路, 采用多电源电压电路可以同时降低时钟电路、存储模块和随机逻辑电路的功耗, 而I/O的功耗则要在电路设计上专门解决, 如图1-7(b)所示。

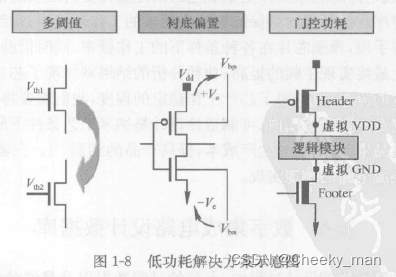

根据设计实验, 采用多电源电压的方法, 功耗可以减少30%左右; 门控电路方法功耗可以减少50%左右; 衬底电压偏置方法功耗可以减少70%左右。图1-8举例说明了多阈值电压、衬底偏置、关断电源等低功耗的手段。

从设计收敛来看, 与被动的功耗分析方法相比较, 低功耗设计是一种主动的手段。它的设计方法和实施细节将在第9章中专门介绍。

1.3.3 可制造性分析

集成电路设计收敛的另一个考察标准为可制造性设计(DFM, design for manufacturing)及其分析, 它包括设计检验、设计产额和制造、设计质量等。

- (1)设计检验, 检验光刻分辨率带来的影响并进行校正。我们已经讨论到光刻分辨率产生的误差需要通过光学邻近校正OPC去处理, 校正的基本方法是分辨率增强技术RET(reticle 或resolution enhancement technology), 它可以采用光刻预知(lithography aware)的EDA软件技术去实现(见第2章2.2节,第5章5.2.2节), 而在设计之后通过GDSII去改变光刻是不可能的。对于65nm以下的设计中移相掩模PSM(phaseshiftingmasks)处理, 是在生产过程中通过反置光刻工艺ILT(inverse lithography technology)去校正。设计与检验的OPC和PSM的校正的主要矛盾还表现在如何正确应用DRC去检查GDSII之前的数据。

- (2)设计产额和制造。工艺中化学机械打磨的制造过程引起互连线厚度不均匀对RC的影响与产额直接相关。早在DSM设计中我们就知道, 必须通过CMP方法去修每层金属间的平整度, 它同时也会造成金属互连线的厚度不均匀,影响RC的计算, 最终影响时序的准确性。据估计,对时序的影响最大可达40%。

- (3)设计质量。其他未知参数变化引起时序的收敛问题是保证设计质量的重要因数。如果缺乏设计与制造之间的信息交流, 设计参数与实际制造参数的不一致会直接产生时序的收敛问题。这是因为设计者想到的是电路原件和多边形, 晶片制造者用到的是几何形状和工艺数据。设计方法与数据模型的选用, 亟需EDA和晶圆芯片生产厂商用实际的实验芯片去作验证, 否则一切都将是纸上谈兵。现在推出了一些工艺仿真软件、产额和性能模型仿真软件,通过设计与工艺相结合的方案才会进一步提高品圆生产效率和产品利润

总之, 数字集成电路的收敛工作是集成电路由理想转变为现实的指导准则, 从而保证芯片成功流片。

- 时序收敛的目的是保证芯片在要求的工作环境中,达到理想的性能, 它通过静态时序分析等手段, 预测芯片在各种条件下的工作频率, 同时借助于约束和优化引擎从而达到路径优化最终实现主频的提高;

- 功耗分析的结果则体现了芯片的能耗大小, 芯片内部电压降和电流的分布, 也反映了芯片工作稳定的程度, 我们需要将芯片的功耗、压降电迁移等参数控制在一定的范围内;

- 可制造性设计是纳米工艺条件下所研究的一个热点,它的目的是提高良品率, 从而降低生产成本,提高产品的利润。三者相辅相成,共同指导并约束着数字集成电路的物理实现。

1.4 数字集成电路设计数据库

1.4.1 数据库的作用与结构

数据库系统早期主要由大型电子公司的CAD部门或EDA公司开发, 它们包括IBM、HP、SDA和ECAD(后两者于1989年合并成为Cadence 公司)等。需要指出的是许多公司的数据设计想法是建立在大学的研究方法和成果上的, 经过再开发研究而成为数据库产品。过去的数据库被分别用来表示网表数据和版图数据, 最著名的有DFI数据库。随着设计的晶体管数目急剧增大, 即使应用64位存储运算, 老的数据库也出现了性能和容量等问题。

用于当代集成电路设计的数据库的数据模型要具有统一的格式, 从RTL到GDSII的数据要能够最终直接用于掩模, 甚至芯片标线和品圆切割画线的数据。直至2005年,唯一公开的完整数据库系统为 Cadence 公司的“开放”(OA, open access)数据库及后来仅用于物理设计 Synopsys 公司的银河路(milkyway)数据库。根据观察, 银河数据库已经比较成熟, 但它的容量似乎和老一代的DFII数据库类似, 从而可以估计新一代的开放存取数据库〇A本身的大小只有它的1/10, 加之OA的用户接口程序(AP, application programming interface)比较干净, 具有更长远发展和应用的潜力。此外, 还有两种不对公众开放的数据库, 它们是 Mentor 公司用C++写成的“猎鹰”(Falcon)数据库和Magma 公司完全基于“小对话”(Smalltalk)的数据库。

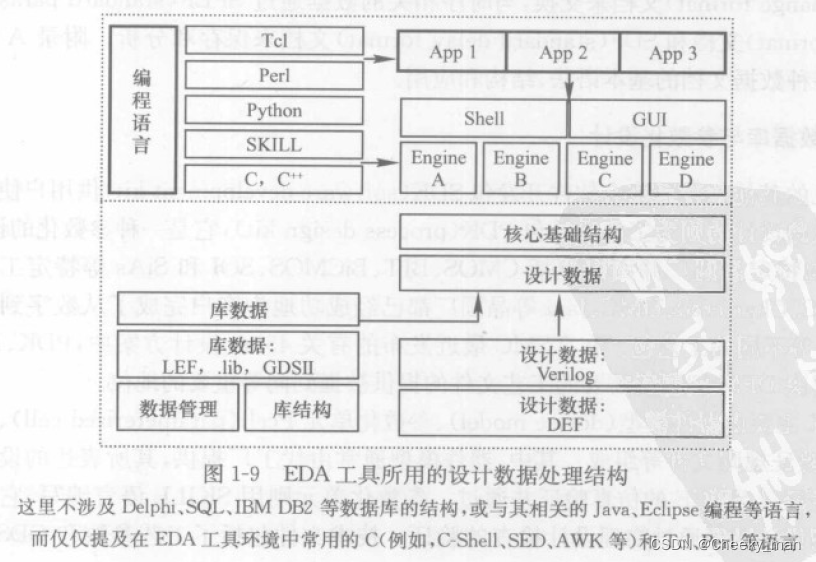

数据库的典型结构如图1-9所示。从设计分析的过程知道, 设计收敛是通过设计约束来检验并完成的。随着设计的不断完善和数据的修改, 通过数据控制的方法, 就可以获得集成电路设计的最终结果。在实际过程中, 中心数据系统被用来管理设计的每一步进展和改变, 优化引擎可以对数据直接做修改和更新, 分析引擎则对结果跟踪并报告数据的变化。

1.4.2 数据库的应用程序接口

由AMD、ARM、IBM、Intel、LSI和NXP等组成的工业界于2003年成立了硅集成行动组织(Si2,silicon integration initiative)。Si2希望借之去支持并推广开放式的 EDA设计数据, 进一步增强生产力, 减小设计的复杂性, 在硅系统的创造与生产过程中降低成本。开放式的数据库使得用户更加放心地去开发应用程序并根据设计特征提高设计效力。

应用程序接口API的特点是让开发人员通过接口去访问一组例程, 而又无需访问源码或理解内部工作机制的细节, 并执行自己的应用程序。最常见的应用程序用C++语言写成, 一般也支持Tcl、Python和Perl。在物理设计中, 用途最广泛的API是参数化的设计, 用SKILL语言写成。

集成电路的设计过程从系统定义、功能验证到逻辑综合用到多种程序语言来做自动化的处理, 它们包括C++、SystemC、SystemVerilog、e、Vera、VHDL、Verilog HDL 等熟练地应用这些程序语言是对设计者的基本技能要求。同时应当注意到, 这些语言会在应用中不断地被改善、淘汰或取代。

集成电路的物理设计与实施的过程则不一样, 它并不依赖这些语言,它更多地、具体地涉及逻辑电路和工艺器件本身, 尤其是图形界面GU的发展和应用使得工程设计师们不熟悉程序语言也能进行, 例如, 典型的、定制的版图设计。对于自动化的版图设计, 一些特殊的程序语言(例如, SKILL, 见1.4.3节)则必须掌握。在 Unix/Linux操作系统下传统的 CAD技术人员为了建立统一的EDA环境, 会常用到一些脚本(script)语言, 它们包括 C-Shell、SED、AWK、Perl、Tcl/Tk, 以及和 EDA 工具相关的宏(macro)脚本。

事实上, 与集成电路设计过程中应用程序相关的数据是由各种文本来进行的。例如,物理实施的实验和过程数据分别用LEF(Iibraryexchange format)文档(file)和 DEF(design exchange format)文档来交换, 与时序相关的数据通过 SPEF(standard parasitic exchange format)文档和 SDF(standard delay format)文档来保存和分析。附录 A收集了常用的各种数据文档的基本语法、结构和应用。

1.4.3 数据库与参数化设计

常见的其他软件系统有软件开发包SDK(software development kit)供用户使用。用于集成电路设计的则为工艺设计包PDK(processdesign kit), 它是一种参数化的设计包。PDK面向特定晶圆厂并面向包括CMOS、BJT、BiCMOS、SOI和SiAs等特定工艺。例如, TSMC、Chartered、UMC、Jazz等晶圆厂都已经成功地为客户完成了从数字到模拟以及到RF等不同的工艺包。在TSMC最近发布的有关45nm设计方案中, PDK、IP单元库以及解决 DFM 问题所需要的工艺文件的提供被提到同等重要的地位。

PDK主要由器件模型(device model)、参数化单元Pcell(parameterized cell)、技术文件、物理验证规则文件等组成。

- 其中, 器件模型通常由代工厂提供, 其所表达的设计单元应当已经经过 SPICE的仿真验证并通过。

- 参数化单元则用SKILL语言编写, 它们所对应的版图设计已经通过物理设计检查的验证。

- 技术文件包括了工艺参数和GDSII的数据与工艺代码数的影射(mapping)关系。

- 物理验证规则文件包括了设计规则检查(DRC)和电气规则检查(LVS)等。

在第2章中, 我们将更加具体地讨论PDK中用到的技术方法和文件。

1.5 总结

集成电路的物理实施方法的时髦说法被概括为从RTL综合到最终完成GDSI数据的实现。由于RTL综合已有专著介绍(见本系列丛书之《数字集成电路设计与技术》), 本书从RTL综合后的门级网表(gate-levelnetlist)着手, 从物理库和时序库数据的准备(第2章)开始, 根据设计流程顺序, 先讲解布局(第3章)、布线(第5章)和物理设计的静态时序分析(第6章), 详细介绍了物理设计中的时钟树综合(第4章)和实现的工程方法, 还专门介绍功耗分析(第7章)、信号完整性分析(第8章)和纳米技术中最先进的低功耗设计与物理设施(第9章)的方法, 最后总结并综合介绍芯片设计的最终验证与签核(第10章)。

进行集成电路的物理实施首先要理解当代集成电路设计中的多种挑战性问题, 包括根据实际课题对设计流程的理解和应用。设计的收敛关键是时序收敛, 功耗分析和可制造性分析, 三者不可或缺。统一的和开放式的数据库在设计中的应用受到人们的重视, 它不仅提供了开放端口供设计人员添加应用程序, 还可以加强设计的专业化管理, 增强数据化维持的功能和简化设计的复杂性, 缩短设计周期。

附录1 集成电路物理设计常用文档总介

数字集成电路的实现离不开EDA工具和各种技术文档的支持。从RTL到GDSI的复杂流程中, EDA工具不仅需要存取并处理各种数据, 而且为了衔接不同工具之间的流程与数据交换还要产生许多重要的中间文件。表A-1列出了一些常用库文件和文档及其在流程中的作用, 附录2~14为对每个附录文件的简要介绍。

习题

1.讨论什么是数字集成电路的物理设计和物理实施。

2.什么是硅虚拟原型SVP?为什么要提出硅虚拟原型设计方法?

3.展平式物理设计与层次化物理设计的共同点和不同点是什么?

4.设计收敛的实现与设计流程有关吗,为什么?

5.当今EDA 工具和设计所采用的主要的数据文件格式有哪些?数据库格式有哪些?常用的编程语言有哪些?

习题参考答案:

-

数字集成电路的物理设计和物理实施:

- 物理设计是数字集成电路设计流程的一个关键阶段,涵盖了从网表转化到可以制造的版图的整个过程。这包括布图规划、布局、布线、时序闭环和功耗分析等步骤。

- 物理实施则是将设计师的电路设计转换为实际硅芯片的过程,这涉及到将物理设计输出的版图数据(如GDSII文件)用于制造芯片的工艺步骤。

-

硅虚拟原型(SVP):

- 硅虚拟原型是一种设计方法,它允许设计团队在物理芯片制造之前,就通过仿真和验证来评估其性能、功耗和成本等关键指标。这种方法支持早期问题发现和解决,降低了设计迭代的次数和成本。

- 提出硅虚拟原型设计方法的原因是为了提高设计的可预测性和可靠性,减少实际硅片测试中的风险和不确定性,尤其是对于复杂的系统级芯片设计。

-

展平式物理设计与层次化物理设计:

- 共同点:两者都旨在完成从网表到版图的转换,确保设计满足所有电气和制造要求。

- 不同点:

- 展平式物理设计不区分设计中的不同功能模块,将整个电路视为一个单一层次来进行布局和布线。这种方法简化了设计流程,但可能导致资源效率低下,尤其是在大型设计中。

- 层次化物理设计将电路划分为多个模块或子系统,分别进行优化和实施,然后再集成到一个顶层设计中。这种方法提高了设计的可管理性和可重用性,适用于复杂或大型的集成电路设计。

-

设计收敛的实现与设计流程的关系:

- 设计收敛的实现与设计流程紧密相关,因为有效的流程可以系统地解决设计中的问题,确保时序、功耗和布局布线等方面都能满足目标要求。一个合理的设计流程能够逐步细化设计,通过迭代优化逐步消除问题,最终实现设计目标。

-

EDA工具和设计所采用的主要数据文件格式:

- 数据文件格式:主要包括GDSII(版图设计)、LEF(库交换格式)、DEF(设计交换格式)、SPEF(标准寄生格式)等,用于描述版图、设计规则、时序和寄生参数。

- 数据库格式:如Open Access是行业标准的数据库格式,用于集成电路设计数据的存储和管理。

- 常用的编程语言:包括Verilog和VHDL(用于硬件描述和仿真)、Python和Tcl(用于设计自动化和工具脚本编写)。

这些概念和工具是数字集成电路设计中不可或缺的组成部分,它们共同支持了从概念到最终产品的整个设计和制造流程。