热门标签

热门文章

- 1Cuda、cuDNN的下载、安装、卸载_download cudnn frontend

- 2张量分解(2)——张量运算(内积、外积、直积、范数)

- 3Android串口开发基于ndk简书,Android studio 配置NDK开发

- 4基于时间卷积网络-双向门控循环单元TCN-BIGRU回归预测,TCN-BIGRU多变量回归组合预测模型,多输入单输出模型。评价指标包括:R2、MAE、MSE、RMSE和MAPE等,代码质量极高,方_基于猎食者优化算法优化门控循环单元的数据分类预测

- 5机器学习算法基础——分类模型(二)_中等树数学模型

- 6Java面试题总结(一)

- 7如何成为一名月薪过万的Java程序员?_java开发月薪过万简单吗

- 8Java 面向对象之重写

- 9解决跨域之烦恼:Nginx如何成为你的跨域问题终结者_nginx跨域问题解决方案

- 10Python入门实战:Python文本挖掘基础_文本挖掘案例及其代码分析

当前位置: article > 正文

使用QuartusII(Verilog语言)进行四种乘法器的仿真实现_quartull ii verilog仿真

作者:笔触狂放9 | 2024-06-12 11:37:59

赞

踩

quartull ii verilog仿真

使用QuartusII(Verilog语言)进行四种乘法器的仿真实现

1、并列乘法器(使用“X”实现)

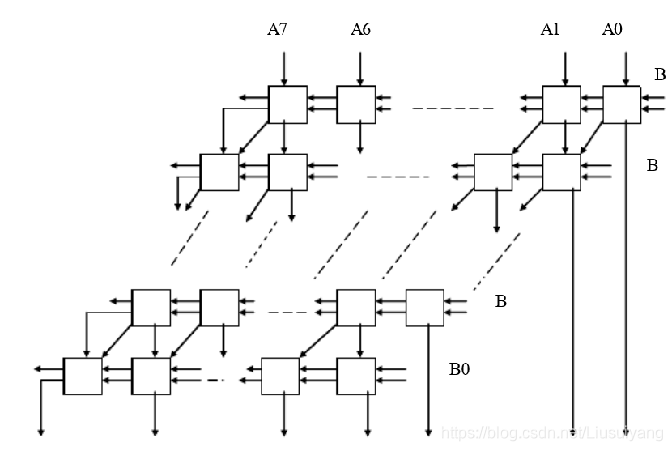

原理图如下:

被乘数A=A7A6A5A4A3A2A1A0,乘数B=B7B6B5B4B3BB1B0,所得乘积为十六位数由P=P15P14P13……P1P0表示。阵列乘法器由8行8列的细胞模块组成,其中每个细胞模块就是封装好的全加器,64个全加器连接后组成阵列乘法器。

Verilog语言实现:

仿真图像:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/707933

推荐阅读

相关标签