热门标签

热门文章

- 1一文搞定前端代理骚操作!再也不怕线上bug啦!

- 2windows下Git BASH安装_gitbash windows安装

- 3springcloudalibaba实战_spring cloud 阿里巴巴版本

- 4python可视化:玩转pyecharts库,分析星巴克门店2023年底最新数据,生成动态全国热力图。_星巴克新增门店数据柱状图

- 5python/pandas 读取Excel不同sheet的数据(或名称)_pandas读取sheet

- 6zemax场曲畸变图_zemax角度视场和真实像高视场畸变值与畸变图里的对不上以及操作数disg的疑问。...

- 7数据结构——相关内部排序算法梳理_数据结构中,对排序数据的初始状态不作任何要求的排序算法

- 8Springboot使用数据库连接池druid_springboot2.5.4 druid连接池配置详解

- 9Python异步等待 使用async和await关键字来创建和暂停协程_python 异步等待

- 10【2024最新精简版】网络_Linux操作系统面试篇

当前位置: article > 正文

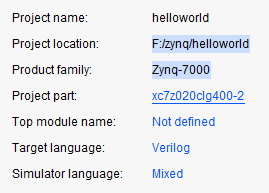

ZYNQ学习日志-------hello wold_zynqd的bank0电平设置成多少

作者:笔触狂放9 | 2024-06-17 17:17:25

赞

踩

zynqd的bank0电平设置成多少

新建工程

版本:vivado 2018.1

ZYNQ板子使用米联客ZYNQ7020

正常创建工程,无需添加设计文件。

型号选择:xc7z020clg400-2

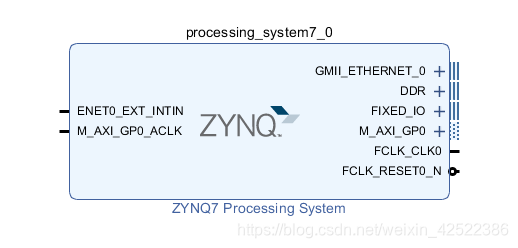

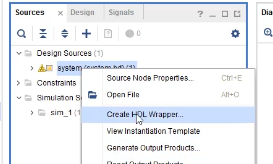

创建block

1.creat block design(IP INTEGRATOR下),

2.添加IP,添加一个ZYNQIP

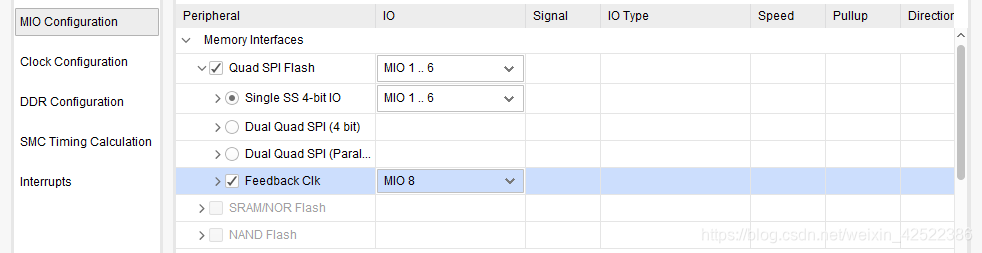

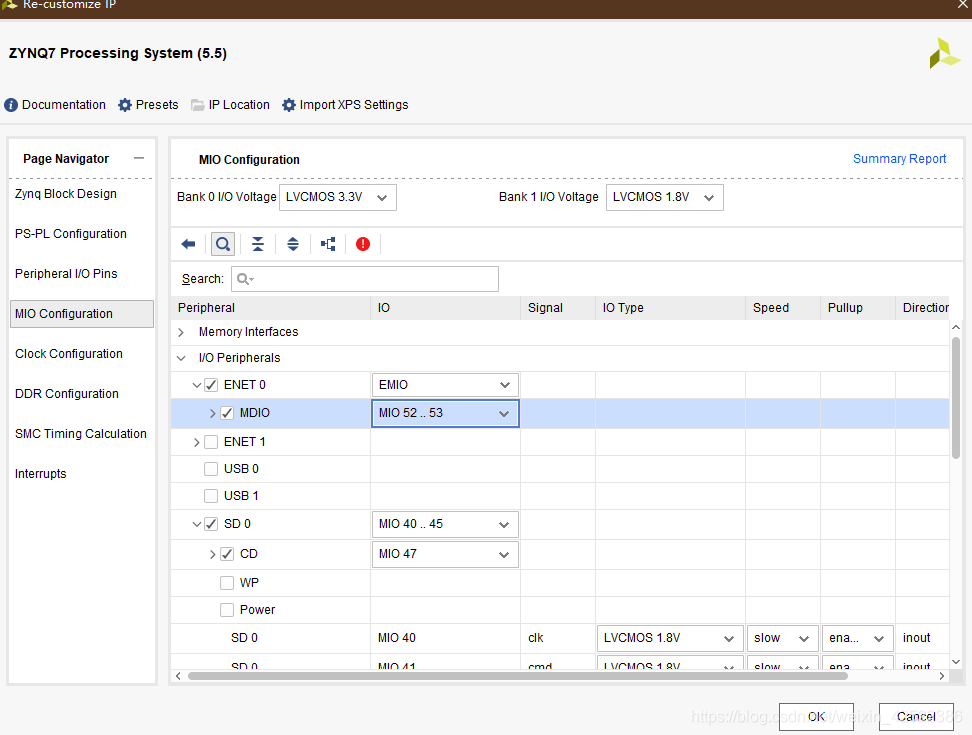

3.配置ZYNQ

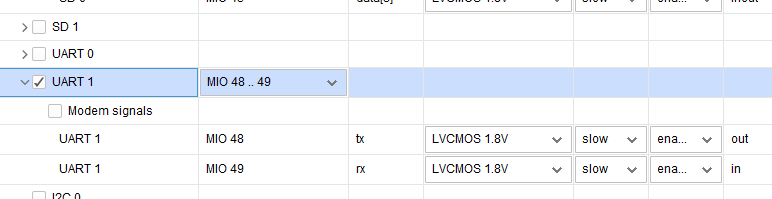

此工程中,使用到SD0,UART1.打开即可,CD管脚在此块板中是47,其他板参考原理图。

BANK 0 I/O Voltage 选择3.3V

BANK 1 I/O Voltage 选择1.8V

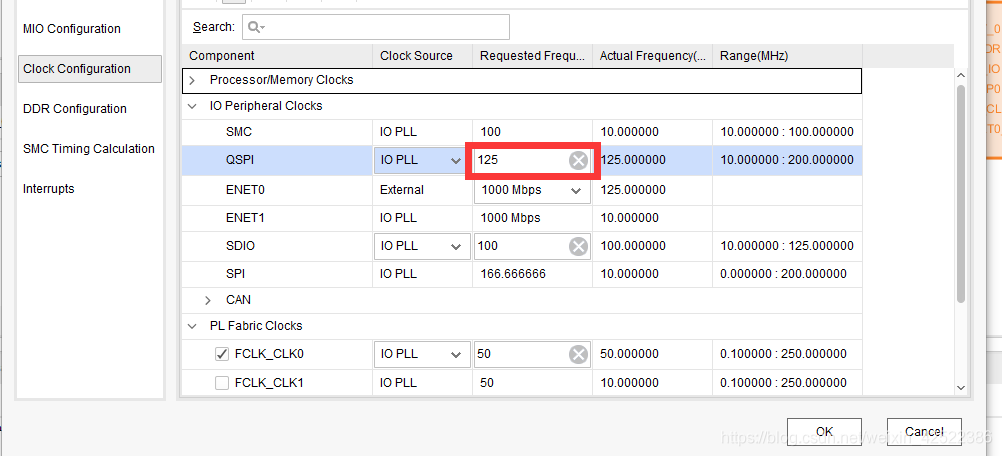

更改PS端时钟,默认200M,更改为125

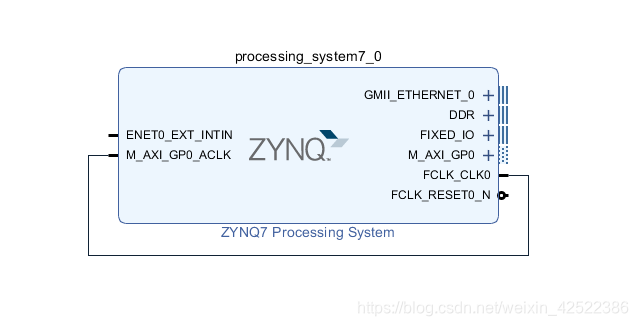

4.连线

此工程没有其余的IP,只需将CLK连上(也可将FCLK_CLK0删掉)。

连接SDK

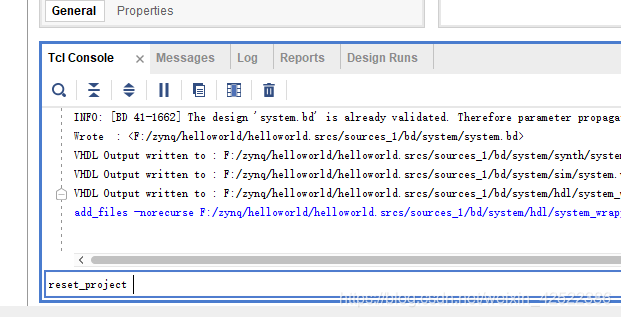

当软件出现一些莫名其妙的问题可以重置工程,没有就忽略。

步骤

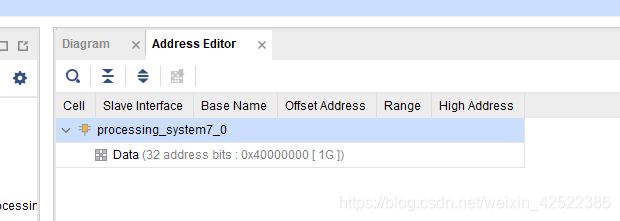

地址分配:只用到DDR,软件自动分配地址,有特殊要求才需自己更改。

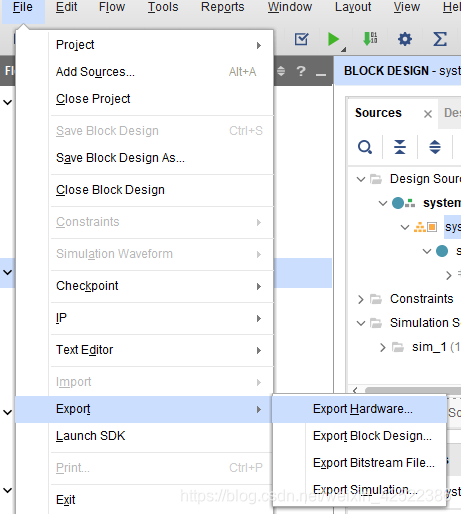

生成bit,直接生成即可,

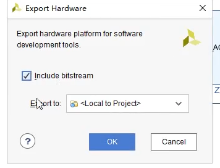

导入

勾选inclede bits

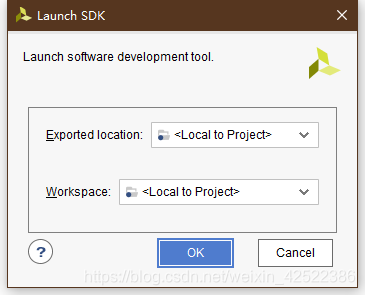

launch sdk

file -> launch SDK

PS端

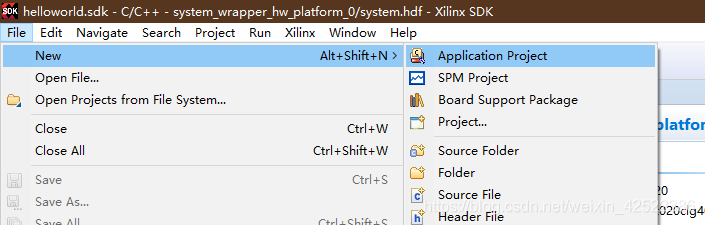

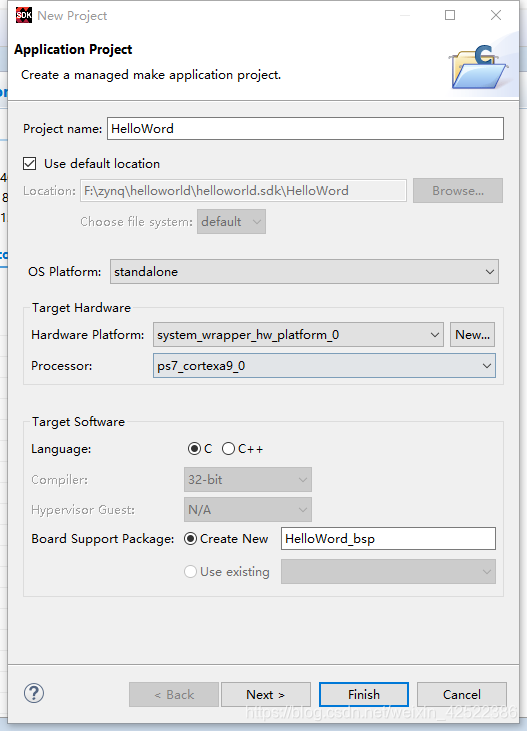

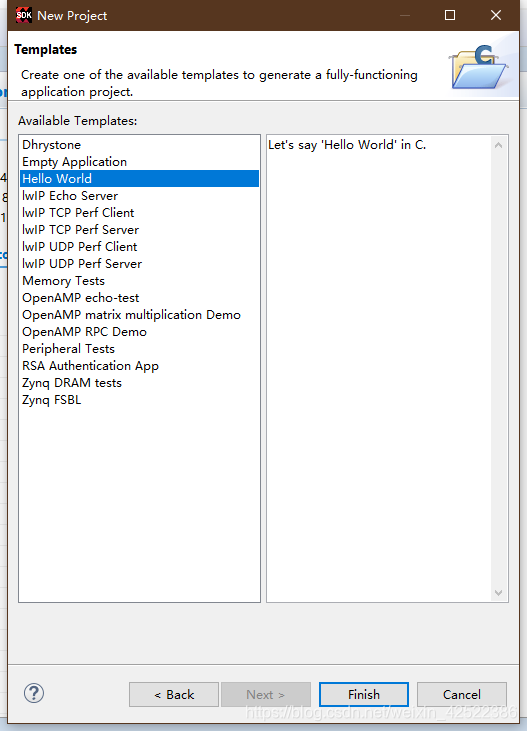

建工程,输入工程名后next,然后选择模板(已有hello word模板,使用即可)。

等待编译完成。

添加串口,将板子的串口连上电脑后添加COM口。

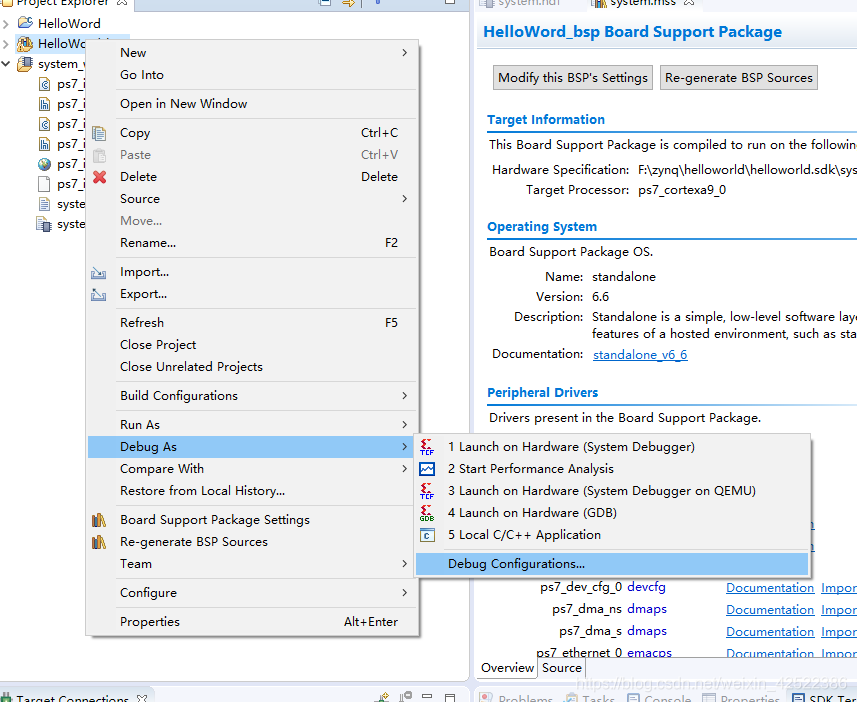

开始调试

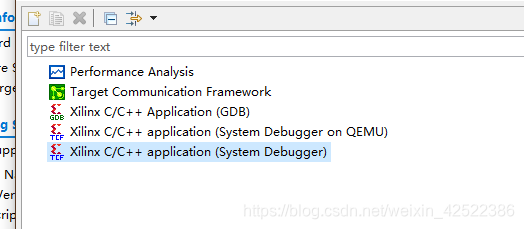

选择第5个,双击

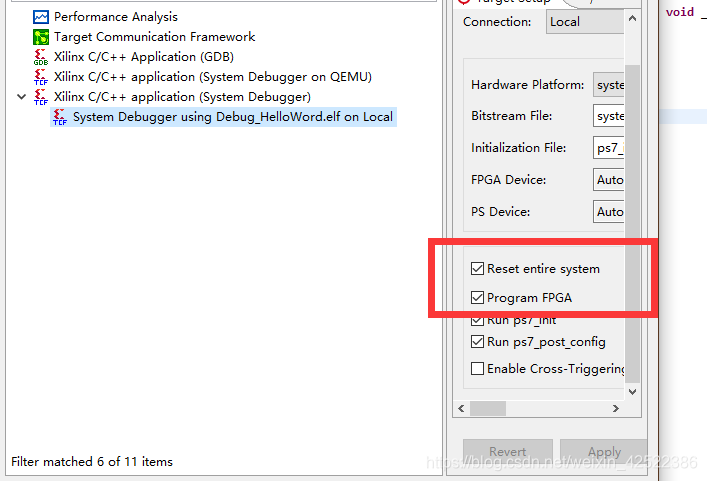

勾选

然后apply,debug。

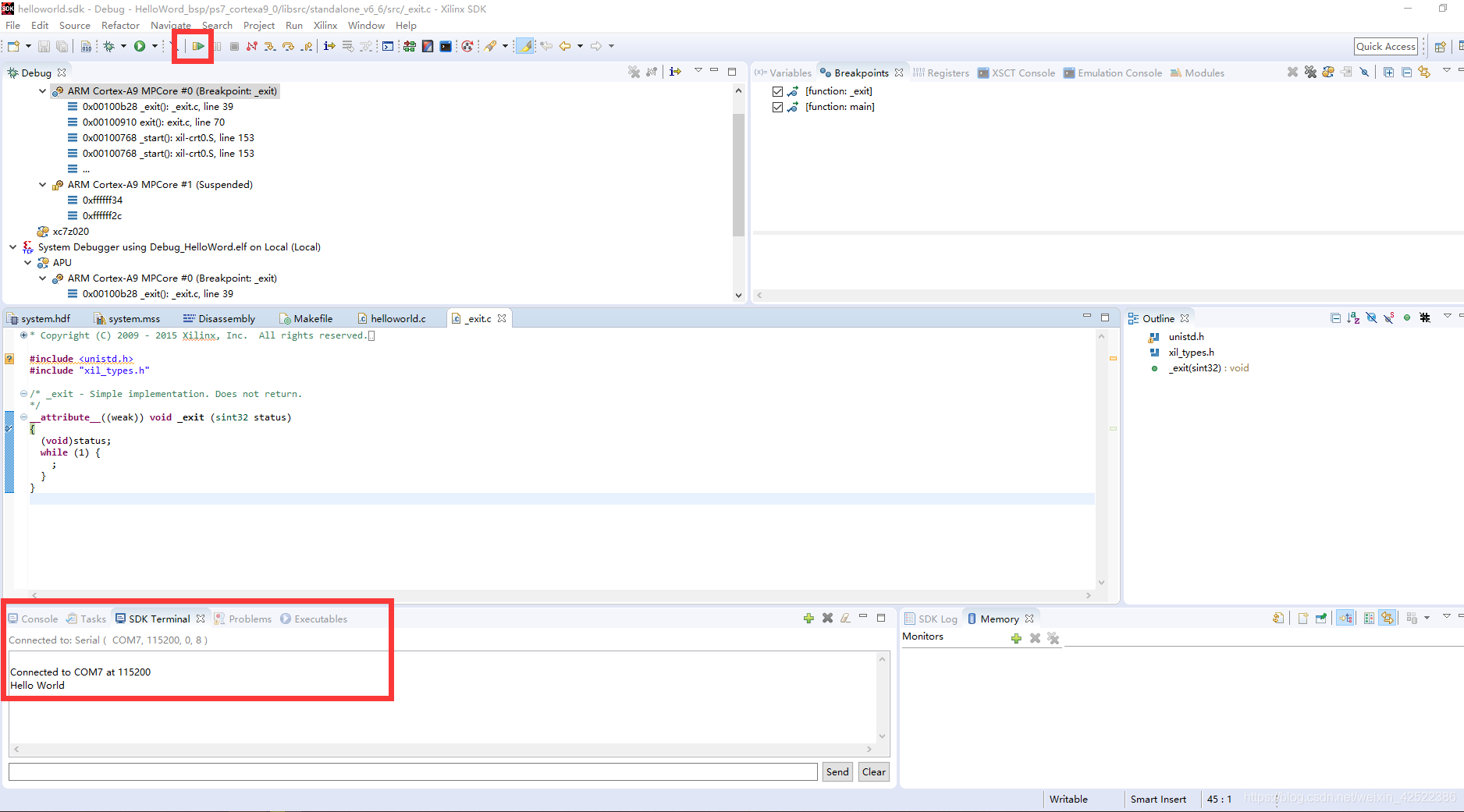

来到调试界面

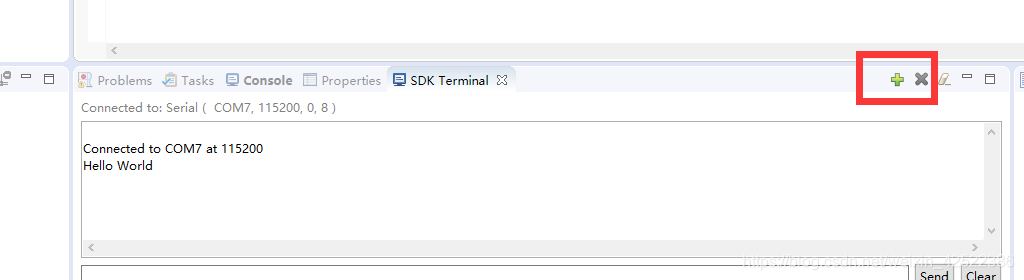

下端选择SDK Terminal界面,然后运行就可以收到hello world

同样的工程,,可直接在SDK中添加新的工程,例如DDR,DRAM,IwIP,不需要在配置fpga,从SDK步骤开始,相同的操作,DDR,DRAM,可在串口反馈,网线的需要板子和电脑用网线连,再在网络共享中心配置一下协议IP,即可使用网线通信软件通过网线进行数据传输。

同样的工程,,可直接在SDK中添加新的工程,例如DDR,DRAM,IwIP,不需要在配置fpga,从SDK步骤开始,相同的操作,DDR,DRAM,可在串口反馈,网线的需要板子和电脑用网线连,再在网络共享中心配置一下协议IP,即可使用网线通信软件通过网线进行数据传输。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/732103

推荐阅读

相关标签