- 1一文掌握文本语义分割:从朴素切分、Cross-Segment到阿里SeqModel_对文本根据语义进行分割的方法

- 2Java集合类之ArrayList_java中inforarray

- 3windows默认共享的打开和关闭_window server 关闭默认共享

- 4SSM农产品交易平台 计算机毕设源码68056_research on bilateral pricing of bulk agricultural

- 5MetaGPT全面指南:多代理协作框架的深入解析与应用

- 6Python用逻辑回归、决策树、SVM、XGBoost 算法机器学习预测用户信贷行为数据分析报告...

- 7『大模型笔记』AI 智能体(Agent)在推理(Reasoning)、规划(Planning)与工具调度(Tool Calling)方面的研究:综合调查!_ai ignorereasoning

- 8python遍历一个文件夹下所有excel,读取所有sheet页,然后写入另一个文件夹下对应模板的excel中_用python检查excel文件中所有的sheet页

- 9抖音短视频矩阵系统技术源头/源代码开发部署/SaaS贴牌/源码api代开发_ai助力的短视频营销平台代码开发

- 10ElasticSearch 集群添加用户安全认证功能(设置访问密码)_es集群添加密码验证

改造STM32F103C8T6为AG32FV103开发板_ag32vf103

赞

踩

一、改造过程

1、利用热放枪将STM32F103C8T6模块焊下来。

2、将AG32FV103(48脚)贴上开发板,注意芯片上的圆点要和板子上的白点对应上。

二、配置AG32FV103芯片

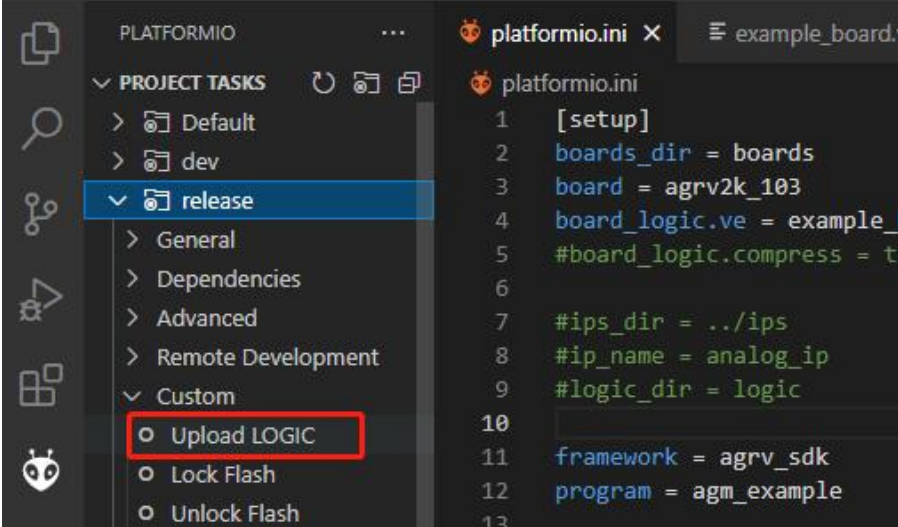

1、利用VS code打开..\AgRV_pio\platforms\AgRV\examples\example下的项目

2、打开platform.ini文件

(1)将第3行修改为 board = agrv2k_103

(2)将第27行注释去掉,并修改为board_logic.device = AGRV2KL48

(3)将JLINK V9的7和9脚连接到开发板的SWIO和SWCK,准备利用swd方式下载代码

第一次使用 jlink,需要先安装插件【zadig-2.8.exe】。注:如果第一步从下拉列表中找不到【J-Link】项,可以把下拉列表打开,插拔 Jlink几次,找列表中的变化项。列表中的那个变化项,就是要更新驱动的项。

(4)新开发板第一次使用,要先烧录 VE 配置。(不烧录 VE 而先烧录程序 bin,会报错)。烧录 VE按钮如下:

三、编程测试

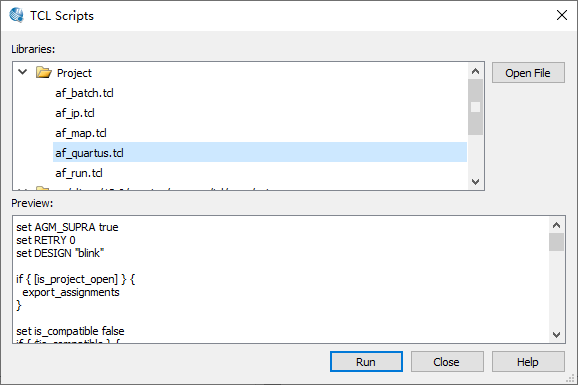

1、在Quartus中新建项目文档

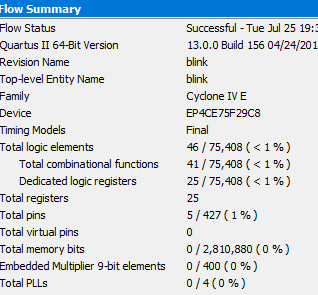

2、点击tools->TCL Scripts,选择af_quartus.tcl,启动编译过程,查看错误信息,注意占用的逻辑单元数不能超过2K,本例占用46个。

3、注意:第一次导入工程,必须执行上图的方式来转换。后续编写和修改 FPGA 代码后,可直接点“编译”按钮编译即可。

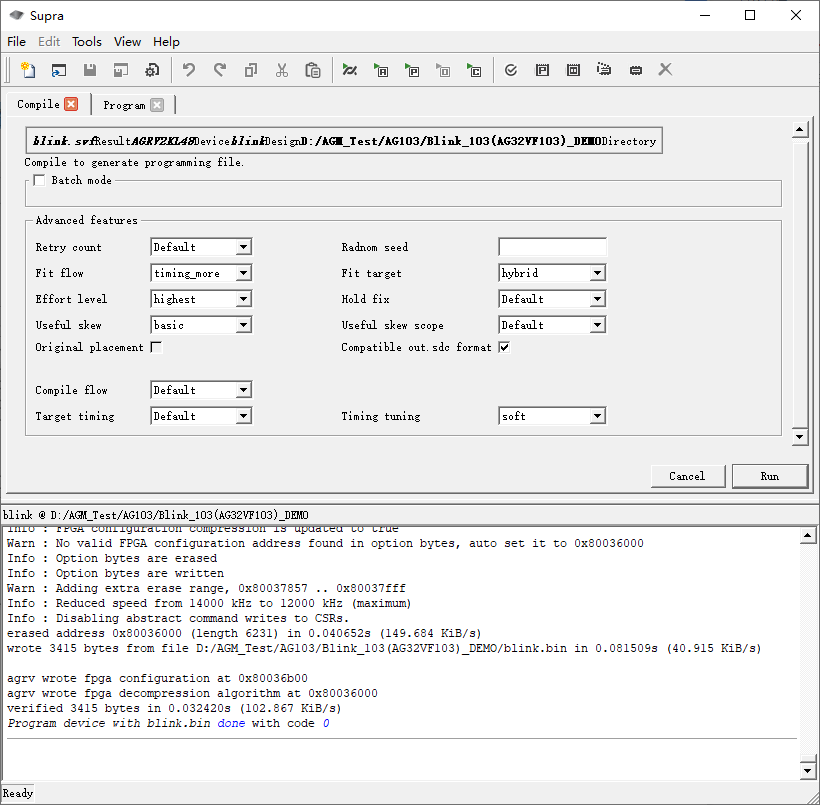

4、在 Supra 工具里,打开该工程。然后,点击 Tool -> Compile,在弹出的画面中点右下角的【run】。

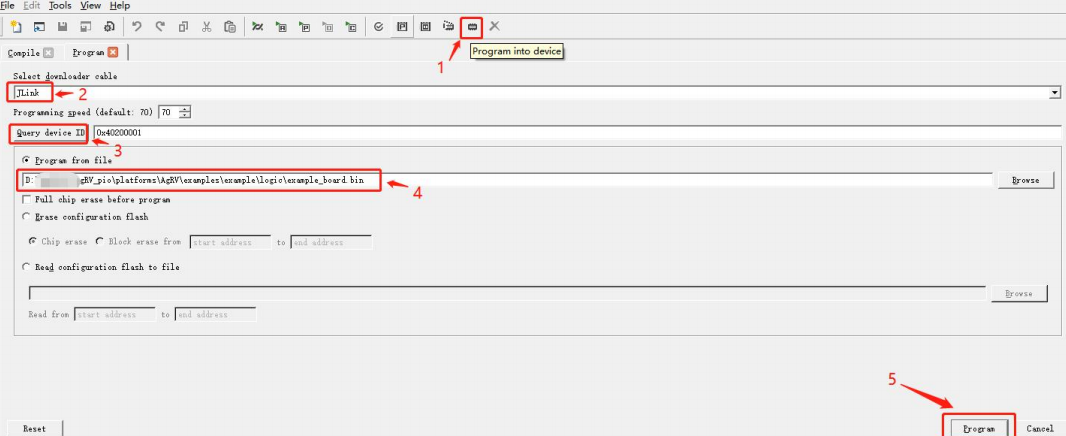

5、点击tools,选择program,加入bin文件,点击Done,下载完成。

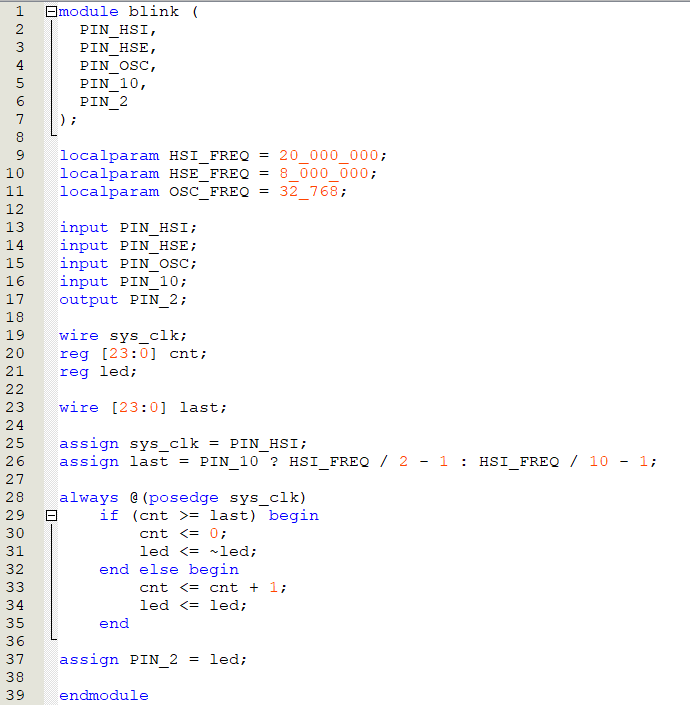

6、代码分析

HSI为内部高速时钟,默认20MHz,HSE为外部高速时钟,即晶振8MHz,OSC为RTC时钟,即32768Hz,PIN_10为PA0引脚,PIN_2为PC3引脚(在VE中已配置),25行给sys_clk赋值为HSI

26行检测PA0引脚状态,若为高则取HSI的二分频,否则取十分频,always过程控制led闪烁。

现象:当PA0为高电平时,LED慢闪,否则块闪。

7、查看结果。