- 1MySQL函数:行转列CONCAT、CONCAT_WS、GROUP_CONCAT的使用(精要)_mysql列转行函数

- 22--JavaSE基础--运算符&选择语句

- 3AI系列:大语言模型的function calling(上)

- 4第一次本地git push到远程仓库的时候出现 Updates were rejected because the remote contains work that you do not_hint: the same ref. if you want to integrate the r

- 5虚拟机下Redis的安装和部署_虚拟机上部署redis

- 6linux学习(超全)

- 7C++关于开源包7zip压缩工具的编译及使用_7zip库

- 8mysql根据一个表的数据更新另一个表数据的SQL写法_mysql根据查询结果更新另一个表数据

- 9九种 OOM 常见原因及解决方案(IT枫斗者)

- 10结构设计到项目管理:工程师是怎么练成的._冰箱结构工程师项目经验怎么写

基于Ultrascale+系列GTY收发器的8b/10b编码方式的数据传输(一)——GTY IP核介绍及配置

赞

踩

GT功能介绍

本节对GTY高速收发器用户手册内容进行简单整理,完整内容请参考UltraScale Architecture GTY Transceivers User Guide (UG578)。

GT(Gigabit Transceiver)是PFGA中用于高速协议数据收发(如PCIe、万兆以太网、SATA等)的硬核资源,它的主要功能类似与iserdes/oserdes,用于进行外部输入的高速串行数据与FPGA能够处理的慢速并行数据的相互转换。Ultrascale+系列的GTY与其他系列的GTP、GTX、GTH等功能相似,主要在支持的最大时钟频率,即数据传输的最大频率上存在差异。

在Ultrascale+系列的FPGA中,GT资源存在于GT bank中,每个GT bank共具有1个GT COMMON和4个GT CHANNEL,其中GT COMMON主要负责为GT CHANNEL提供时钟,4个GT CHANNEL各负责利用1个TX引脚和1个RX引脚进行数据收发。

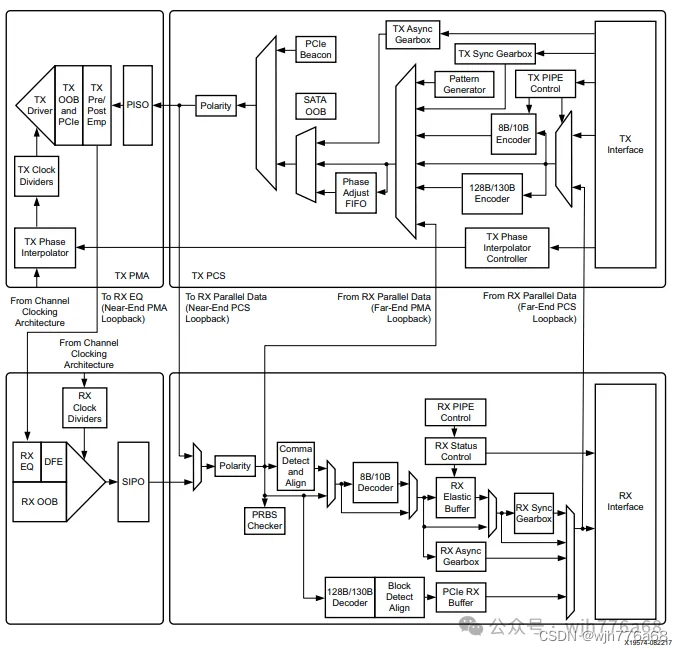

Ultrascale+系列的GTY的GT CHANNEL的结构框图如下,TX和RX部分均由PCS、PMA两个部分构成,其中PCS用于对并行数据进行处理、PMA用于对串行数据进行处理。可以看到GT除了串并转换(PISO、SIPO)外,在PCS部分还包括有其他辅助模块,这些辅助模块主要为了解决传输高速数据传输过程的额外问题。

高速数据传输的问题:

噪声与信号衰减:在长距离数据传输时,信号很容易出现衰减,GT的PMA侧提供了LPM(低功耗)/DFE(高性能)两种均衡器。

时钟恢复:为了避免走线延时的差异。高速数据传输通常采用串行差分方式进行数据传输,这种方式需要在数据中携带时钟。为了便于GT接收部分能够恢复时钟,数据信号需要保证不出现连续1或0,因此GT往往需要采用编码方式将用户数据转换为不连续出现1或0的数据信号,GTY内置的编码方式包括8B/10B、64B/66B、64B/67B(后两者位于Gearbox中)、128B/130B。

直流平衡:数据信号不出现连续1或0除了为了便于时钟恢复外,还为了用于实现直流平衡,避免因较长的1系列产生的直流电平对滤波器的电容充电,导致电压不平衡问题和误码。为此,在不传输数据时,发送端需要不断发送不出现连续1或0的伪随机数。

带宽匹配:由于编码方式的存在,编码数据和解码数据间的带宽存在差异,接收侧采用Elastic Buffer弹性缓冲区(类似FIFO,在缓冲区快满时不传输控制字符以降低带宽)用于解决带宽不一致的问题。

8B/10B编码方式

本文采用8B/10B编码方式进行实现,8B/10B编码将8bit即1个字节的数据为一组编码为10bit的编码数据。共分为数据字符编码和控制字符编码两种类型。

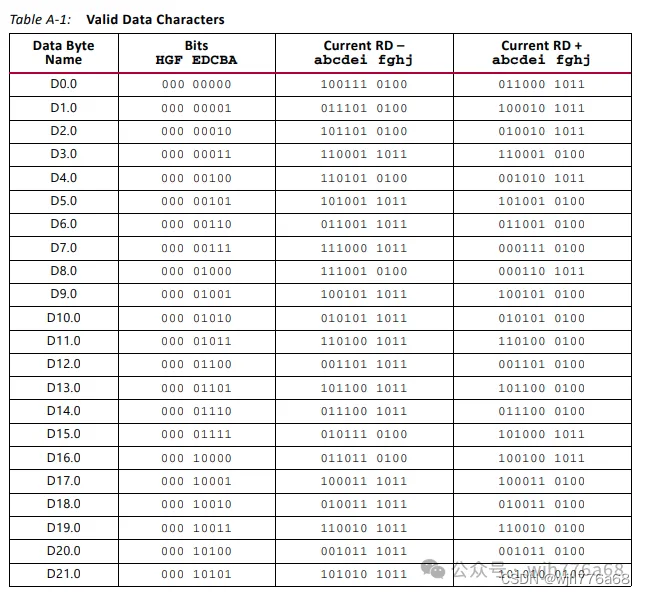

数据字符编码:为了便于硬件实现,8B/10B编码将原始8bit字节被拆分为高3bit X和低5bit Y,在表示时采用DY.X的方式进行表示,其中D表示数据,如下表所示展示了0-21共22种数据的8B/10B编码关系,每个8bit数据对应两种10bit编码,两种编码一种为1的个数比0的个数多两个的正极性(RD+)编码,一种为0的个数比1的个数多两个的负极性(RD-)编码,在传输时正极性编码与负极性编码交替传输(即第一次传RD+,第二次RD-,第三次RD+…),这样1与0的个数差异不会超过2,从而保证直流平衡。

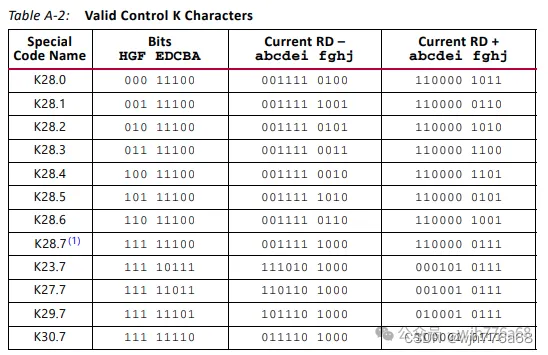

控制字符编码(K码):控制字符编码采用KY.X的方式表示,它在编码后的10bit字符上与DY.X存在差异。控制字符的存在主要为了解决字节对齐、通道对齐、时钟纠正、帧起始、帧结束等编码方式遗留的问题。

字节/逗号对齐(Comma alignment):由于数据信号0、1连续变化,为了区分输入的串行数据哪10个bit为一组,引入了K28.1、K28.5两种K码。

通道对齐(Channel bonding):由于1组TX、RX收发带宽存在上限,例如PCIe协议通常采用多组TX、RX进行收发从而提升带宽,受走线延时影响,多组TX、RX的数据到达时间存在偏移。为了解决延时不一致的问题,TX可以向RX发送包含K码的通道对齐序列,由通道绑定控制器调节弹性缓冲区的输出延时。使用时需要指定时钟纠正与通道对齐两者的优先级。

时钟纠正(Clock Correction):弹性缓冲区两侧的时钟(RX PMA恢复的时钟与RX接收端产生时钟)间可能存在微小的差异(受工作条件影响),在长时间数据收发过程后累积可能产生多个周期的差异,为了解决时钟差异问题,TX可以定期向RX发送包含K码的时钟纠正序列,当RX弹性缓冲区变满时,可以将时钟纠正序列删除,当RX弹性缓冲区变空时,可以输出时钟纠正序列。

帧格式定义:8B/10B编码通常采用帧的方式进行突发数据传输,如Aurora 8B/10B、PCIe1.0/2.0等,其中帧开始、帧结束设置为两个不同的K码。

IP核配置

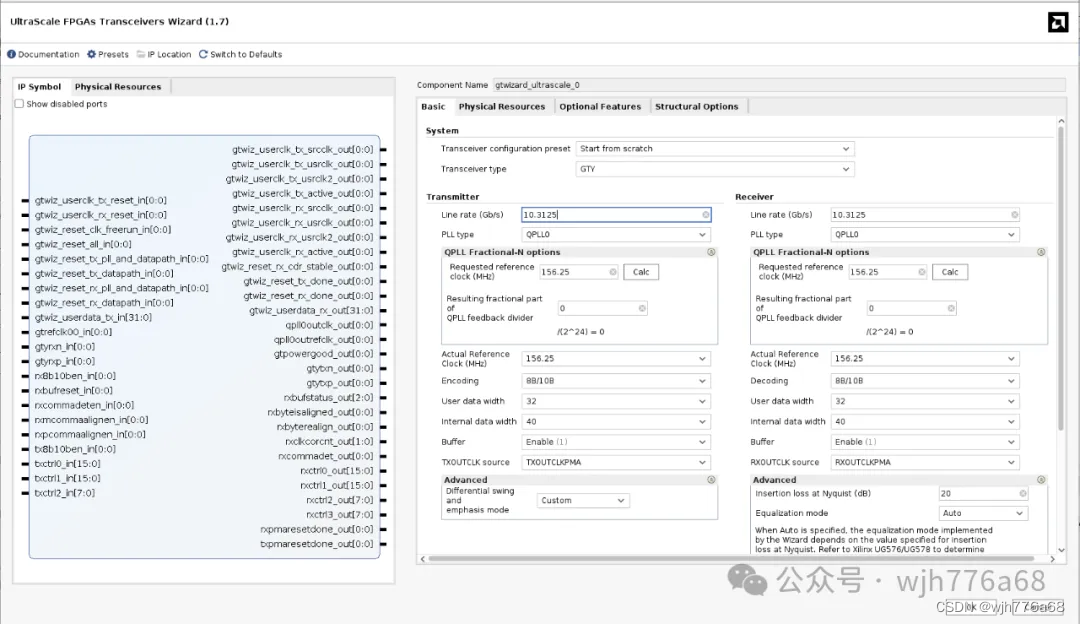

编码设置:本文使用Xilinx Virtex Ultrascale+HBM VCU128开发板进行测试,使用QSFP1端口对应GT自环测试,采用8B/10B编码方式的GTY IP核的配置如下,线速率选择默认10Gbps,为了使用8B/10B编码,需要在Encoding部分选择8B/10B方式,这时用户数据位宽可设为32 / 64(不同位宽用户时钟频率不同),内部数据位宽将为40。在参考时钟上使用QSFP1所在GT BANK的参考时钟,时钟频率156.25MHz。

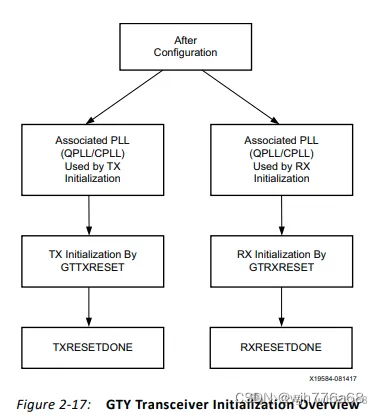

复位时钟设置:GT在使用前必须进行复位,GTY的复位包含时钟(GT COMMON)复位、发送复位、接收复位三个部分,其中发送复位与接收复位独立进行。

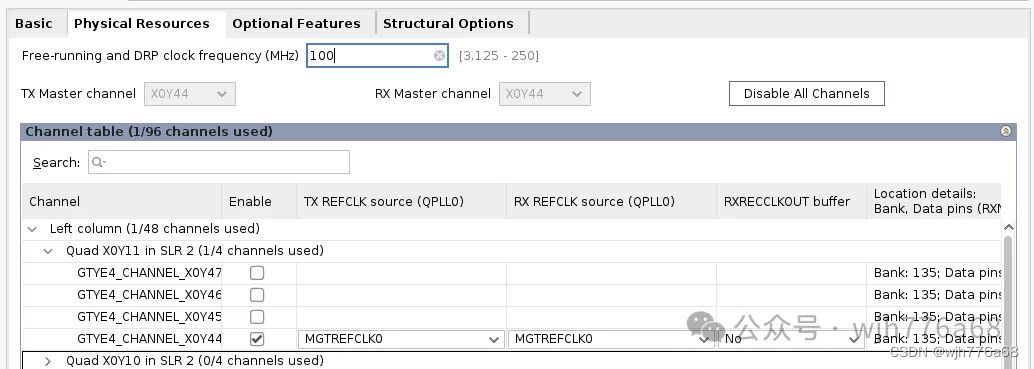

由于GT COMMON/CHANNEL复位前不保证时钟能正常产生,因此需要使用额外一个时钟控制复位逻辑,这里使用128板卡的默认100MHz时钟。Free-runing时钟频率设置为100MHz。

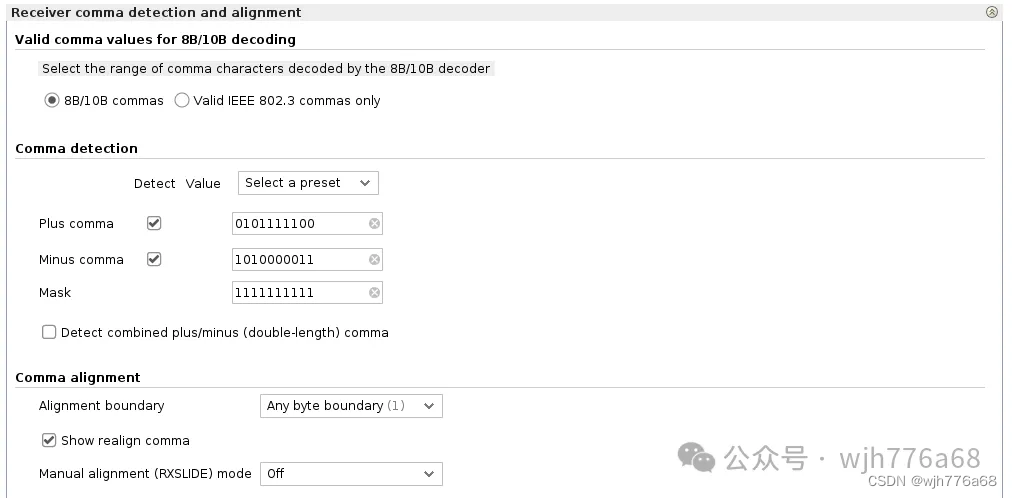

字节对齐设置:本文8B/10B采用K28.5编码作为逗号,对应极性编码写入正逗号和负逗号后,其中逗号对齐的对齐边缘选项用于规定逗号在32bit用户数据信号中出现的位置,从而能够实现用户数据字节的对齐:

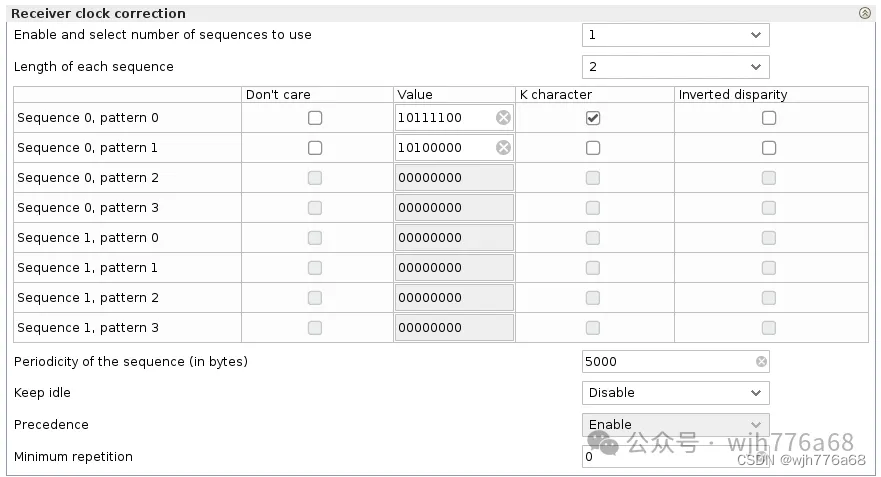

时钟纠正设置:如下图所示,时钟纠正需要指定时钟纠正的序列长度。本文以1个时钟纠正序列,长度为2为例,时钟纠正采用K28.5进行。

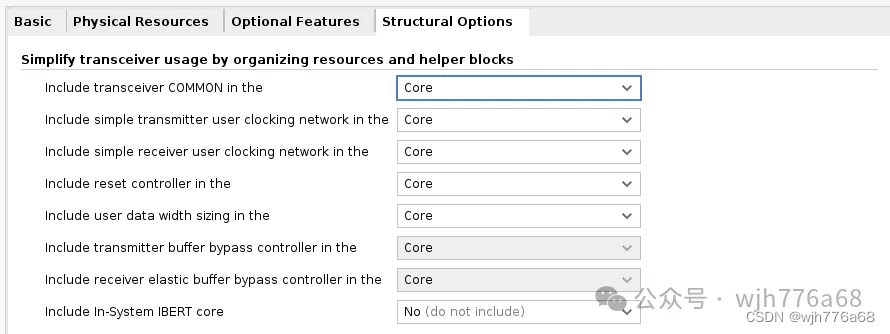

其他设置:本文主要介绍8B/10B编码,其他设置采用IP核内部生成的方式。

本文介绍了基本8B/10B传输所需的GTY IP核配置,下文将利用本文配置的IP核进行数据收发。

工程代码

本文所涉及的工程代码可在同名公众号回复GTY_8B10B_SIMPLE下载。