热门标签

热门文章

- 1SDK Tools version25.2.5 26.1.1_android sdk 25.2.5

- 2汽车行业中的AUTOSAR与OSEK到底是什么,有什么区别_osek全称

- 3python鼠标移动事件_Python3 tkinter基础 Frame bind 鼠标移动事件 实时显示鼠标的位置...

- 4Mysql、HiveSql、SparkSql的区别_sql与hive、mysql区别

- 5CVHub | YOLOv10 正式发布!原理、部署、应用一站式齐全_yolov10部署

- 6Mysql疑难报错排查 - Field ‘XXX‘ doesn‘t have a default value_mysql非空字段报错 field

- 7中国最大的系统软件外包公司排名靠谱的IT人力外包企业有哪些_深圳极联股份有限公司是外包吗

- 8ChatGPT百科全书(全网最全面)_chatgpt介绍

- 9Python实现基于人脸识别的上课考勤系统,可作为毕业设计_基于python人脸识别的课堂签到系统

- 10如何在飞桨 x 昆仑芯上部署PP-OCR模型 | 洞见AI硬件

当前位置: article > 正文

FPGA的spi flash配置-配置模式理解_vivado在tool中手动设定flash的配置方式。

作者:繁依Fanyi0 | 2024-06-11 16:34:38

赞

踩

vivado在tool中手动设定flash的配置方式。

FPGA的spi flash配置-配置模式理解

起因

现在在做的FPGA工程是基于以前的工程,其中flash配置啊什么的都没有进行过修改,之前是采用的spi x1的模式,现在新的数字版改为了spi x4的模式,所以我就认为需要修改xdc约束文件。但是在xdc文件中搜索相关引脚,发现并没有对其做任何约束和定义,所以考虑应该是FPGA固有的一些配置引脚,不需要单独定义和约束。

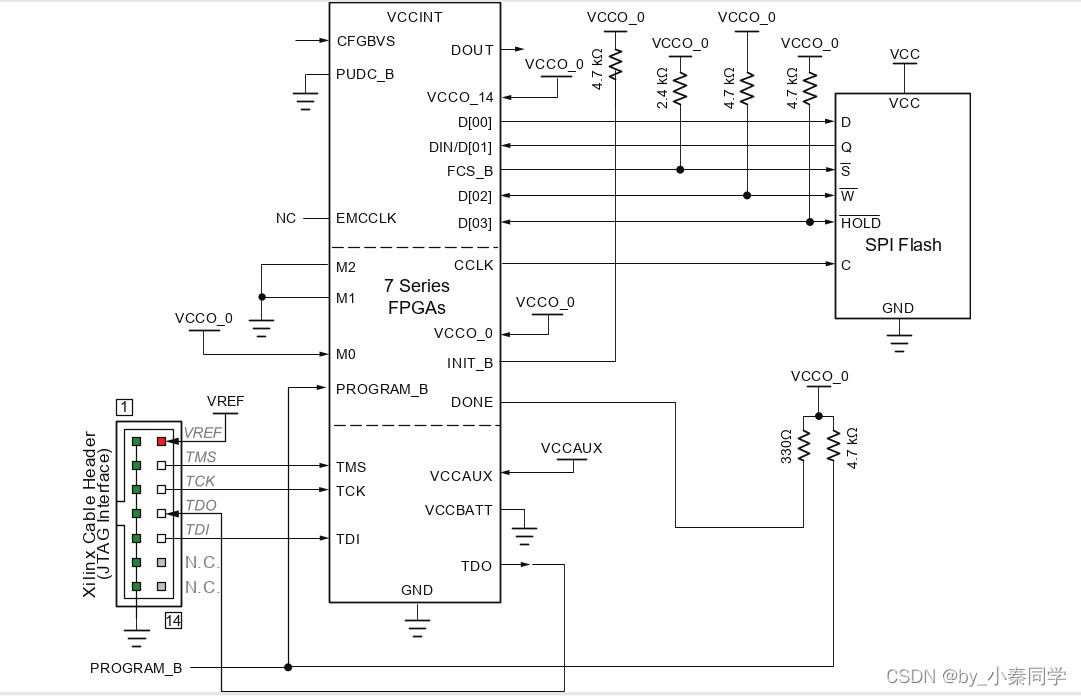

下图是vivado中官方提供的spi x4的配置电路

逻辑代码配置模式

观察图1,经过查阅官方文档,在该电路中,M0、M1、M2这3个引脚是逻辑代码配置模式选择管脚。在该模式中,M2,M1,M0为001,对应的模式为master SPI。

M[2:0]对应的配置模式表格如下表1所示

| configuration mode | M[2:0] | bus width | CCLK direction |

|---|---|---|---|

| Master Serial 主串模式 | 000 | x1 | output |

| Master SPI 主SPI | 001 | x1,x2,x4 | output |

| Master BPI 主BPI | 010 | x8,x16 | output |

| Master SelectMAP 主并模式 | 100 | x8,x16 | output |

| JTAG JTAG模式 | 101 | x1 | NOT Applicable |

| Slave SelectMAP 从并模式 | 110 | x8,x16,x32 | input |

| Slave Serial 从串模式 | 111 | x1 | inpput |

其中主从模式对应CCLK的流向。

这些配置模式对应的电路在vivado中都可以找到:tool->Edit Device Properties->configuration modes。

operties->configuration modes。

本文内容由网友自发贡献,转载请注明出处:【wpsshop博客】

推荐阅读

相关标签