热门标签

热门文章

- 1从零开始的Docker Desktop使用,Docker快速上手,Docker介绍和基础使用_docker desktop 用法

- 2Neo4j在Ubuntu 20.04上安装、配置以及Python连接使用 - Neo4j_neo4j ubuntu

- 3无人机视觉检测算法研究及数据集汇总_目标检测数据集无人机视角

- 4毕业设计:基于python的反电信诈骗管理系统_反诈数据库设计

- 5深度学习-09(目标检测:Object Detection)_深度学习目标检测

- 6Git 使用中显示“Another git process seems to be running in this repository...”问题解决

- 7基于JS和vue的sql编辑器功能的实现_前端sql编辑器

- 8pycharm加载本地数据集_pycharm使用总结

- 9【AI大模型应用开发】从CoT到ToT,再到ReAct,提升大模型推理能力的方式探索(含代码)_大模型 思维图cot

- 10OPENMV与STM32串口通信_uart.init(baudrate=115200, bits=8, parity=none, st

当前位置: article > 正文

vivado 创建和运行链路清扫_vivado phase5 sweep

作者:繁依Fanyi0 | 2024-06-14 20:21:27

赞

踩

vivado phase5 sweep

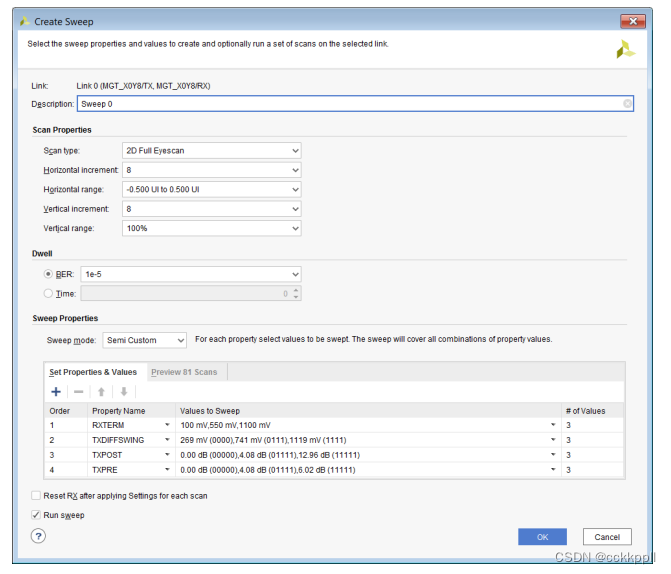

创建和运行链路清扫

要分析给定链路的裕度

,

利用不同

MGT

设置来多次运行链路扫描是很有效的。这样有助于判定最佳设置。

Vivado

Serial I/O Analyzer

功能支持您定义、运行、保存和重新调用链路清扫

,

链路清扫是由多次链路扫描集合而成的。

每条链路对应一次清扫。要创建清扫

,

请在“

Link

”窗口中选中链路

,

然后右键单击并选择“

Create Sweep

”

,

或者也

可以单击“链路

(Link)

”窗口工具栏中的“

Create Sweep

”按钮。这样将显示“创建清扫

(Create Sweep)

”对话框

,

此

对话框与“创建扫描

(Create Scan)

”对话框相似

,

差别在于前者具有额外的选项用于定义要清扫的属性以及清扫方式。

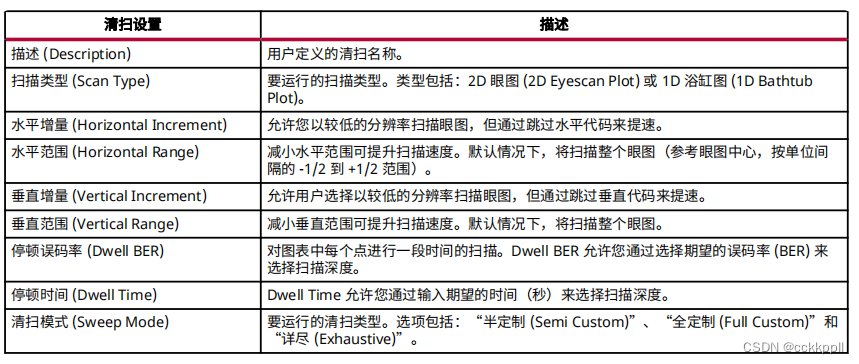

选定这些设置后

,

下一步是选择“清扫属性

(Sweep Properties)

”。所有可写链路属性都可接受清扫。要添加属性

,

请

单击左侧“

+

”按钮以在表格中添加另一行。单击“

Property Name

”即可选择要清扫的属性。

要更改值

,

请单击“

Values to Sweep Cell

”

,

并使用选择器来选择要清扫的值。如果属性不含枚举值

,

请在提供的文

本区域的每一行上输入

1

个十六进制值。

• 在下图所示的“

Semi Custom

”模式下

,

将针对每一次扫描定义每一种属性组合

,

并且将根据清扫属性来执行扫

描。可通过选中“

Preview & Scans

”选项卡来预览执行的清扫数量以及清扫顺序。

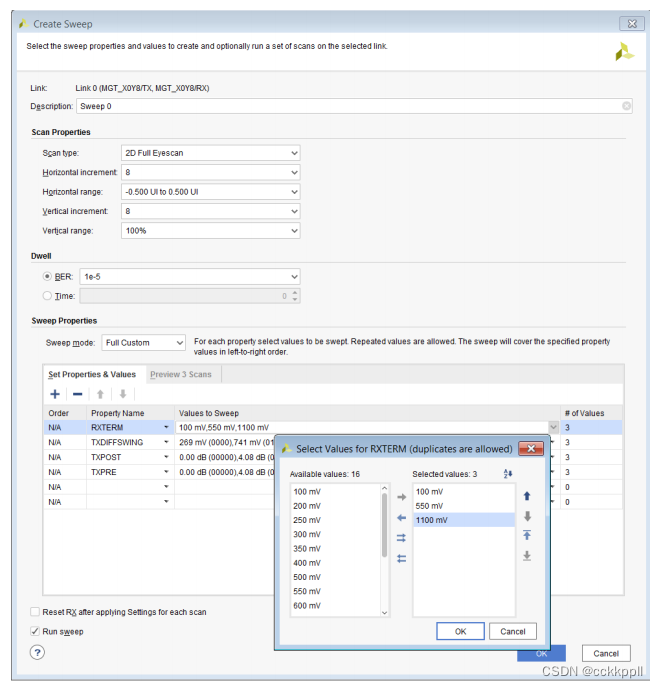

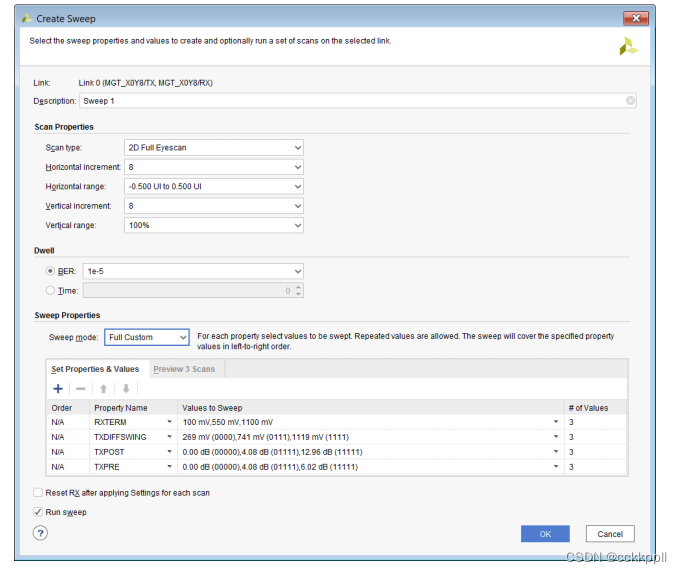

• 在“

Full Custom

”模式下

,

列出的每个属性的第一个选项用于首次扫描

,

每个属性的第二个选项用于第二次扫描

,

以此类推。如果任一属性所含选项数少于其它属性

,

则最后一个选项将用于所有后续扫描。如果属性选项全部相

同

,

但采用“

Full Custom

”作为清扫模式

,

那么只能执行

3

次扫描。

• 在“

Exhaustive

”模式下

,

“

Values to Sweep

”不可编辑

,

因为针对任一给定属性将选中所有值。

所有属性都完成设置后

,

要按顺序运行每一次扫描

,

请保持“

Run Sweep

”处于选中状态。单击“

OK

”后就会在“扫

描

(Scan)

”窗口中详细罗列扫描列表。

清扫期间

,

在“

Scan

”窗口中将跟踪进度

,

并显示最新的扫描结果。

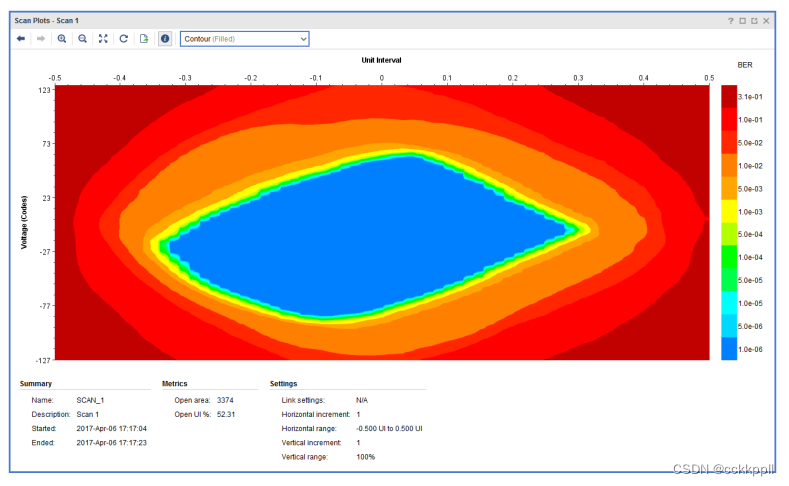

显示和浏览扫描图

创建扫描后

,

它会为扫描自动启动“扫描图

(Scan Plots)

”窗口。对于

2D

眼图扫描

,

扫描图为

BER

值组成的热图。

就像

Vivado IDE

中显示的其它图表一样

,

眼图扫描图的放大鼠标手势如下

:

• 缩放区域

(Zoom Area)

:

左键单击并从左上向右下拖动

• 缩放适应

(Zoom Fit)

:

左键单击并从右下向左上拖动

• 放大

(Zoom In)

:

左键单击并从右上向左下拖动

• 缩小

(Zoom Out)

:

左键单击并从左下向右上拖动

并且当鼠标置于图上时

,

当前水平和垂直代码以及扫描所得

BER

值都会显示在工具提示中。您还可通过单击绘图窗口

中的“

Plot Type

”按钮并选择“

Show Contour (filled), Show Contour (lines), Bathtub (Center Horizontal Line), and

Heat Map

”来更改绘图类型。

在扫描图底部会显示摘要视图

,

其中显示了扫描设置以及扫描执行时间等基本信息。在执行

2D

眼图扫描期间

,

将计算

扫描中不含任何错误的像素数量

(

将水平和垂直增量一并纳入考量

),

此结果将显示为“开放区域

(Open Area)

”。

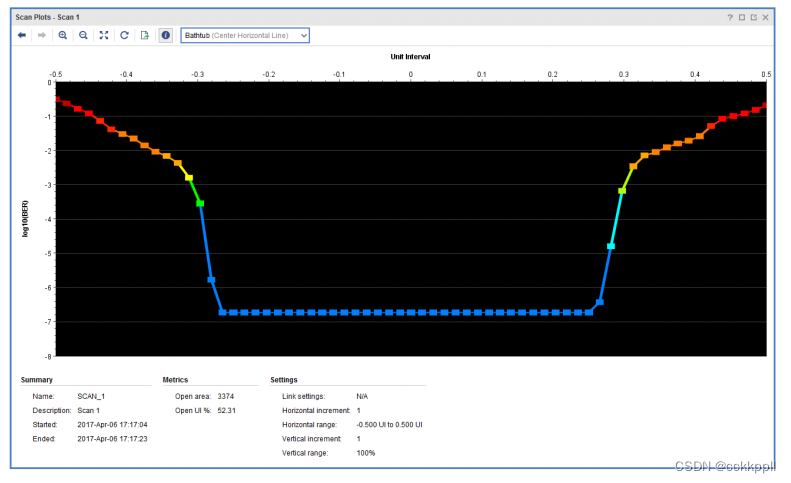

“扫描

(Scan)

”窗口内容默认情况下按“

Open Area

”排序

,

因此开放区域最大的扫描显示在顶部。下图为上图所示扫

描的浴缸图。

将扫描结果写入文件

如果由于执行了部分或完整二维眼图扫描导致存在扫描数据

,

那么可通过单击“扫描

(Scan)

”窗口中的“

Write Scan

”

按钮

,

将这些结果写入

CSV

文件。这样即可将扫描结果保存到逗号分隔格式的文件

,

并将

BER

值归入同一个区块

(

经

复制扫描图所得

)

内。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/繁依Fanyi0/article/detail/719486

推荐阅读

相关标签