- 1【Golang】Json 无法表示 float64 类型的 NaN 以及 Inf 导致的 panic_golang float nan

- 2Android之调节屏幕亮度(文末附源码)_android屏幕亮度范围

- 3毕业论文格式大全、排版技巧及常见问题汇总_csdn毕业论文格式

- 4Docker部署帆软_docker上部署finebi

- 5【赠书第25期】C#项目开发实战(微视频版)

- 6Linux等系统使用screen会话_screen会话状态

- 7基于stm32的太空人温湿度时钟项目——DHT11(HAL库)_hal库dht11(1)_dht11功率

- 8Android keyevent值中文表_android keyevent

- 9树莓派部署yolov5实现目标检测(ubuntu22.04.3)_树莓派 yolo目标检测

- 10Docker运维之最佳实践

【数字IC/FPGA】门控时钟_clock gate的电路是什么样的

赞

踩

门控时钟介绍

功耗是芯片设计中非常重要的一个指标,研究表明,在芯片功耗的组成中,有高达40%甚至更多是由时钟树消耗掉的。这个结果的原因也很直观,因为这些时钟树在系统中具有最高的切换频率,而且有很多时钟buffer,而且为了最小化时钟延时,它们通常具有很高的驱动强度。此外,即使输入和输出保持不变,接收时钟的触发器也会消耗一定的功耗。而且这些功耗主要是动态功耗。 减少时钟网络的功耗消耗,最直接的办法就是在不需要时钟的时候,把时钟关掉。这种方法就是所谓的门控时钟:clock gating。

门控时钟类别

1.与门门控

最简单的方法,就是将时钟信号和一个使能信号相与,这样,当使能信号为高电平时,时钟正常工作,低电平时,时钟被关闭,从而起到降低功耗的效果,其电路图如下所示

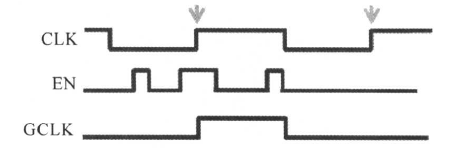

但是,这么做是有危险的。由于EN信号不受任何控制,因此很容易产生毛刺,下面是一个例子

可以看到,如果EN信号在时钟为高电平期间产生毛刺,那么相应的输出GCLK也会产生毛刺。而时钟信号产生这种毛刺是十分危险的,会造成预想不到的结果。

锁存门控

锁存门控时钟的电路图如下所示

我们结合与门门控刚刚那个例子来进行分析(下图)

1.当CLK信号为低电平时,锁存器的EN信号为高(注意EN的输入端有个非门),此时Q=EN(这个EN是外界输入的EN),但由于CLK为低,因此GCLK也为低,即CLK信号低电平时,输出GCLK恒等于CLK。

2.当CLK信号为高电平时,锁存器的EN信号为低,锁存器保存之前的值(上图中是1),因此Q=1,所以GCLK=1&CLK=CLK,可以看到,尽管EN信号毛刺,但GCLK不受毛刺的影响。

当EN信号一段时间稳定下来为低时,Q最终也会变为低,从而GCLK恒为0,时钟被关闭了。

虽然这个电路消除了毛刺的影响,但还存在着一些问题。我们看下面这个情景

在上半张图中,CLK@A和CLK@B之间存在时钟偏移(skew),锁存器的输入和输出之间也存在延时(delay),因此会造成GCLK产生毛刺。下半张图也是类似的分析方法。

寄存门控

还有一种方式就是使用寄存器对EN信号打一拍。如下图所示

来看波形图

CLKA的第四个上升沿,采样到EN信号为高,因此EN1信号拉高(图中有误),EN1再和CLKB相与,得到GCLK。除非CLKB上升沿提前CLKA很多,快半个周期,才会出现毛刺,而这种情况一般很难发生。在上图中,CLKB比CLKA迟到(这是绝大多数情况),因此不会出现毛刺。

总结

经过上面的分析,我们知道,可以采用与门门控、锁存门控和寄存门控来进行时钟门控,以此降低功耗。那么到底采用哪一种门控时钟的结构呢?通过分析,我们大概会选择寄存器结构的门控时钟,这种结构比锁存器结构的问题要少,只需要满足寄存器的建立时间就不会出现问题。

然而,在实际情况下,SOC芯片设计中使用最多的却是锁存结构的门控时钟。

原因如下:在实际的SOC芯片中,要使用大量的门控时钟单元。所以通常会把门控时钟做出一个标准单元,有工艺厂商提供。那么锁存器结构中线延时带来的问题就不存在了,因为是做成一个单元,线延时是可控和不变的。而且也可以通过挑选锁存器和增加延时,总是能满足锁存器的建立时间,这样通过工艺厂预先把门控时钟做出标准单元,这些问题都解决了。而虽然寄存门控也能达到这个效果,但是由于一个DFF是由两个锁存器组成的,采用锁存器组成门控时钟单元,可以节省一个锁存器的面积。当大量的门控时钟插入到SOC芯片中时,这个节省的面积就相当可观了。