- 1王道数据结构——线性表和单链表操作_王道数据结构相线性表和链表

- 2使用Flink实现MySQL到Kafka的数据流转换_flink 消费mysql到kafka

- 3天池NLP新闻文本分类学习赛心得-Task2_新闻文本分类项目难吗

- 4专访微软战略安全官裔云天:做好网站安全的纵深防御

- 5Nat. Rev. Genet. | 通过可解释人工智能从深度学习中获得遗传学见解

- 62024年最新猿创征文|我的技术成长之路&;&;C++_c++抽奖程序,2024年最新从零开始学大数据开发编程

- 72024简约唯美的个人引导页源码

- 8Hadoop伪分布式集群搭建_在sbin目录中vim start-dfs.sh

- 9软件测试中年危机?30岁大关?“我“该如何破局...

- 10机器学习-KNN最近邻算法原理及实践_knn算法实验原理

PLL IP 核_pll ip核

赞

踩

一、IP 核简介

在数字电路设计中,IP核是一种可重用的设计模块,它可以被集成到不同的电子系统中。这些核心可以包括各种功能,例如处理器核心、通信接口、存储控制器、数字信号处理器(DSP)等。IP核允许设计者在其项目中使用已验证和可靠的功能块,从而提高设计效率和降低开发成本。

二、PLL IP核概述

PLL(Phase-Locked Loop,锁相环)是一种电路或系统,用于同步一个信号的相位和频率与另一个参考信号保持一致。PLL通常由以下几个主要组件组成:

-

相位频率检测器(PFD,Phase-Frequency Detector): PFD用于比较两个输入信号的相位和频率差异,并产生一个误差信号。

-

电荷泵(Charge Pump): 电荷泵接收PFD的误差信号,并将其转换为一个电流,该电流用于控制VCO的频率。

-

电压控制振荡器(VCO,Voltage-Controlled Oscillator): VCO是一个产生频率可调输出信号的振荡器,其频率受电流或电压的控制。

-

分频器(Divider): 分频器将VCO的输出信号进行分频,以产生反馈信号,用于与输入信号进行比较。

-

环路滤波器(Loop Filter): 环路滤波器用于平滑控制电流,以确保PLL系统的稳定性和响应速度。

PLL的工作原理是通过不断调整VCO的频率,使得反馈信号的相位和频率与参考信号保持一致,从而实现锁相。这种锁相的特性使得PLL在许多应用中都非常有用,例如时钟生成、通信系统、射频应用等。

Quartus II 软件提供了锁相环 PLL 的 IP 核,对时钟网络进行系统级的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程占空比的功能。

三、创建PLL IP核

(一)实验目的

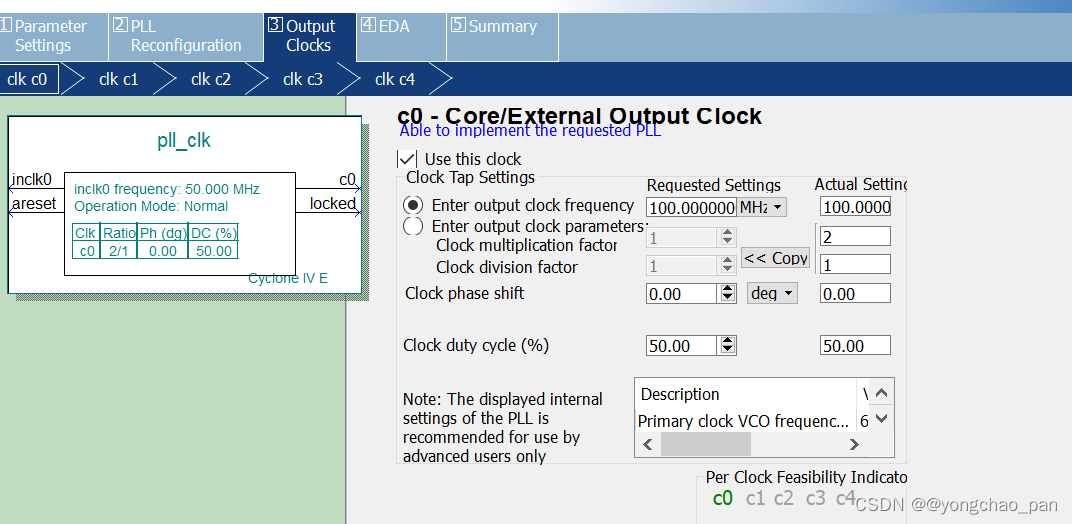

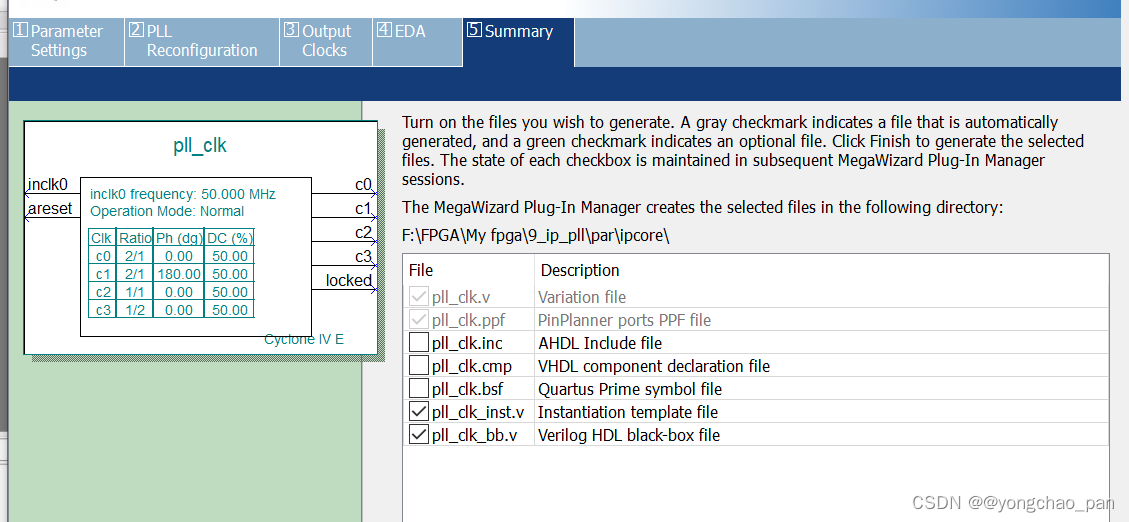

将 ALTPLL IP 核产生的四个时钟,输出到 FPGA 的扩展口 IO 上,时钟分别是 100Mhz、100Mhz (相位偏移 180 度)、50Mhz和 25Mhz 。假定系统时钟是50Mhz,要实现50Mhz以上的倍频,需要借助锁相环来实现。25Mhz只需要进行二分频然后输出。

(二)Quartus创建IP核

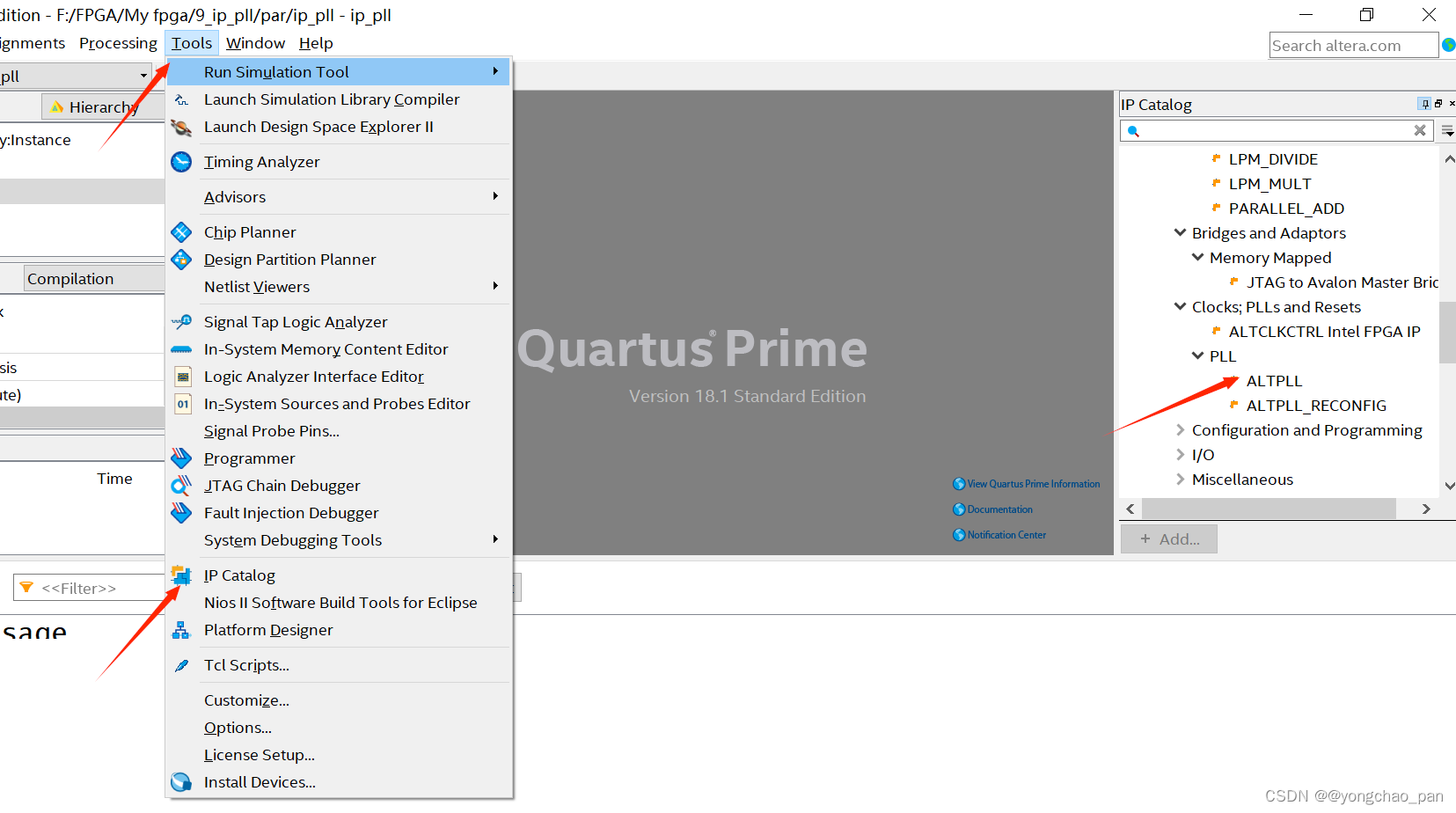

找到TOOLS——IP Catalog——ALTPLL

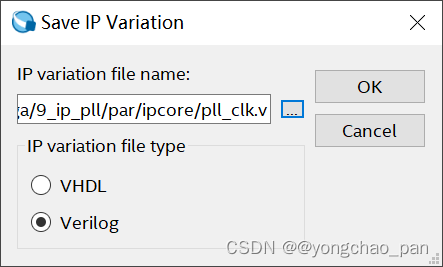

选择语言为Verilog,选择存放IP核路径,一般放在par文件夹下的ipcore文件中

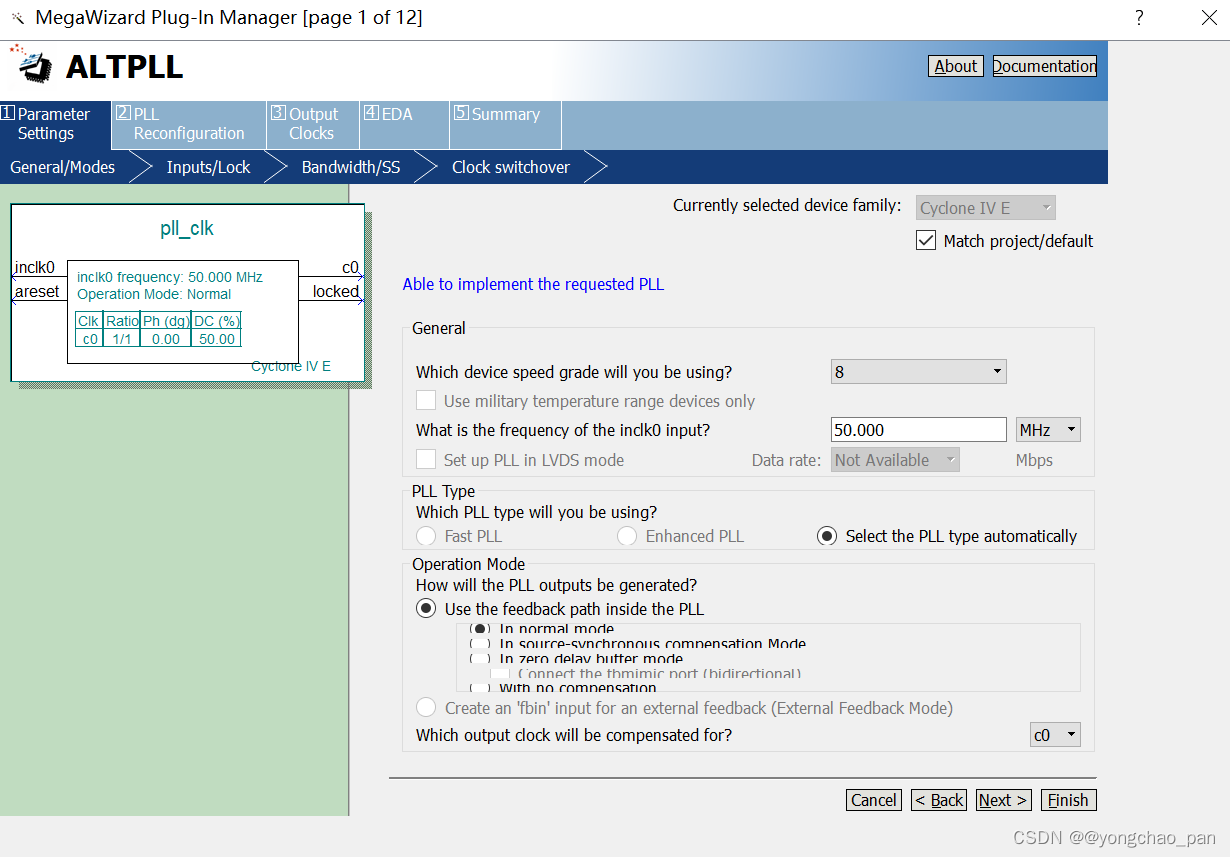

修改相关参数,速度等级,时钟频率,时钟模式。其中时钟模式一般默认标准模式。

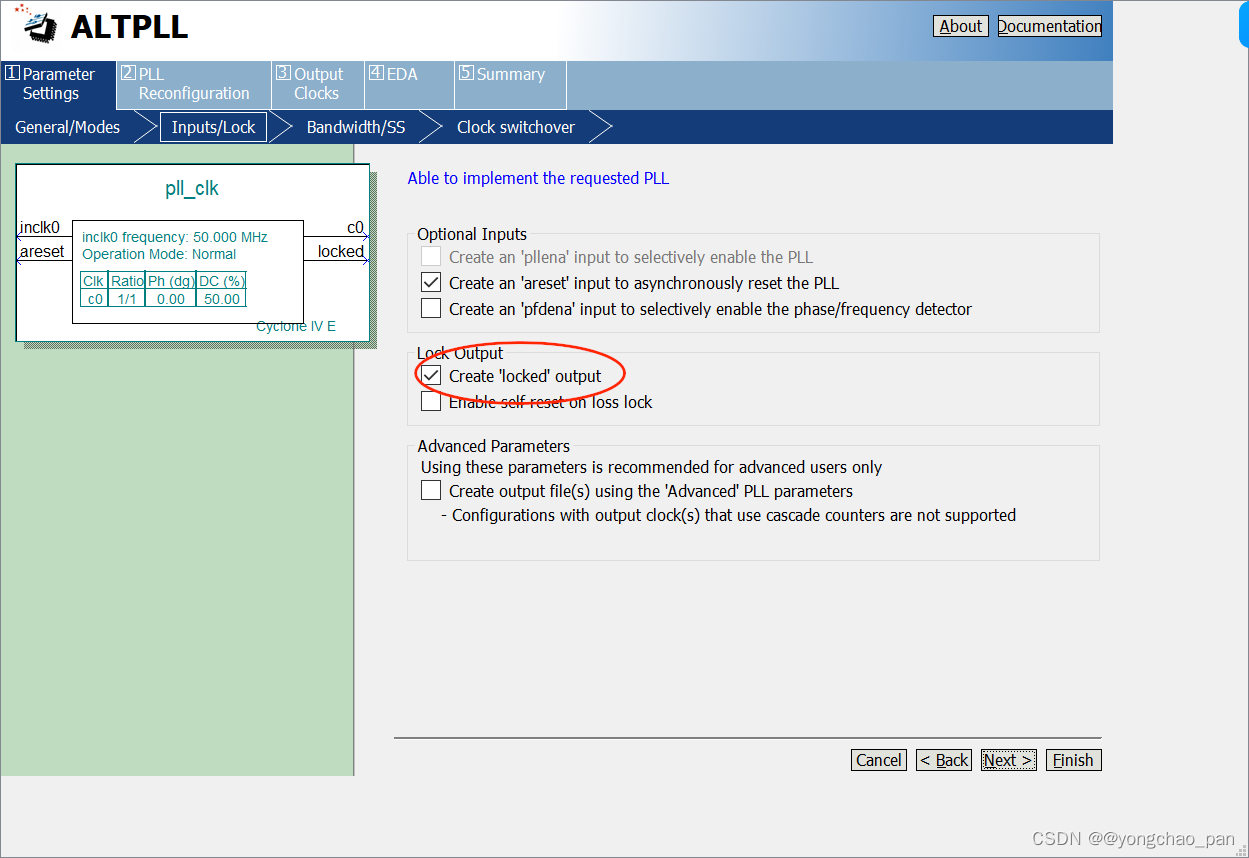

可以通过添加lock信号来看输出的时钟是否稳定

然后一路next到输出参数设置,设置需要输出的时钟频率、相位要求和占空等。

点击yes添加到工程

(三)时钟反馈模式

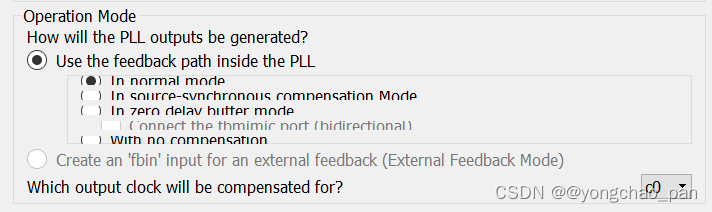

如下图所示,在PLL参数配置界面会出现4种时钟反馈模式选择。

1.标准模式

标准模式中的内部时钟是与输入时钟管脚相位对齐的。如果在该模式中连接外部时钟 输出管脚,则外部时钟输出管脚会产生相对于时钟输入管脚的相位延迟。Quartus II 软件时序分析将报告两者之间的相位差别。在标准模式下,PLL 将对 GCLK 网络所产生的延迟进行完全补偿。

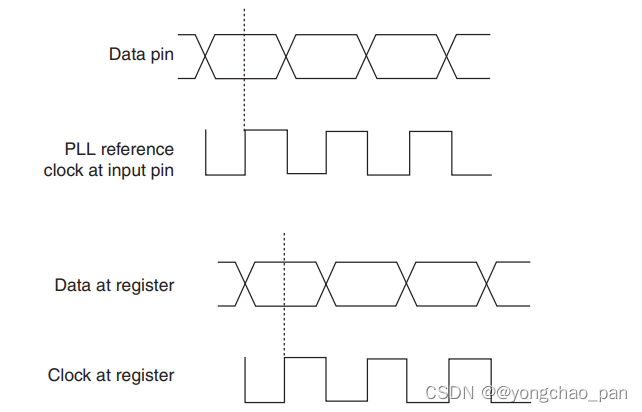

2.源同步模式

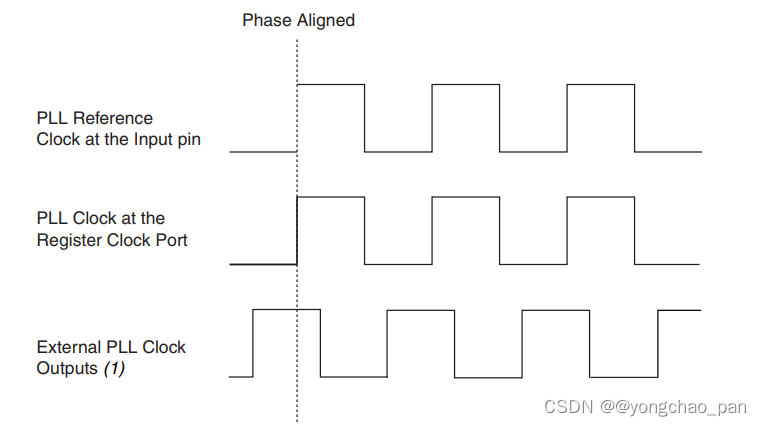

在时钟经过锁相环的前后,时钟与输入数据之间的相位关系保持不变。如果数据和时钟同时到达输入管脚,那么在 I/O 单元输入寄存器的数据与时钟端口,数据与时钟之间的相位关系保持不变。如下图所示。

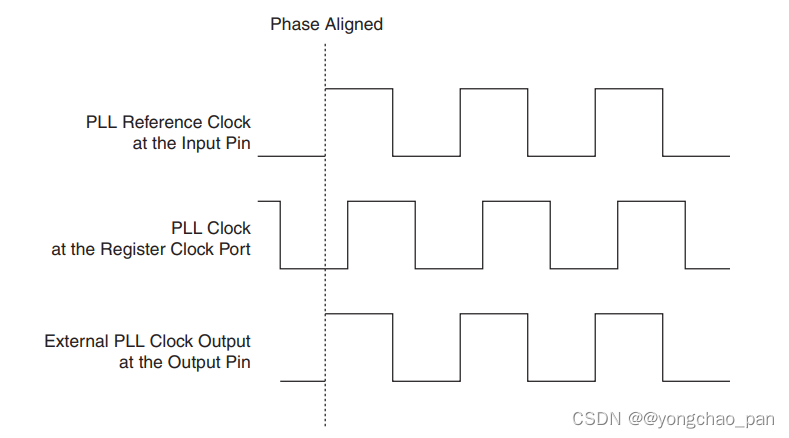

3.零延迟缓冲模式

在零延迟缓冲 (ZDB) 模式中,外部时钟输出管脚与时钟输入管脚是相位对齐的,没有 延迟。当使用该模式时,需要在输入时钟与输出时钟上使用同一 I/O 标准,以保证输入与输出管脚上的时钟对齐。

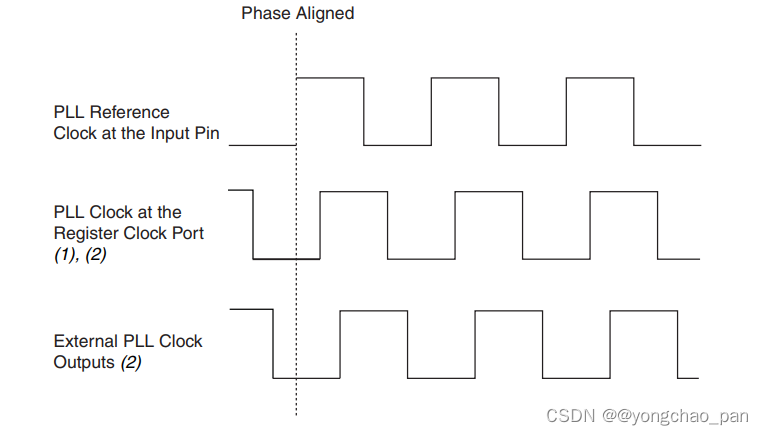

4.无补偿模式

在无补偿模式中,PLL 不对任何时钟网络进行补偿。这样会有更佳的抖动性能,因为反馈到 PFD 中的时钟不经过某些电路。相对 PLL 时钟输入,PLL 内部以及外部时钟输出均 有相位偏移。

四、PLL IP 核的使用

(一)代码实现

在该工程下创建一个.v文件,写好输入输出。然后找到文件路径par-ipcore-pll_clk_inst.v文件,将里面的例化代码复制到创建的.v文件下。修改端口名。需要注意的是,锁相环PLL默认是高电平复位,低电平处于工作状态,而系统复位是低电平复位,因此需要再例化时对系统复位取反。代码如下:

- module ip_pll(

- input sys_clk,

- input sys_rst_n,

-

- output clk_25,

- output clk_50,

- output clk_100,

- output clk_100_180deg

-

- );

-

-

- wire rst_n ; //复位信号

- wire locked ; //locked信号拉高,锁相环开始稳定输出时钟

-

-

- //系统复位与锁相环locked相与,作为其它模块的复位信号

- assign rst_n = sys_rst_n & locked;//当Locked信号拉高之后,代表输出时钟稳定,再去给其他模块使用

-

- pll_clk u_pll_clk_inst (

- .areset ( ~sys_rst_n ),

- .inclk0 ( sys_clk ),

- .c0 ( clk_100 ),

- .c1 ( clk_100_180deg ),

- .c2 ( clk_50 ),

- .c3 ( clk_25 ),

- .locked ( locked )

- );

-

-

- endmodule

(二)添加时序约束

Tools—Time Analyzer—Netlist—Creating Timing Netlist—选择post-may—ok

constraints—Creat Clock—设置参数—Targets选择端口—List—将sys_clk添加到右栏,点击OK

Task里面点击Update Timing Netlist

Constraints—Derive PLL Clock—Run—再点击Update Timing Netlist

write SDC files

将生成的SDC文件添加到工程

然后分配引脚

五、PLL IP 核的仿真

(一)测试文件

- `timescale 1ns/1ns

-

- module ip_pll_tb() ;

-

- parameter SYS_PERIOD = 20; //定义系统时钟周期

-

- reg clk ;

- reg rst_n ;

-

- wire clk_100m ;

- wire clk_100m_180deg ;

- wire clk_50m ;

- wire clk_25m ;

-

- always #(SYS_PERIOD/2) clk <= ~clk ;

-

- initial begin

- clk <= 1'b0 ;

- rst_n <= 1'b0 ;

- #(20*SYS_PERIOD)

- rst_n <= 1'b1 ;

- end

- //例化ip_pll模块

- ip_pll u_ip_pll(

- .sys_clk (clk),

- .sys_rst_n (rst_n),

- .clk_100m (clk_100m ),

- .clk_100m_180deg (clk_100m_180deg),

- .clk_50m (clk_50m ),

- .clk_25m (clk_25m )

- );

- endmodule

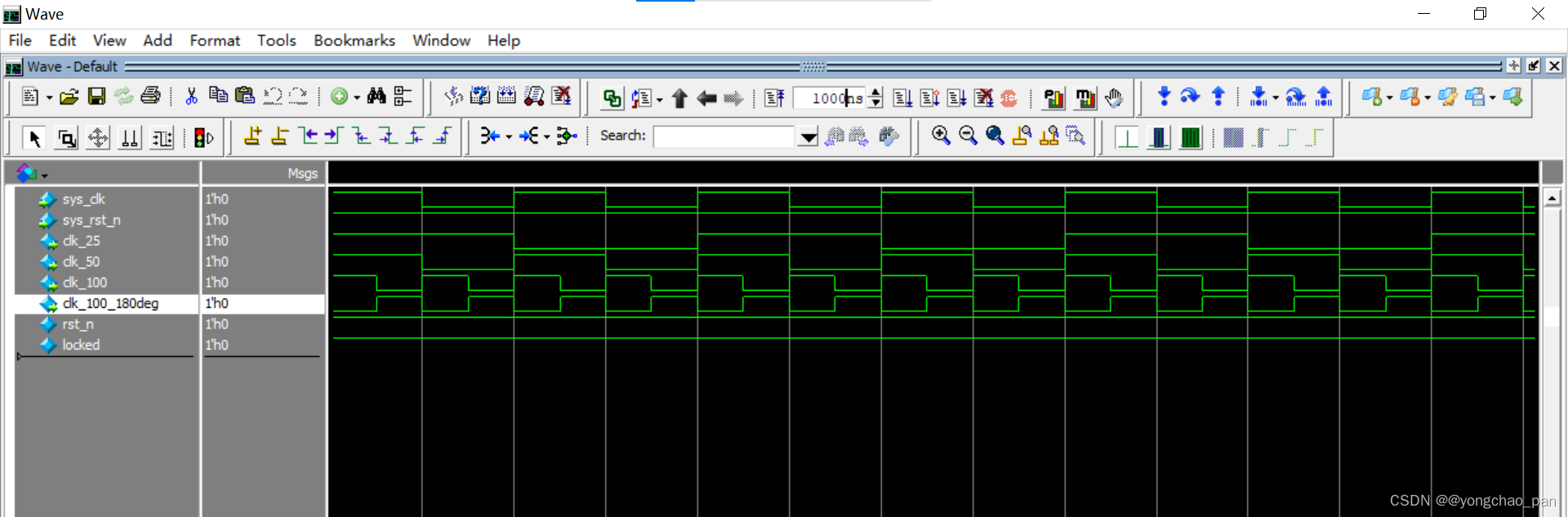

(二)ModelSim仿真

注意在添加仿真文件时,要把锁相环的文件也添加进去,放在par-ipcore-pll_clk.v下面。同时还需要记得把仿真库加进来。打开Quartus软件安装目录,altera_mf.v文件一般放在安装目录的eda-sim_lib文件夹下面,然后将该文件复制到我们所在工程的sim文件夹下面。然后将该文件在ModelSim中添加到工程,重新编译仿真。波形图如下:

###本文参考正点原子视频,如有侵权,请联系删除。