热门标签

热门文章

- 1Python 告诉你绝不知道的1983-2018 春晚

- 2Postman 使用方法详解_postman登录网页后怎么在app上看

- 3jetson 系列 安装完jetpack/已安装 tensorrt 在虚拟环境中仍然报 no module named tensorrt >> 在虚拟环境建立软连接_tensorrt: export failure 6.2s: no module named '

- 4【面经】深信服测试开发岗面经一面+二面+hr面面经---2019-10中旬_深信服测试工程师二面内容

- 5两大智能合约签名验证漏洞分析_25 - signature replay attacks

- 6计算机无法登录用户名是怎么回事,win10无法登录到你的账户是怎么回事(教你两个方法解决问题)...

- 7161基于matlab的快速谱峭度方法

- 8IntelliJ IDEA 2020 如何解决Commit: Local Changes Refresh提交Git代码卡住超级慢(已解决)

- 9攻击方式 ---- SSH暴力破解_ssh 攻击

- 10OpenCV的Delaunay三角剖分和Voronoi图的实现_c#delaunay三角形变形

当前位置: article > 正文

【FPGA】Verilog:实现十六进制七段数码管显示 | 7-Segment Display_verilog多人表决器得票数用七段数码管显示

作者:羊村懒王 | 2024-02-25 02:42:50

赞

踩

verilog多人表决器得票数用七段数码管显示

写在前面:本章主要内容为理解七点数码管显示的概念,并使用 Verilog 实现。生成输入信号后通过仿真确认各门的动作,通过 FPGA 检查在 Verilog 中实现的电路的操作。

Ⅰ. 前置知识

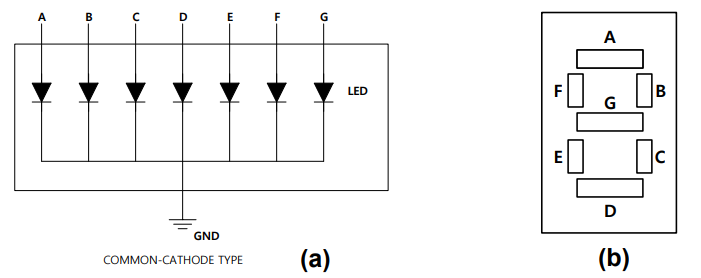

七段数码管是利用多重输出功能的非常有用的元件。该元件用于字符化,如十进制、十六进制数等。适当配置 7 个 元件,如图(a)所示,在每个端子上施加电压(logic "1"),使其发光,从而呈现字形(图b)。

数码管的一种是半导体发光器件,数码管可分为七段数码管和八段数码管,区别在于八段数码管比七段数码管多一个用于显示小数点的发光二极管单元 (decimal point)。

七段数码管的工作原理

多个发光二极管封装在一起的七

推荐阅读

相关标签