- 1垂直滤波和水平滤波的区别_变声导论-变声器原理及实现(基音分类与滤波系统实现)...

- 22023最新高薪岗位大爆料,大模型算法工程师!凭什么人均月薪50K_大语言模型工资csdn

- 3中间件的分类_操作系统数据库中间件归位哪一类

- 4中间件_c++中间件

- 5ASM磁盘管理:从初始化参数到自动化管理的全面解析_oracle asm文件自动管理参数

- 6python学习 文本特征提取(二) CountVectorizer TfidfVectorizer 中文处理_countvectorizer中文

- 7生动说明Transformer,BERT,预训练模型的含义和关系_bert和transformer的关系

- 8手把手教会你如何通过ChatGPT API实现上下文对话_js调用chatgptapi回答上下文

- 9word2vec结合TF_IDF进行多标签文本分类(三)_word2vec和tfidf的结合

- 10C#测试调用PaddleSharp模块识别图片文字_paddleocrsharp

LUT是如何实现千万种逻辑结构的_lut电路

赞

踩

目录

(4)LUT实现C = A + B(A:1bit B:1bit)

(1)FPGA和LUT简介

FPGA是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,具有不同的结构,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

LUT指显示查找表(Look-Up-Table),本质上就是一个RAM。它把数据事先(很重要,由分析综合工具完成)写入RAM后,每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

非常重要的概念:输入的信号 <====> 输入的地址 ===> 输出结果

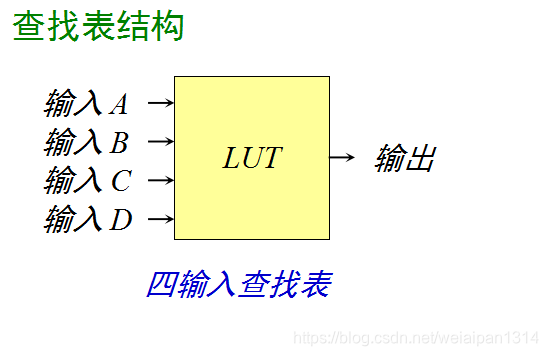

(2)LUT框图结构

下图为四输入查找表结构。xilinx FPGA内部是通过六输入查找表实现的。

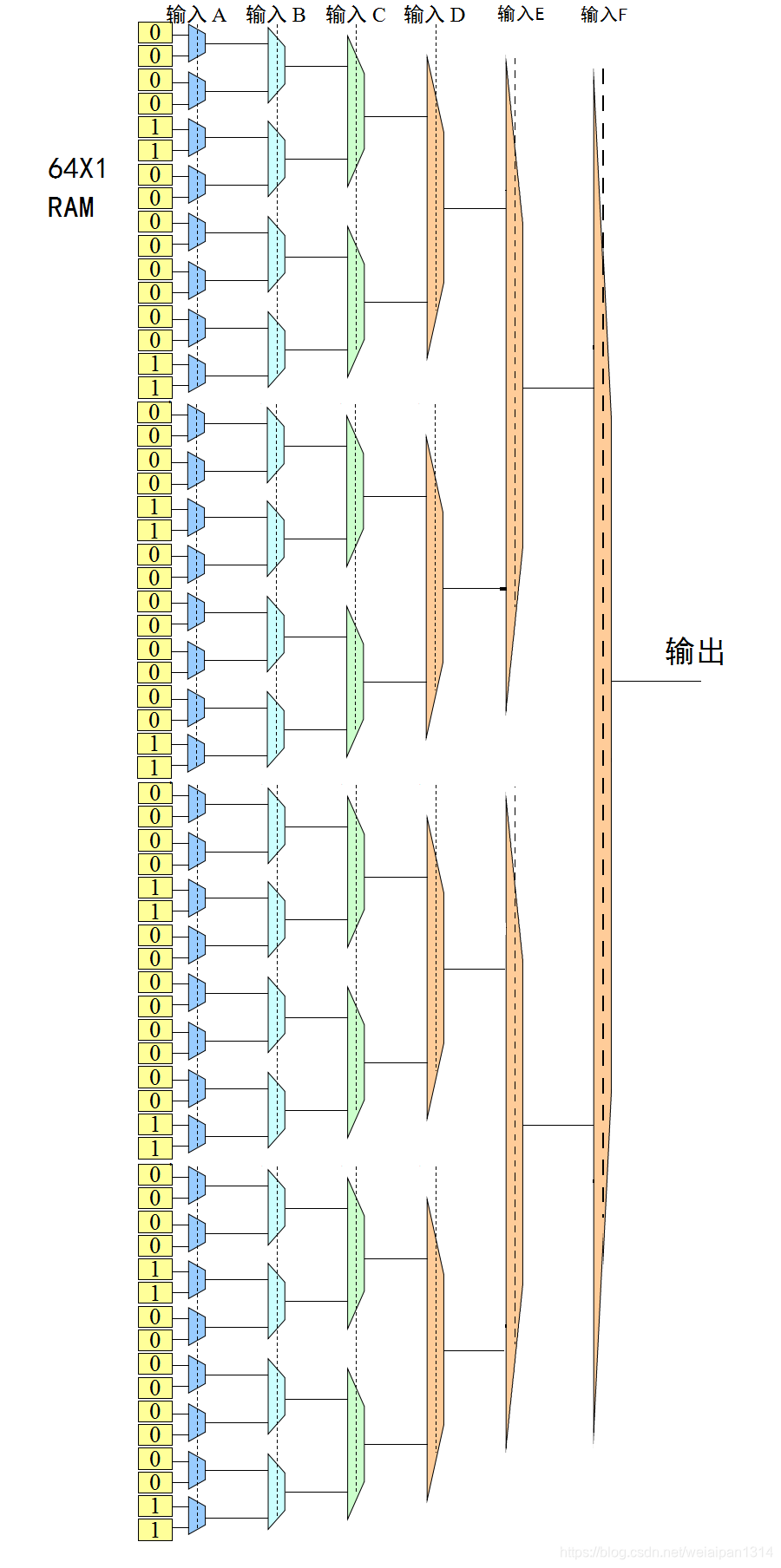

(3)LUT内部结构

从图中可以看出,LUT是通过RAM实现的,4输入LUT通过16X1 RAM实现了,6输入查找表通过64X1 RAM实现。

下图为4输入查找表内部结构:

下图为6输入查找表内部结构:

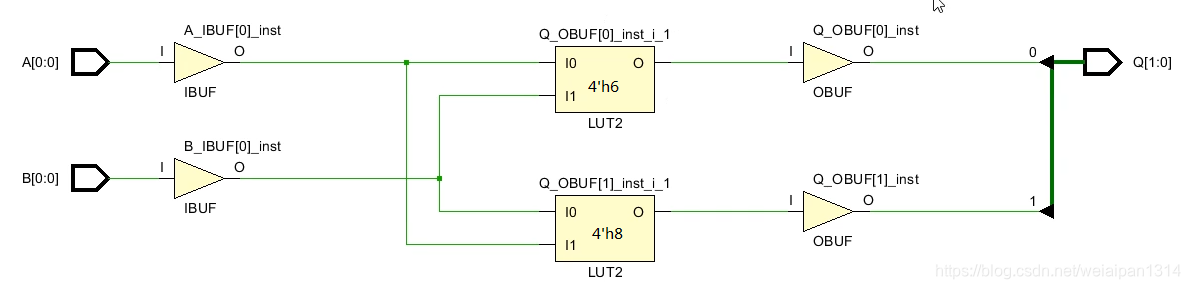

(4)LUT实现C = A + B(A:1bit B:1bit)

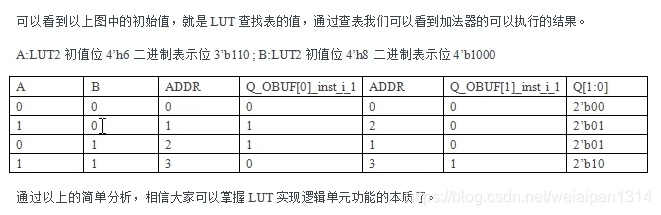

综合完毕之后,可以查看电路如下,查找表1被初始化为4'h6(3'b110),查找表2被初始化为4'h8(3'b1000)。

可以推断A+B以下的四种情况:

当A为0,B为0时,2个查找表输入的地址都为0,因此第1个查找表输出4'h6(3'b110)第0位0,第2个查找表输出'h8(3'b1000)第0位0,因此Q的值为2'b00 = 0; ==> 0 + 0 = 0

当A为1,B为0时,第1个查找表输入的地址为1,第2个查找表输入的地址为2,因此第1个查找表输出4'h6(3'b110)第1位1,第二个查找表输出'h8(3'b1000)第2位0,因此Q的值为2'b01 = 1; ==> 1 + 0 = 1

当A为0,B为1时,第1个查找表输入的地址为2,第2个查找表输入的地址为1,因此第1个查找表输出4'h6(3'b110)第2位1,第二个查找表输出'h8(3'b1000)第1位0,因此Q的值为2'b01 = 1; ==> 0 + 1 = 1

当A为1,B为1时,两个查找表输入的地址都为3,两个因此第一个查找表输出4'h6(3'b0110)第3位0,第二个查找表输出'h8(3'b1000)第3位1,因此Q的值为2'b10 = 2。 ==> 1 + 1 = 2

哈哈,是不感觉很费劲呢?如果你看下C = A+B(A、B都是5位的时候)会更加复杂,此时会用到Slice内部复杂的进位链逻辑快。因此我们只要知道原理就行,上面的操作综合分析工具和LUT已经帮我们做了,大家细细品味。下面列了一个表:

(5)总结LUT实现逻辑原理

本质上来说,就是把我们输入的数据作为LUT的地址信号,然后查找出预先定义好的逻辑结果,这个就是逻辑代码实现原理。编译器在编译verilog代码的时候会遍历所有逻辑输入并且计算出输出存入RAM里面,在硬件运行的时候根据线上的当前状态确定LUT输出从而实现了数字电路的一切设计逻辑。

1.本文部分素材来源网络,版权归原作者所有,如涉及作品版权问题,请与我联系删除。

2.未经原作者允许不得转载本文内容,否则将视为侵权;

3.转载或者引用本文内容请注明来源及原作者;

4.对于不遵守此声明或者其他违法使用本文内容者,本人依法保留追究权等。

下面是我的个人微信公众号,关注【一个早起的程序员】精彩系列文章每天不断。