- 1云计算实战系列:Linux-用户管理_kali云服务器用户管理

- 2usage: conda-script.py [-h] [--no-plugins] [-V] COMMAND ...

- 3由于找不到iUtils.dll,无法继续执行代码。重新安装程序可能会解决此问题。_由于找不到iutils.dll重新安装程序可能会解决此问题

- 4【Python百宝箱】声音的数字化探索:Python引领音频奇妙世界_python声音数字化

- 5大数据技术原理及应用课实验3 :熟悉常用的HBase操作

- 6《AIGC星辰大海训练营火爆来袭!掌握大模型技术,成为AI领域翘楚!免费试听名额限时抢!》_aigc大模型应用开发 培训

- 7基于Textrank算法的两种关键词提取_采用textrank算法进行关键词提取取,并输出结果的python代码

- 8信息泄露漏洞

- 9百度语音识别开发笔记

- 10elementul el-menu 和 el-tabs两种方式实现tab切换_element的tab页面切换

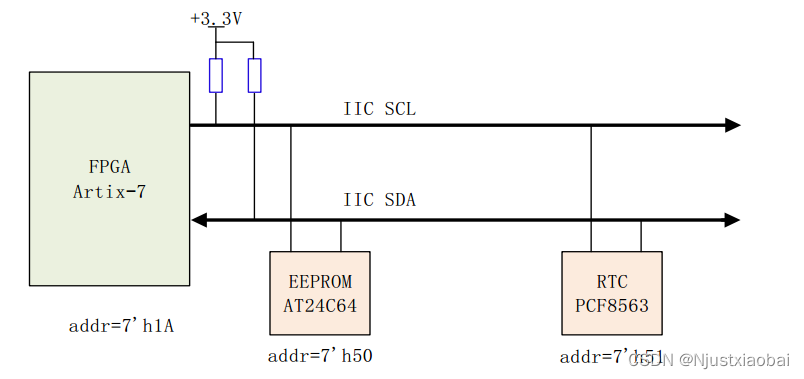

FPGA低速接口I2C,verilog实现_i2c scl持续为低

赞

踩

I2C

I2C简介

I2C 总线数据的传输速率在标准模式下可达 100kbit/s,在快速模式下可达 400kbit/s,在高速模式下可达 3.4Mbit/s(工程使用的IIC_SCL的时钟频率2.5Mbit/s)。I2C_SCL 和 I2C_SDA 均需接上拉电阻,空闲时,两条线处于高电平状态。

项目中SCL速率250K

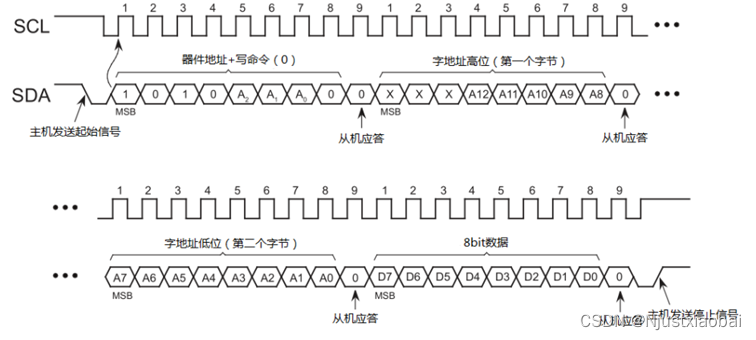

I2C传输时序

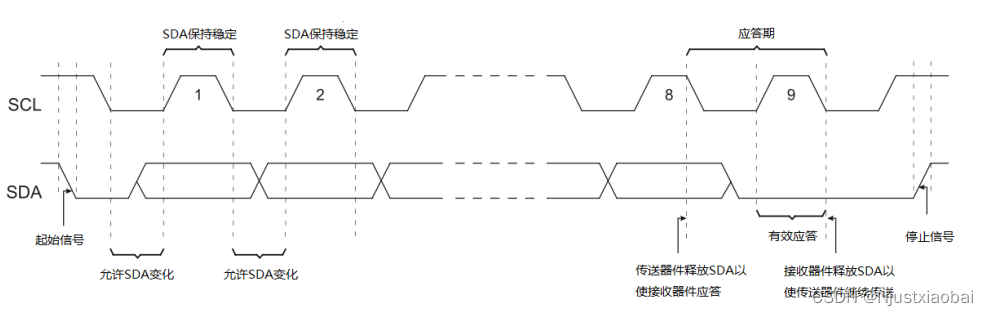

起始信号之后,主机开始发送传输的数据;在串行时钟线 SCL 为低电平状态时, SDA 允许改变传输的数据位,在 SCL 为高电平状态时, SDA 要求保持稳定,相当于一个时钟周期传输 1bit 数据,经过 8 个时钟周期后,传输了 8bit 数据,即一个字节。

第 8 个时钟周期末,主机释放 SDA 以使从机应答,在第 9 个时钟周期,从机将 SDA 拉低以应答;如果第 9 个时钟周期, SCL 为高电平时, SDA 未被检测到为低电平,视为非应答,表明此次数据传输失败。

第 9 个时钟周期末,从机释放 SDA 以使主机继续传输数据,如果主机发送停止信号,此次传输结束。

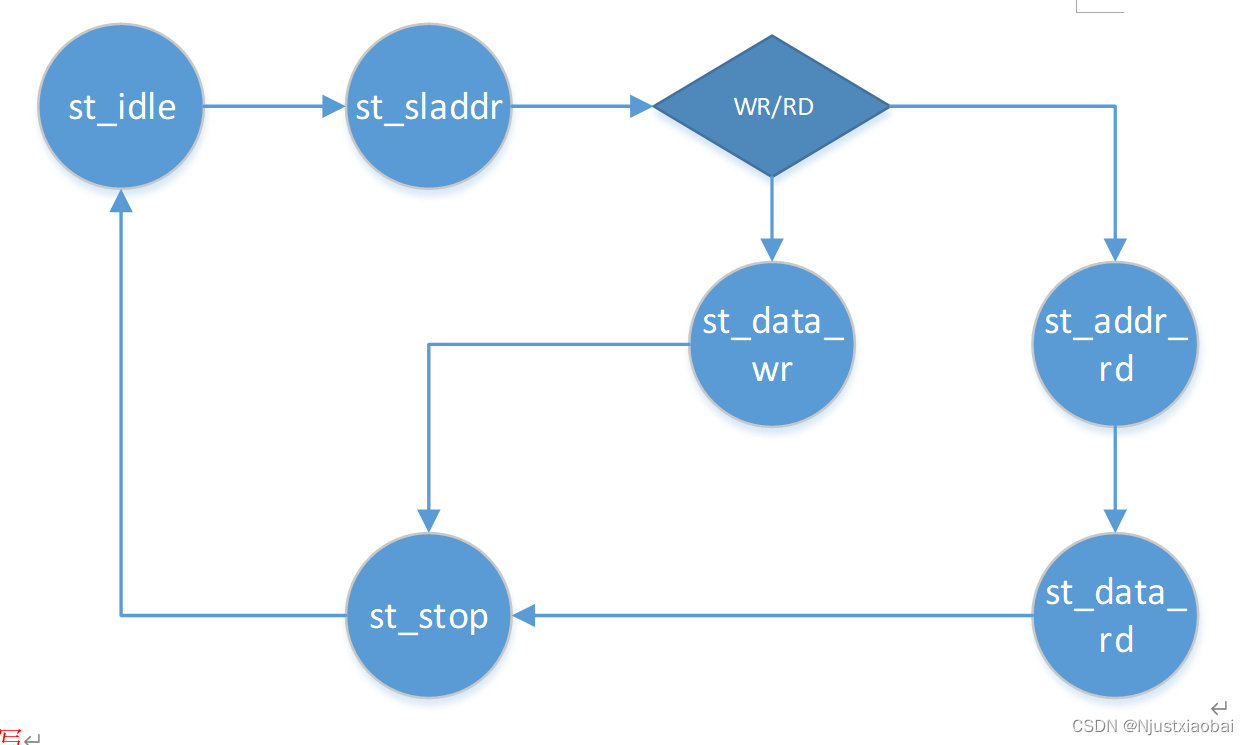

主机传送数据状态机如下

写

读

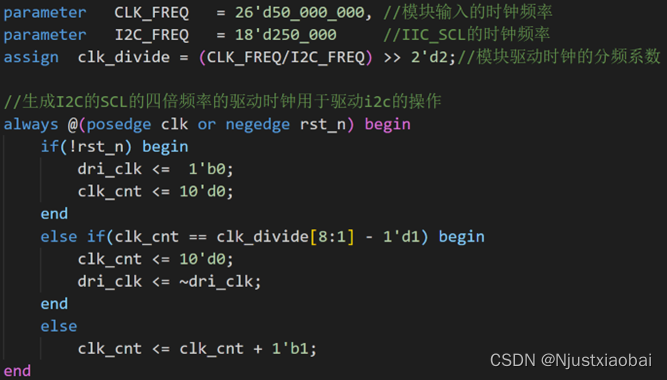

’1.生成i2c的scl四倍的时钟用于驱动i2c的操作

’1.生成i2c的scl四倍的时钟用于驱动i2c的操作

2.在3.4(4时改变sda的值)时刻scl为低,5.6时刻scl为高

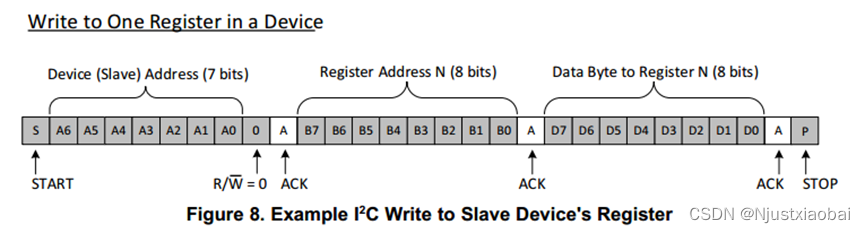

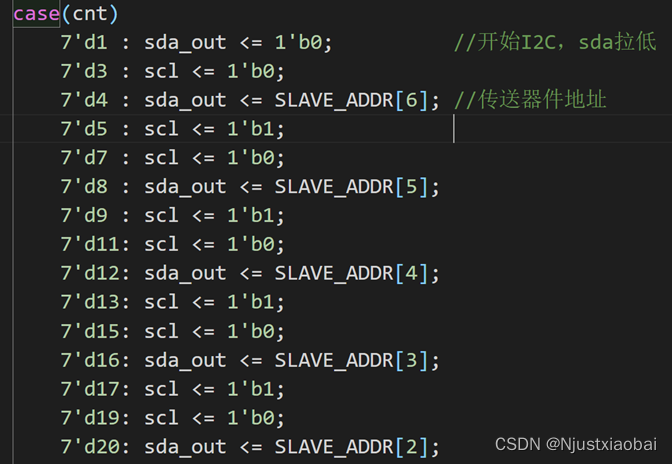

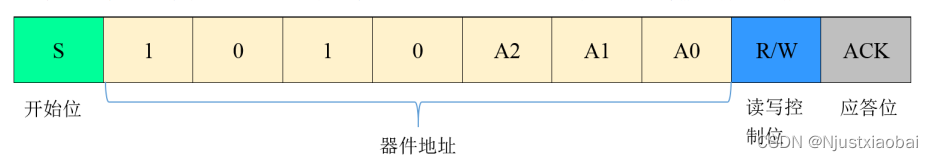

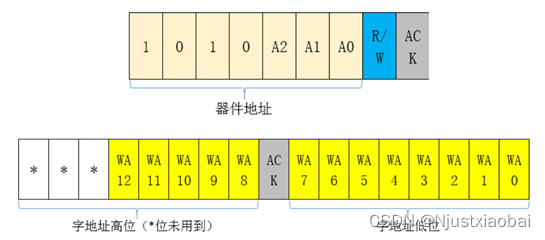

I2C传输器件地址和字地址

以AT24C64为例,器件地址为 1010 加 3 位的可编程地址, 3 位可编程地址由器件上的 3 个管脚A2、 A1、 A0的硬件连接决定。当硬件电路上分别将这三个管脚连接到 GND 或 VCC 时,就可以设置不同的可编程地址。不同的器件格式有差异

进行数据传输时,主机首先向总线上发出开始信号,对应开始位 S,然后按照从高到低的位序发送器件地址,一般为 7bit,第 8bit 位为读写控制位 R/W,该位为 0 时表示主机对从机进行写操作,当该位为 1 时表示主机对从机进行读操作,然后接收从机响应。

单次写:开始->器件地址->字地址->数据(8bit)->结束

多次写:开始->器件地址->字地址->数据(8bit)->…->数据(8bit)->结束

多次写:开始->器件地址->字地址->数据(8bit)->…->数据(8bit)->结束