- 1Spring Boot 快速入门、开发环境热部署_springboot热部署配置

- 2android逆向开发之Frida逆向基础_android逆向 frida

- 3版本匹配指南:Scipy版本、Python版本和Numpy版本的对应关系_numpy 1.23.5

- 4C语言实现平衡二叉树的插入、查找、删除_#include "stdio.h"#include "stdlib.h"typedef struc

- 5SAP 系统查询系所有 TCODE清单_sap查找收藏的tcode

- 6Promethus+Gafana-MySQL 的监控_grafana如何监控mysql慢查询

- 7隐马尔科夫模型、最大熵模型、最大熵马尔科夫、条件随机场

- 8threejs特殊几何体(一:文字几何体对象)_threejs textgeometry json字体

- 9kafka学习-基本概念与简单实战_kafkatemplate.send producerrecord

- 10Uniswap V2白皮书翻译

基于SPI实现stm32与fpga通信(二)_arm32 spi fpga

赞

踩

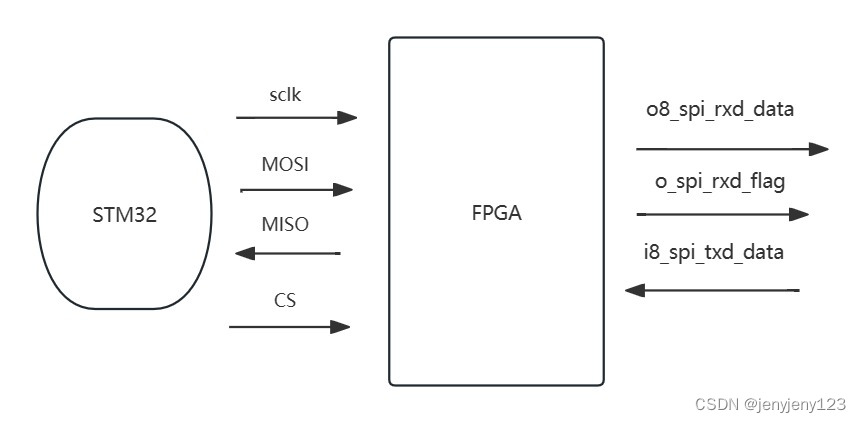

spi通信,通过片选信号cs和时钟信号sclk来接收、发送数据

| CS | 信号拉低时,主机发送数据 or 从机发送数据 |

| SCLK | 上升沿:stm32(主机)发送数据,fpga(从机)接收数据 下降沿:stm32(主机)接收数据,fpga(从机)发送数据 |

1、如何确定stm32 spi时钟边沿

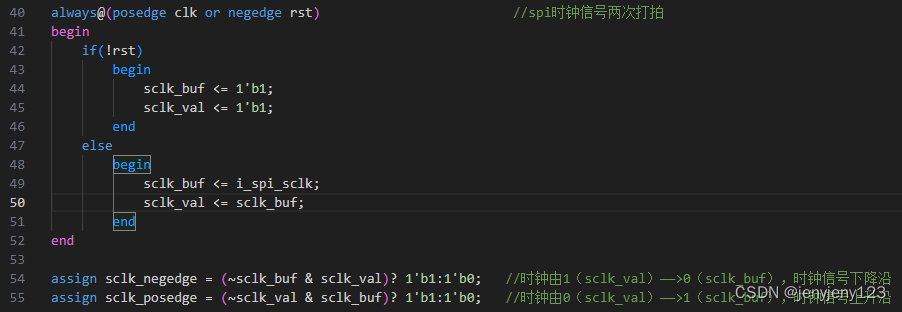

将sclk信号经过两级寄存器,对比两次缓存信号来判断时钟信号边沿:

|

2、在stm32发送数据,fpga接收数据时,怎么判断接受数据是否接收完毕

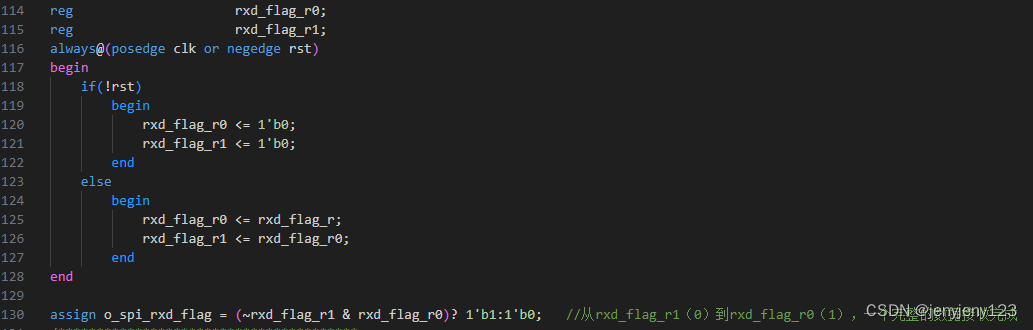

如果是串行接受8bit位宽的数据,在接受第一位数据时,给flag标志位rxd_flag_r置0,当全部接收完8位数据,给rxd_flag_r标志位置1。

|

那么,当标志位由0变为1的下降沿到来时,表示fpga从机数据接收完成。该完成标志位需要输出,在进行MOSI接收数据解析时用到;

3、在stm32数据接受端,是否需要判断来自fpga的数据全部被接收到

在SPI通信中,STM32作为主机,FPGA作为从机,通常是通过轮询方式来判断接收是否完成的。

在STM32中,可以通过以下方式来判断接收是否完成:

-

利用SPI的状态寄存器:SPI的状态寄存器(例如SR寄存器)中会有接收缓冲区非空的标志位(例如RXNE标志位),可以通过检查该标志位来判断接收是否完成。如果该标志位为1,说明接收缓冲区中已经有数据,即接收完成。

-

使用SPI的中断:可以配置SPI相关的接收中断,当接收完成时,会触发相应的中断服务程序(ISR),在中断服务程序中进行相关处理。

具体的实现方法如下:

-

轮询方式的实现:

- while (1) {

- if (SPI_I2S_GetFlagStatus(SPIx, SPI_I2S_FLAG_RXNE)) {

- // 接收完成

- uint8_t receivedData = SPI_I2S_ReceiveData(SPIx);

- // 其他处理

- }

- }

在轮询方式下,通过

SPI_I2S_GetFlagStatus()函数检查接收缓冲区非空的标志位,并通过SPI_I2S_ReceiveData()函数读取接收缓冲区的数据。 -

中断方式的实现:

首先需要配置SPI相关的中断,以及编写相应的中断服务程序。

- void SPIx_IRQHandler(void) {

- if (SPI_I2S_GetITStatus(SPIx, SPI_I2S_IT_RXNE)) {

- // 接收完成

- uint8_t receivedData = SPI_I2S_ReceiveData(SPIx);

- // 其他处理

- }

- }

- int main(void) {

- // 硬件初始化等操作

- // 配置SPI中断

- NVIC_InitTypeDef NVIC_InitStructure;

- NVIC_InitStructure.NVIC_IRQChannel = SPIx_IRQn;

- NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0;

- NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;

- NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

- NVIC_Init(&NVIC_InitStructure);

- // 启用SPI接收中断

- SPI_I2S_ITConfig(SPIx, SPI_I2S_IT_RXNE, ENABLE);

- // 主循环

- while (1) {

- // 等待中断触发

- }

- }

在中断服务程序中,通过

SPI_I2S_GetITStatus()函数检查接收缓冲区非空的中断标志位,并通过SPI_I2S_ReceiveData()函数读取接收缓冲区的数据。

无论是轮询方式还是中断方式,都需要根据具体情况进行选择,以满足应用的需求。

4.从机fpga接收和发送数据的方式

在SPI通信中,STM32作为主机控制通信流程和发送数据,FPGA作为从机接收数据并回应。以下是从机FPGA接收和发送数据的方式:

-

接收数据:

- FPGA配置一个SPI接收缓冲区,用于存储接收到的数据。

- 在STM32发送数据时,FPGA通过SPI接收数据线接收来自STM32的数据。

- 当FPGA接收到数据时,将数据存储到接收缓冲区中。

-

发送数据:

- FPGA配置一个SPI发送缓冲区,用于存储待发送的数据。

- 在STM32请求FPGA发送数据时,STM32将希望发送的数据写入到FPGA的发送缓冲区中。

- FPGA读取发送缓冲区中的数据,并通过SPI发送数据线将数据传输给STM32。

- STM32接收到FPGA发送的数据后进行处理。

需要注意的是,SPI通信是全双工的,主机和从机可以同时进行发送和接收操作。因此,在实际应用中,你需要在STM32和FPGA之间约定好通信协议,以确保数据的正确传输和解析。

两个过程都涉及到fpga缓冲数据,那么fpga缓冲数据的几种方式:

-

存储器缓冲:FPGA中可以使用片上存储器(RAM)对数据进行缓冲。数据可以暂时存储在片上存储器中,待需要时再进行读取。这种方式可以提高数据读写速度,并减少对外部存储器的访问次数。

-

FIFO缓冲:FPGA中可以使用FIFO(First In, First Out)缓冲器对数据进行缓冲。FIFO是一种双端队列,数据可以按照先进先出的原则进行存储和读取。当数据产生速率和消耗速率不一致时,可以使用FIFO缓冲器进行数据调整和平衡,以避免数据丢失或溢出。

-

BRAM缓冲:FPGA中的BRAM(Block RAM)是一种高性能的片上存储器,具有较大的容量和较快的读写速度。可以将数据存储在BRAM中进行缓冲,以提高数据处理速度和效率。

-

缓冲寄存器:FPGA中的逻辑资源可以用来实现缓冲寄存器,用于存储和延迟数据。缓冲寄存器可以在数据信号的传输过程中提供临时存储和调整数据时序的功能。

-

外部存储器缓冲:在某些应用中,FPGA可能需要缓冲大量的数据,此时可以借助外部存储器设备进行缓冲。可以将数据存储在外部存储器中,然后通过FPGA与外部存储器进行数据读写交互。

需要根据具体的应用场景和设计要求选择适合的缓冲方式。在FPGA设计中,缓冲数据可以提高数据处理的效率和性能,并满足实时性要求。

因为在这个过程中可以简化为串转并(串行数据转并行数据)、并转串(并行数据转串行数据),所以在这两个过程中,fpga采用的缓冲数据模式是寄存器,将串行数据通过寄存器缓存在多bit数据中,

以下是一个使用移位寄存器接收来自主机的数据的示例代码,假设SPI接口的数据线宽度为8位:

在上述代码中,我们在时钟的上升沿处检测片选信号,当片选信号为低电平时,我们将输入的数据位移入一个8位的移位寄存器中。每次时钟上升沿到达时,寄存器向左移动一位,并将输入数据位移到最低位上。最后,我们将寄存器的值作为接收到的数据输出。

请注意,上述代码仅展示了如何使用移位寄存器接收数据,并未包括其他SPI协议相关的功能,如主机从机选择和数据传输位序等。在实际应用中,您可能需要根据具体的SPI协议要求进行相应的修改和扩展。

4、fpga从机spi模块的数据流向

时钟sclk、复位rst、单bit接收数据MOSI、单bit输出数据MISO、多bit接收到的数据o8_spi_rxd_data(8bit,串转并接收来自主机MOSI的数据,输出到下一模块)、接收数据完成标志位o_spi_rxd_flag、多bit发送的数据i8_spi_txd_data(8bit,输入到模块中,并转串通过MISO发送到主机)