热门标签

热门文章

- 1信号处理基础之噪声与降噪(二)| 时域降噪方法(平滑降噪、SVD降噪)python代码实现_信号去噪平滑度指标

- 2【网络安全 | CTF】攻防世界 simple_php 解题详析_小宁听说php是最好的语言,于是她简单学习之后写了几行php代码。

- 3MobileNet实战:tensorflow2(1),2024年最新跳槽 面试

- 4微信小程序实现 API Promise 化_微信小程序new promise

- 5GitHub的Fork的作用(Github fork 和 git clone的区别)_fork仓库的好处

- 6数据可视化分析教学课件——FineBI实验册节选====高校招生数据分析_招生、流失可视化分析

- 7【日常问题】解决git clone提示unable to access 问题_git clone unable to access

- 8【自然语言处理】【大模型】DeepSeek-V2论文解析_deepseek v2

- 9外卖扫码点餐全开源小程序源码_点餐小程序下载开源

- 10YoloV8改进策略:蒸馏改进|CWDLoss|使用蒸馏模型实现YoloV8无损涨点|特征蒸馏

当前位置: article > 正文

【紫光同创国产FPGA教程】【第十八章】AD实验之AD7606波形显示_ad7606b的寄存器读写verilog

作者:羊村懒王 | 2024-06-06 16:55:01

赞

踩

ad7606b的寄存器读写verilog

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处(http://www.alinx.com)。

适用于板卡型号:

PGL22G/PGL12G

1. 实验简介

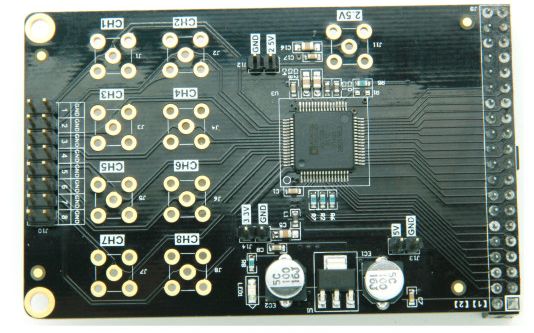

本实验练习使用ADC,实验中使用的ADC模块型号为AN706,最大采样率200Khz,精度为16位。实验中把AN706的2路输入以波形方式在HDMI上显示出来,我们可以用更加直观的方式观察波形,是一个数字示波器雏形。

8路200K采样16位ADC模块

实验预期结果

2. 实验原理

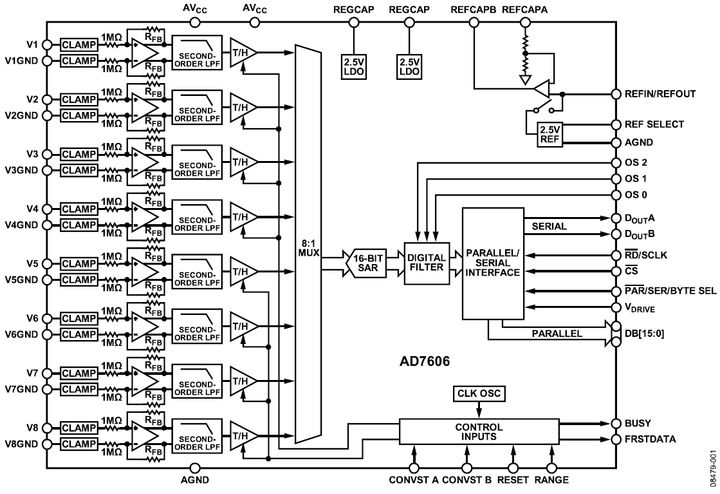

AD7606是一款集成式8通道同步采样数据采集系统,片内集成输入放大器、过压保护电路、二阶模拟抗混叠滤波器、模拟多路复用器、16位200 kSPS SAR ADC和一个数字滤波器, 2.5 V基准电压源、基准电压缓冲以及高速串行和并行接口。

AD7606采用+5V单电源供电, 可以处理±10V和±5V真双极性输入信号, 同时所有通道均以高达200KSPS的吞吐速率采样。输入钳位保护电路可以耐受最高达±16.5V的电压。

无论以何种采样频率工作, AD7606的模拟输入阻抗均为1M欧姆。它采用单电源工作方式, 具有片内滤波和高输入阻抗, 因此无需驱动运算放大器和外部双极性电源。

AD7606抗混叠滤波器的3dB截至频率为22kHz; 当采样速率为200kSPS时, 它具有40dB抗混叠抑制特性。灵活的数字滤波器采用引脚驱动, 可以改善信噪比(SNR), 并降低3dB带宽。

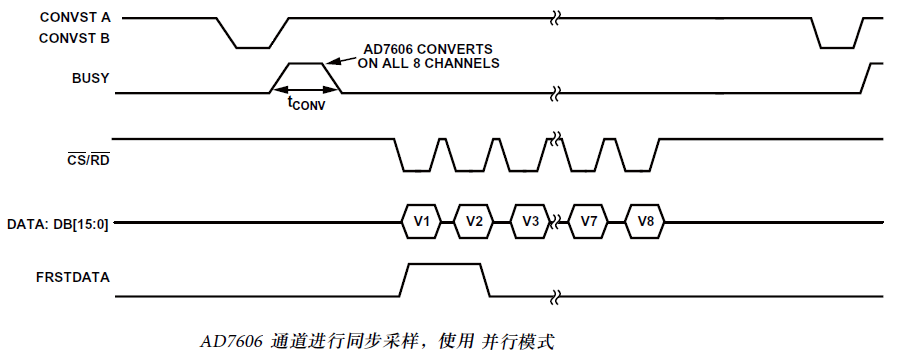

2.1 AD7606时序

AD7606可以对所有8路的模拟输入通道进行同步采样。当两个CONVST引脚(CONVSTA和CONVSTB)连在一起时ÿ

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/羊村懒王/article/detail/681780

推荐阅读

相关标签