- 1[论文总结] 智慧农业论文摘要阅读概览_oasis 文章摘要

- 2kafka源码解析(4)生产者解析之内存池_kafka we are out of memory and will have to block

- 3MySQL 8.0 OCP (1Z0-908) 考点精析-架构考点5:数据字典(Data Dictionary)_mysql ocp8 培训

- 4如何玩转github

- 5基于STM32f103c8t6的两轮自平衡小车--1(硬件准备以及OLED 屏幕显示)_平衡小车中的o显示设备

- 6红黑树增删操作详解_红黑树删除操作解决红黑冲突

- 7使用ET2000和Wireshak分析Ethercat主站的实时性_ethercat et2000

- 8信息安全-网站安全需求分析与安全保护工程(二)_iis的访问控制主要包括请求过滤、url授权控制、ip地址限制、文件授权等安全措施。

- 92024年九大最佳LangChain替代方案,打造AI助手的新选择

- 10一文总结经典卷积神经网络CNN模型_cnn网络模型汇总

【FPGA】Quartus项目工程创建以及联合Modelsim进行仿真(FPGA项目创建与仿真)_quartus 创建项目

赞

踩

目录

软件下载

这里使用的是Quartus Prime Light 18.1 以及ModelSim Intel FPGA 10.5b,两个软件在同一个地方下载,附网址https://www.intel.com/content/www/us/en/software-kit/665990/intel-quartus-prime-lite-edition-design-software-version-18-1-for-windows.html

解压过后根据提示等待安装即可,唯一需要注意的点是安装路径不要出现中文

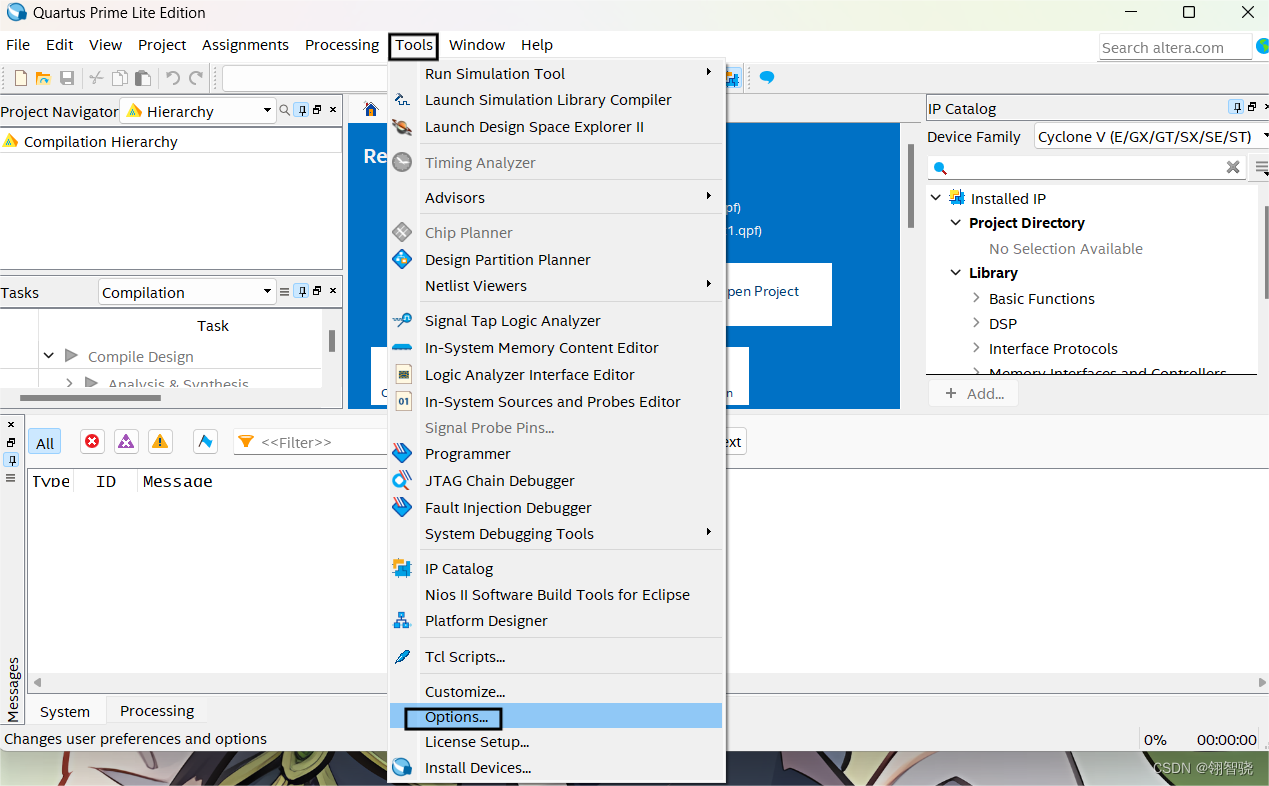

Quartus中设置Modelsim-Altera仿真器

双击打开quartus,点击Tools->options

点击EDA Tool Options,找到Modelsim-Altera并点击其后...设置仿真器路径

找到安装Quartus的文件夹,按照路径选择modelsim_ase\win32aloem文件夹,点击选择文件夹即可

设置完后点击ok保存即完成

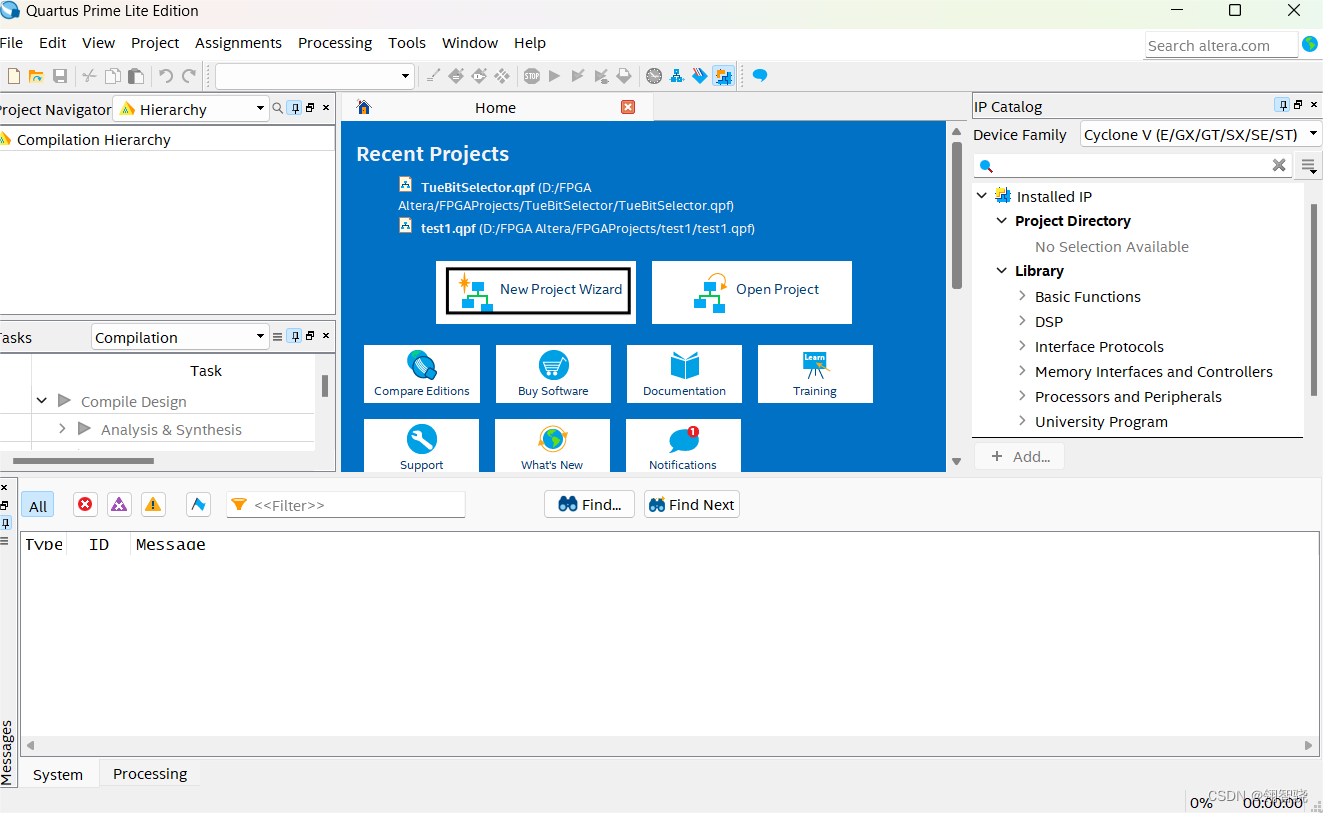

创建新项目

点击New Project Wizard

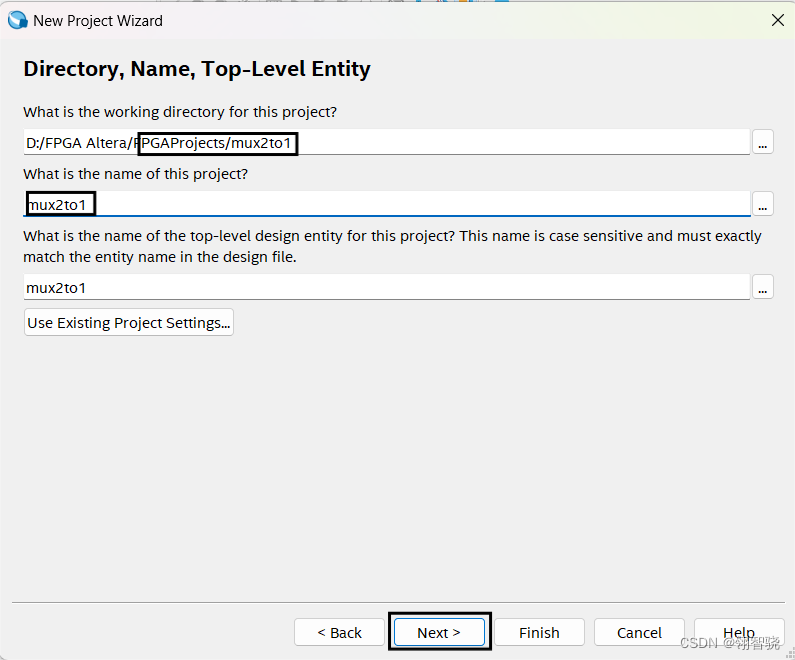

根据引导进行配置

选择项目储存的位置,同样,位置和项目名字也不要出现中文,同时项目储存文件名和项目名最好是以项目名称命名,这里以2选1数字选择器为例,点击next

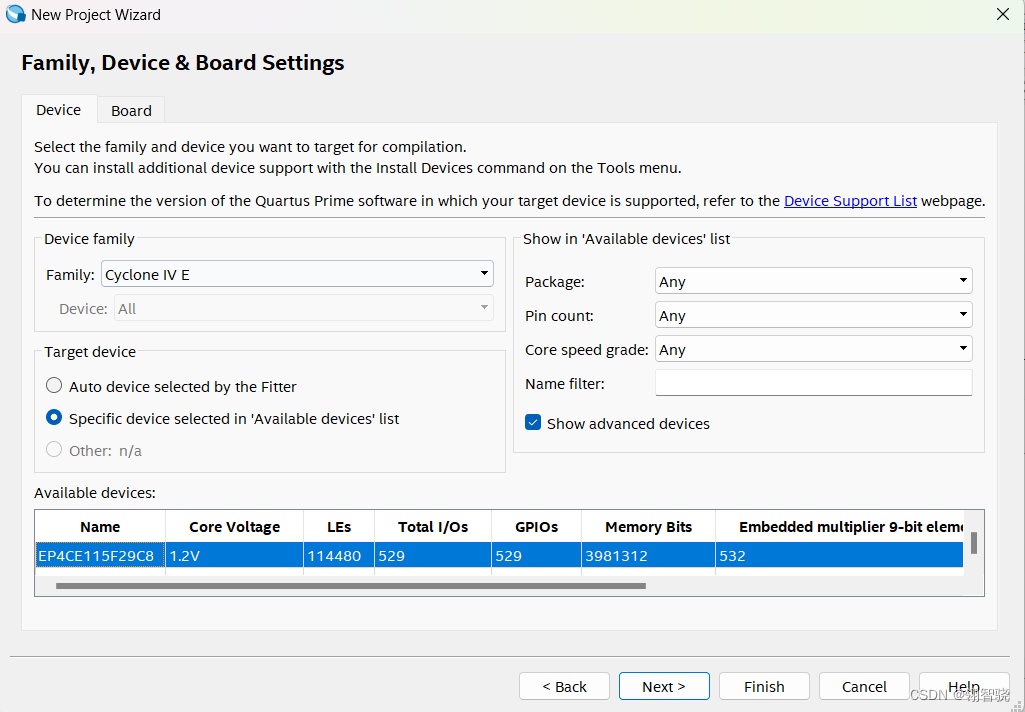

这里我们不用项目模板也没有要添加的文件,所以一直点击next来到设备选择,我这里用的是Cyclone IV系列的,选好设备后点击next

接下来来到EDA Tool Setting,在这里我们需要选择我们仿真使用的仿真器Modelsim-Altera,format选择verilog HDL

点击finish完成项目创建

编写项目代码

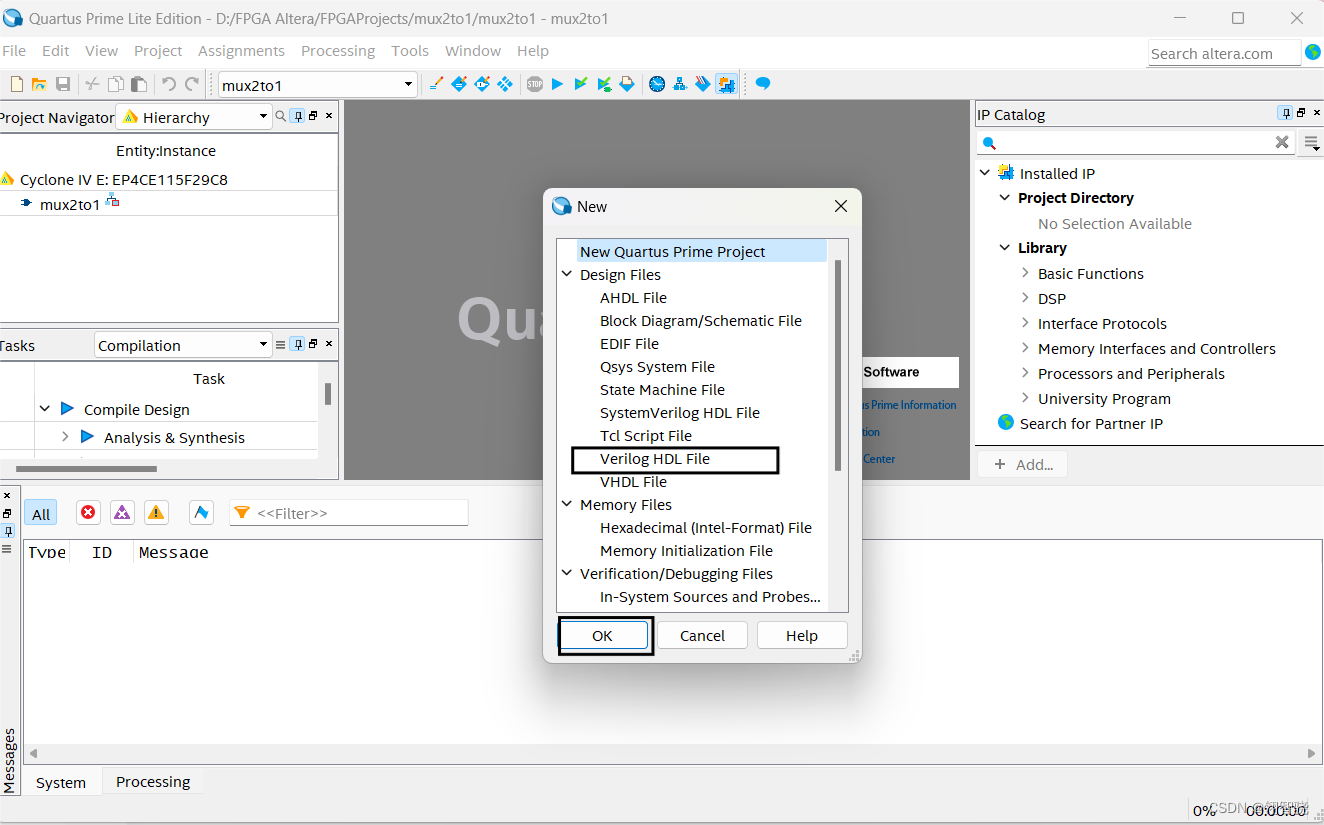

首先点击一下项目文件,然后按住Ctrl+N或者左上角 文件-New 进行verilog HDL 文件添加,选择verilog HDL File选项,点击ok确认

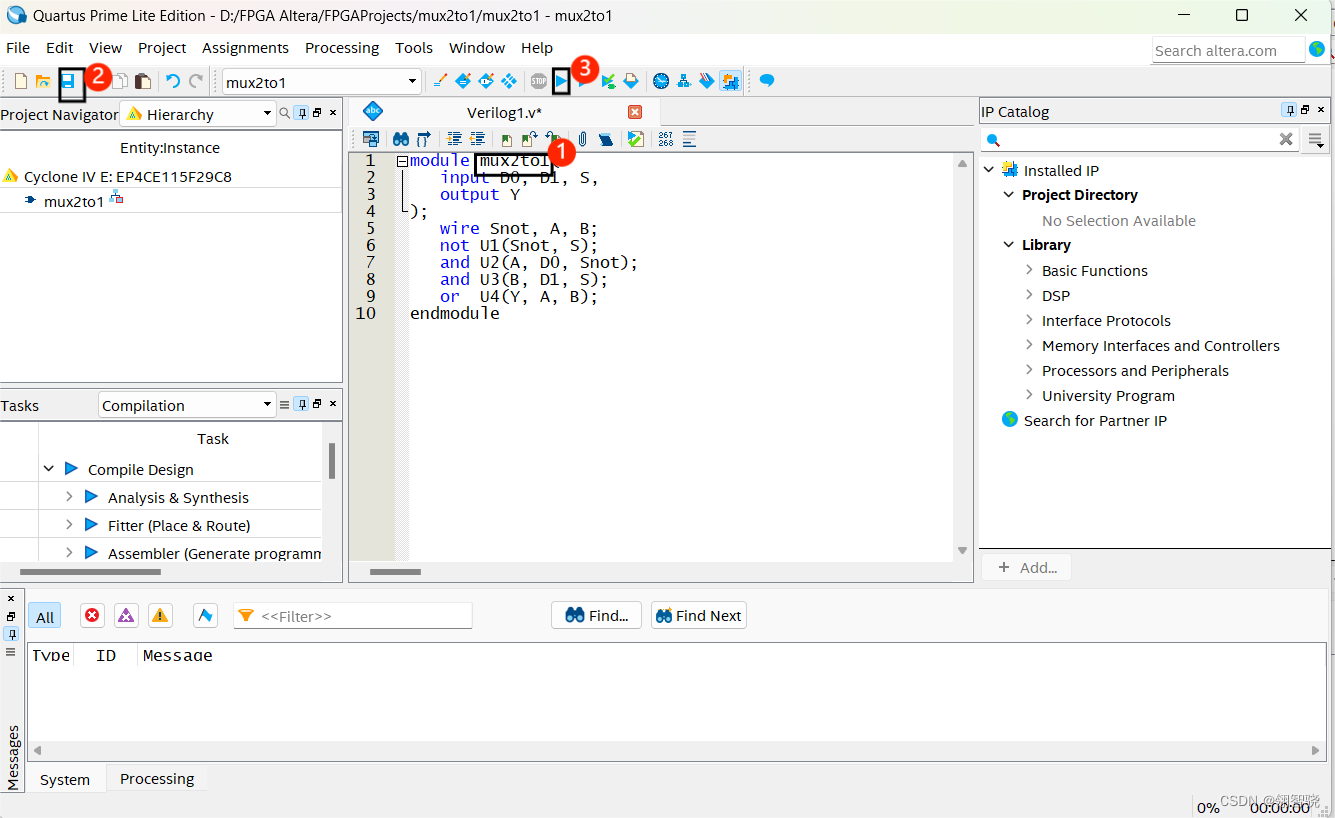

接下来在打开的文件中编写要实现的模块的代码,要注意的是,顶层模块的名字应该与你创建项目的名字相同,否则会报错,然后点击左上角保存按钮(保存地址默认即可),并按照途中③开始编译项目

代码如下

- module mux2to1(

- input D0, D1, S,

- output Y

- );

- wire Snot, A, B;

- not U1(Snot, S);

- and U2(A, D0, Snot);

- and U3(B, D1, S);

- or U4(Y, A, B);

- endmodule

编译完成后查看下方,没有error即可

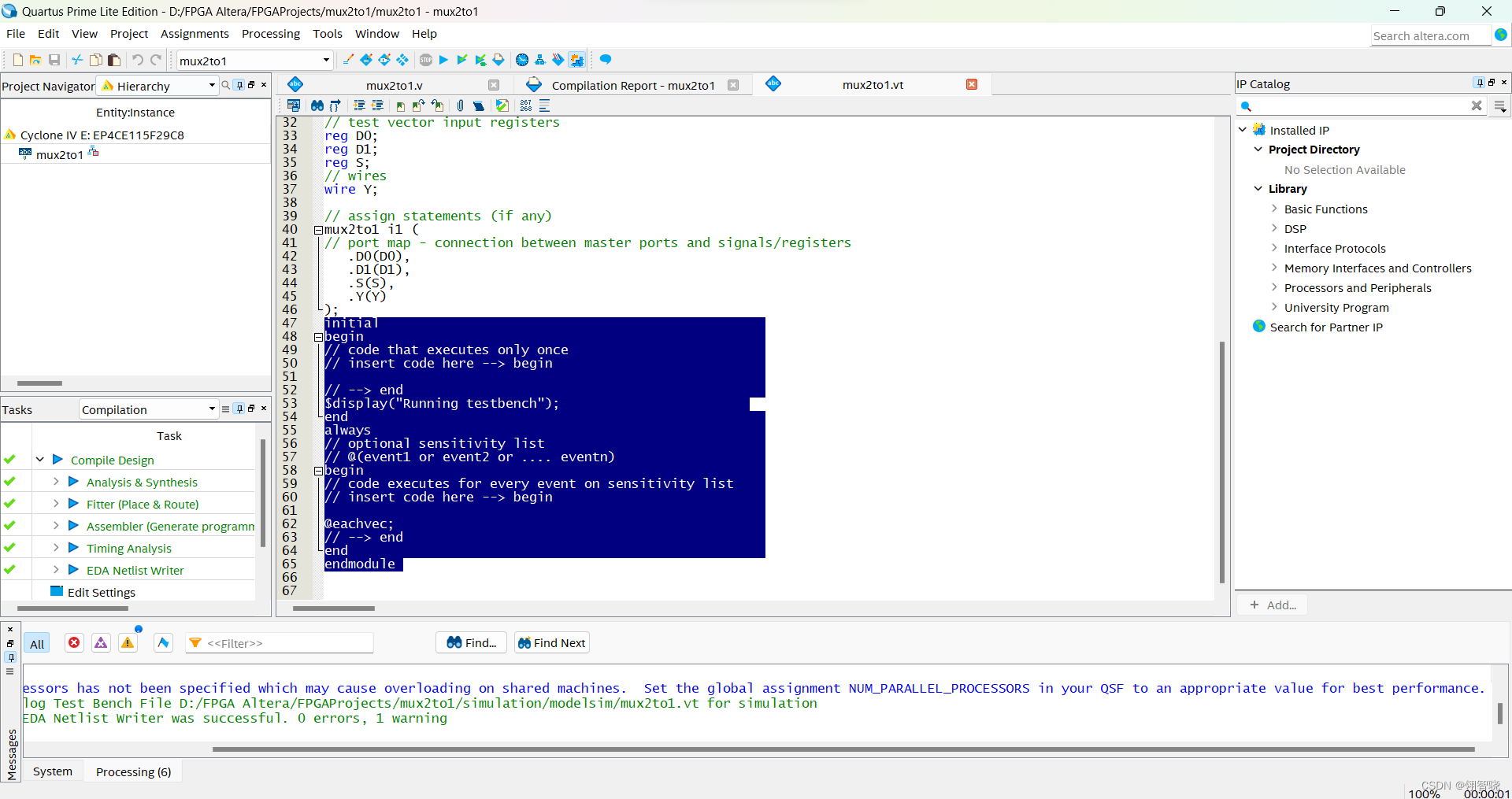

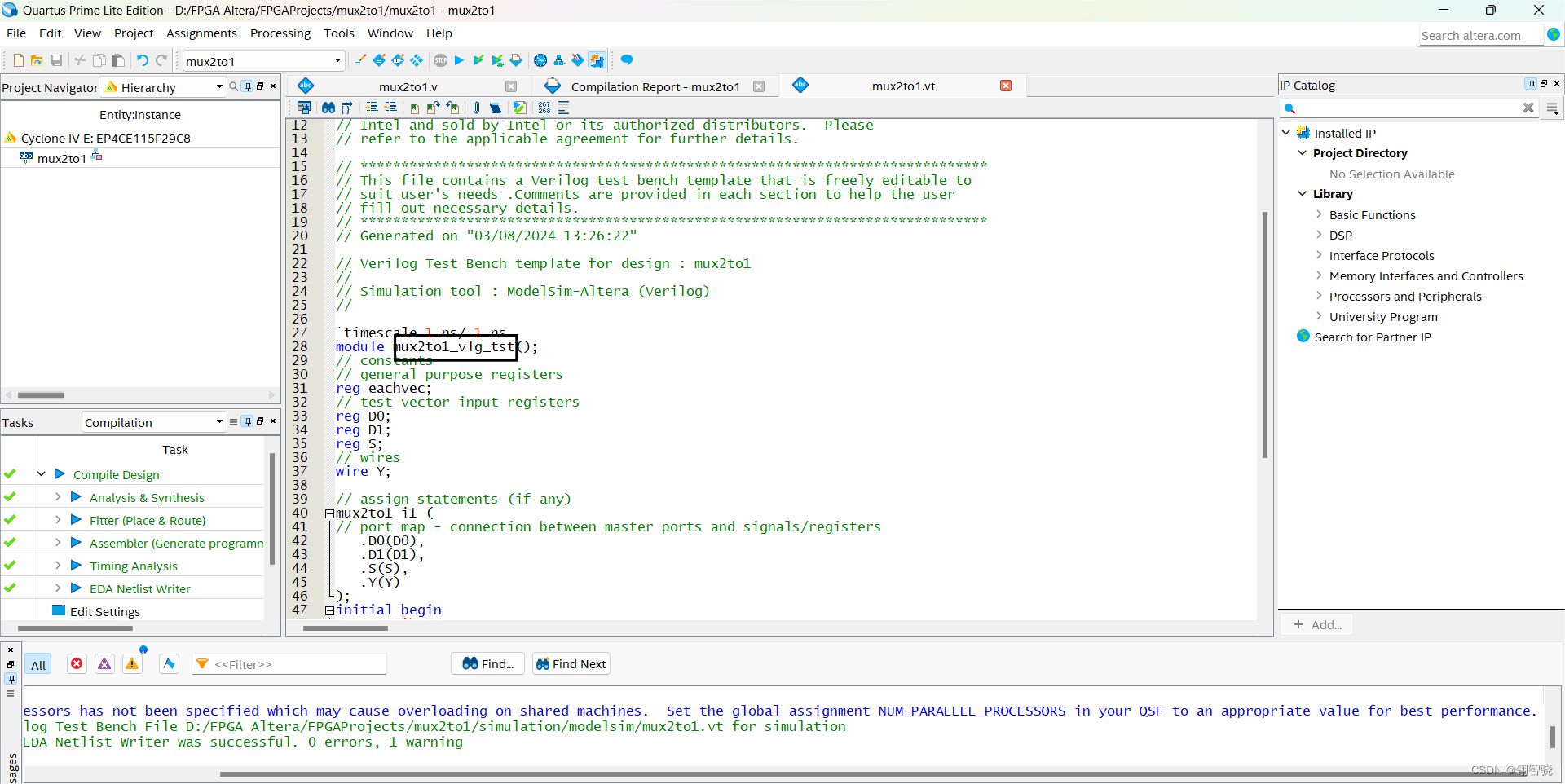

编写测试模块

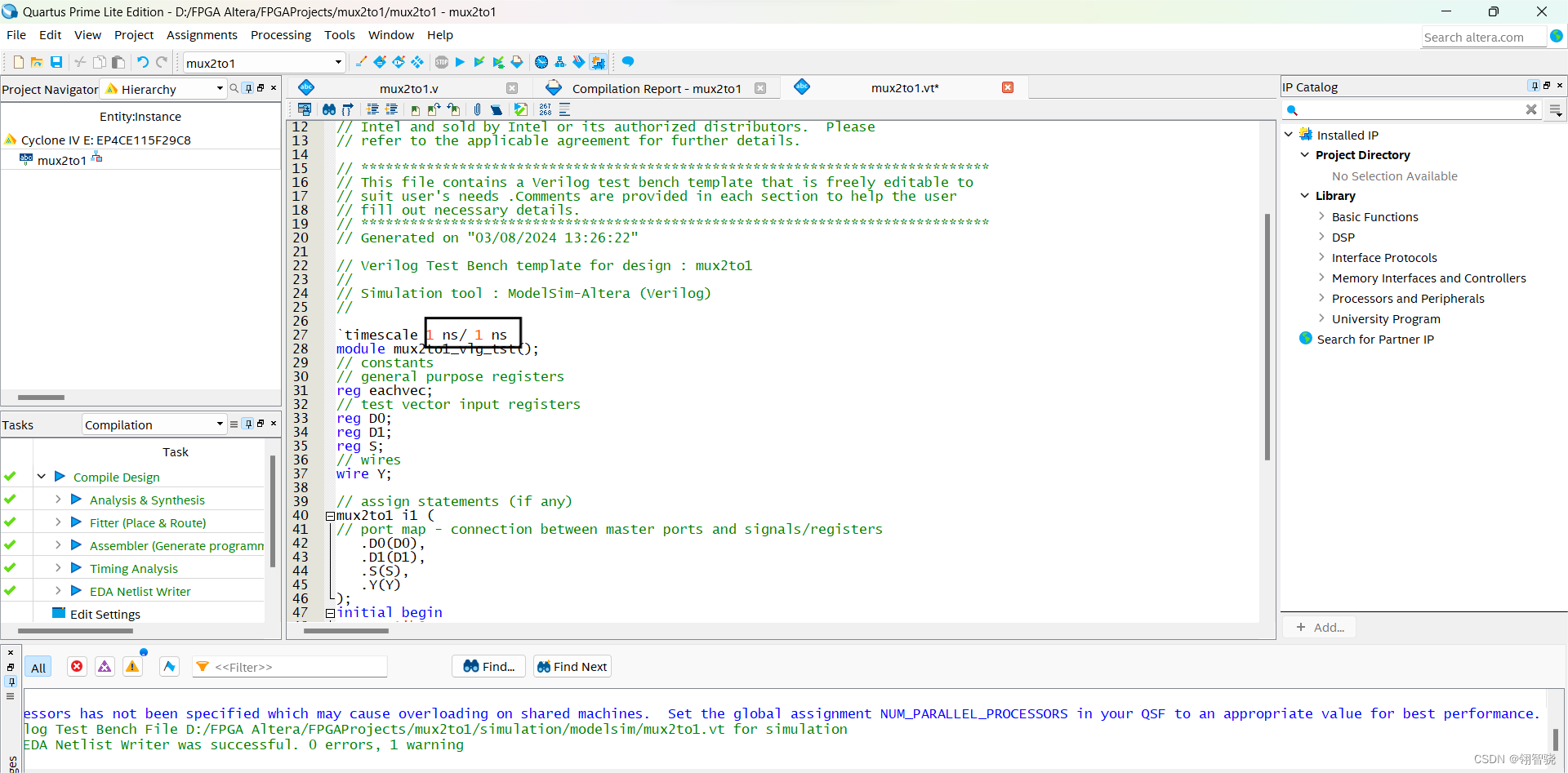

首先,在processing->start->start test bench template writter生成测试模块文件模板,他会在仿真文件夹中生成一个vt文件

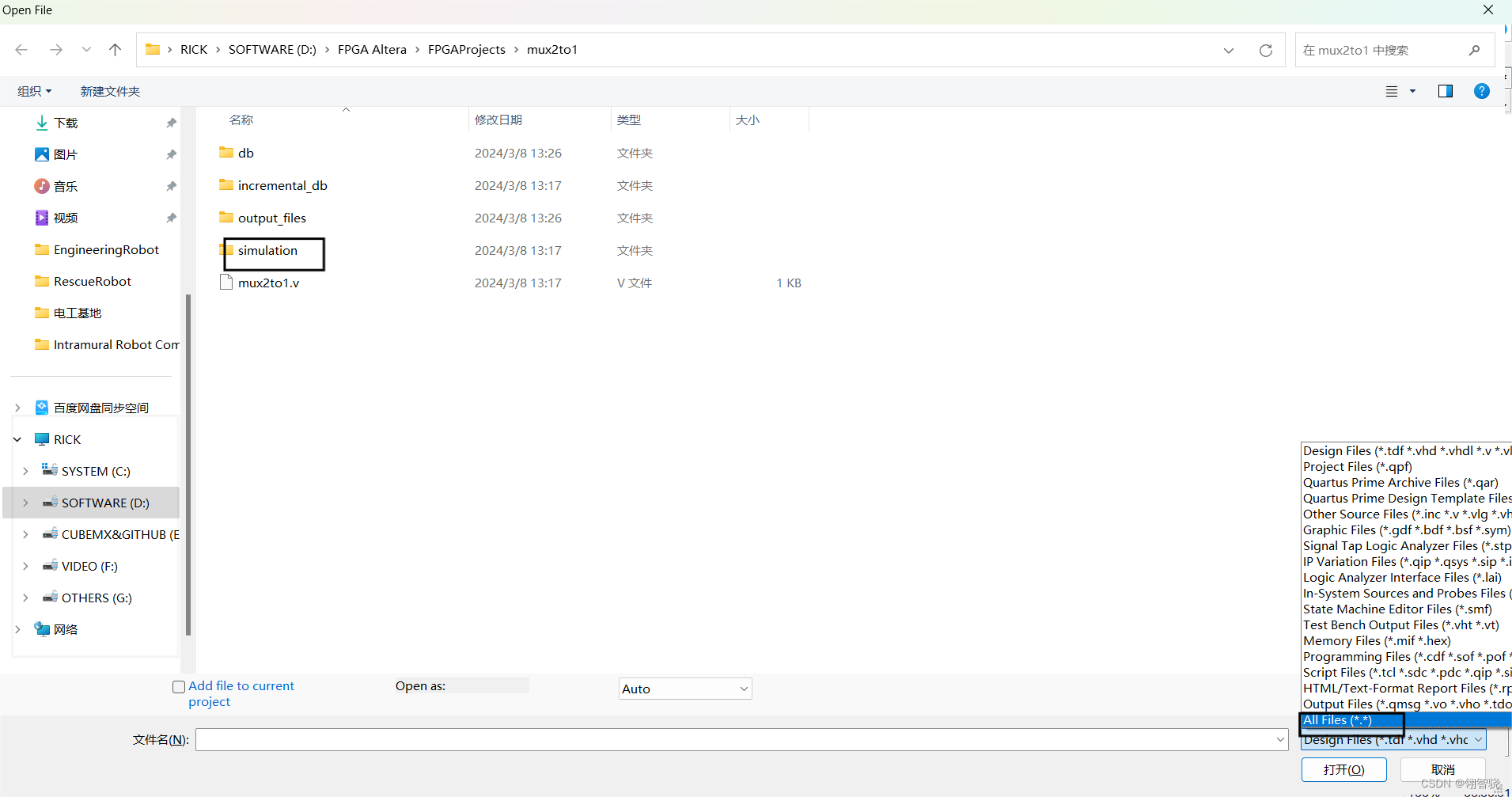

接着我们打开该测试模板进行编写,按住Ctrl+O选择文件,将文件类型改成all files,并点击simulation文件夹

找到以vt为后缀的文件打开即可

打开后首先将时间单位改成ns

然后选中以下区域,将其替换成下面代码块中的代码

- initial begin

- S = 1'b0;

- D0 = 1'b0;

- D1 = 1'b0;

- #1 D0 = 1'b1;

- #1 D0 = 1'b0;

- #1 D1 = 1'b1;

- #1 D0 = 1'b1;

- #1 S = 1'b1;

- #1 D0 = 1'b0;

- #1 D1 = 1'b0;

- #1 D0 = 1'b1;

- #1 D0 = 1'b0;

- #1 D1 = 1'b1;

- #1 D0 = 1'b1;

- end

- initial begin

- $monitor($time,":\tS=%b\tD1=%b\tD0=%b\tY=%b", S, D1, D0, Y);

- end

- endmodule

完成后点击左上角保存

找到文件中顶层模块名字并复制他

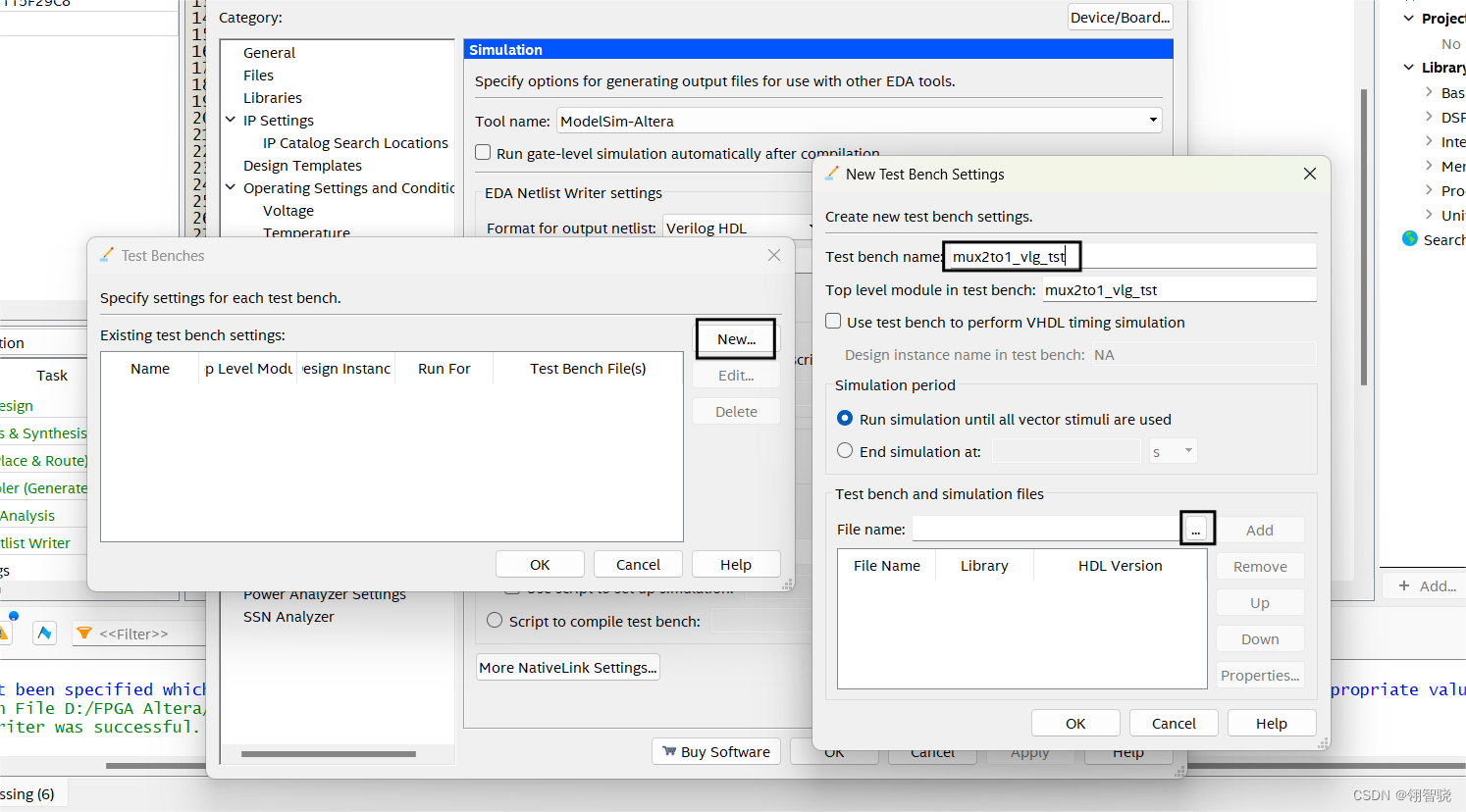

接下来按住Ctrl+shift+E打开设置,或者点击Processing->settings

点击Simulation->compile test bench

然后点击test benches进行配置

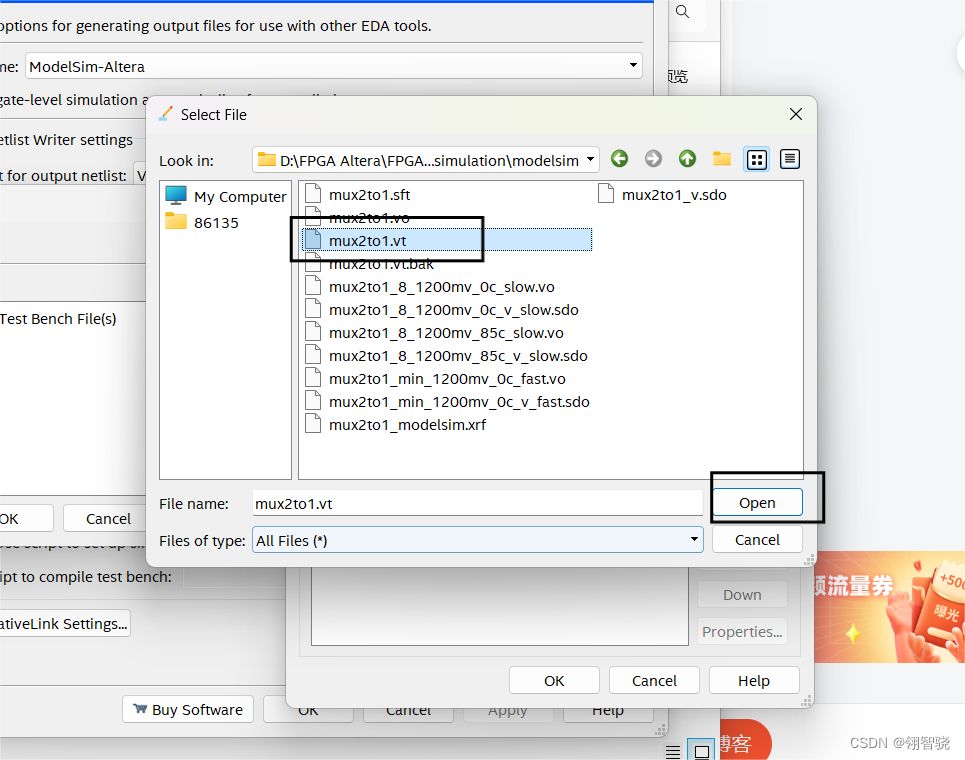

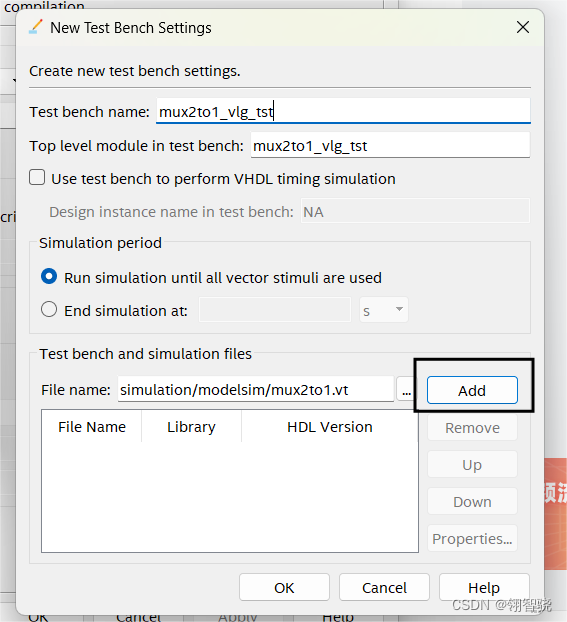

点击new添加,并把刚刚复制的顶层模块名粘贴进去,然后点击下面的...找到文件

按照之前的路径选择刚才编辑的vt文件,点击open打开

点击add进行添加后按ok确认

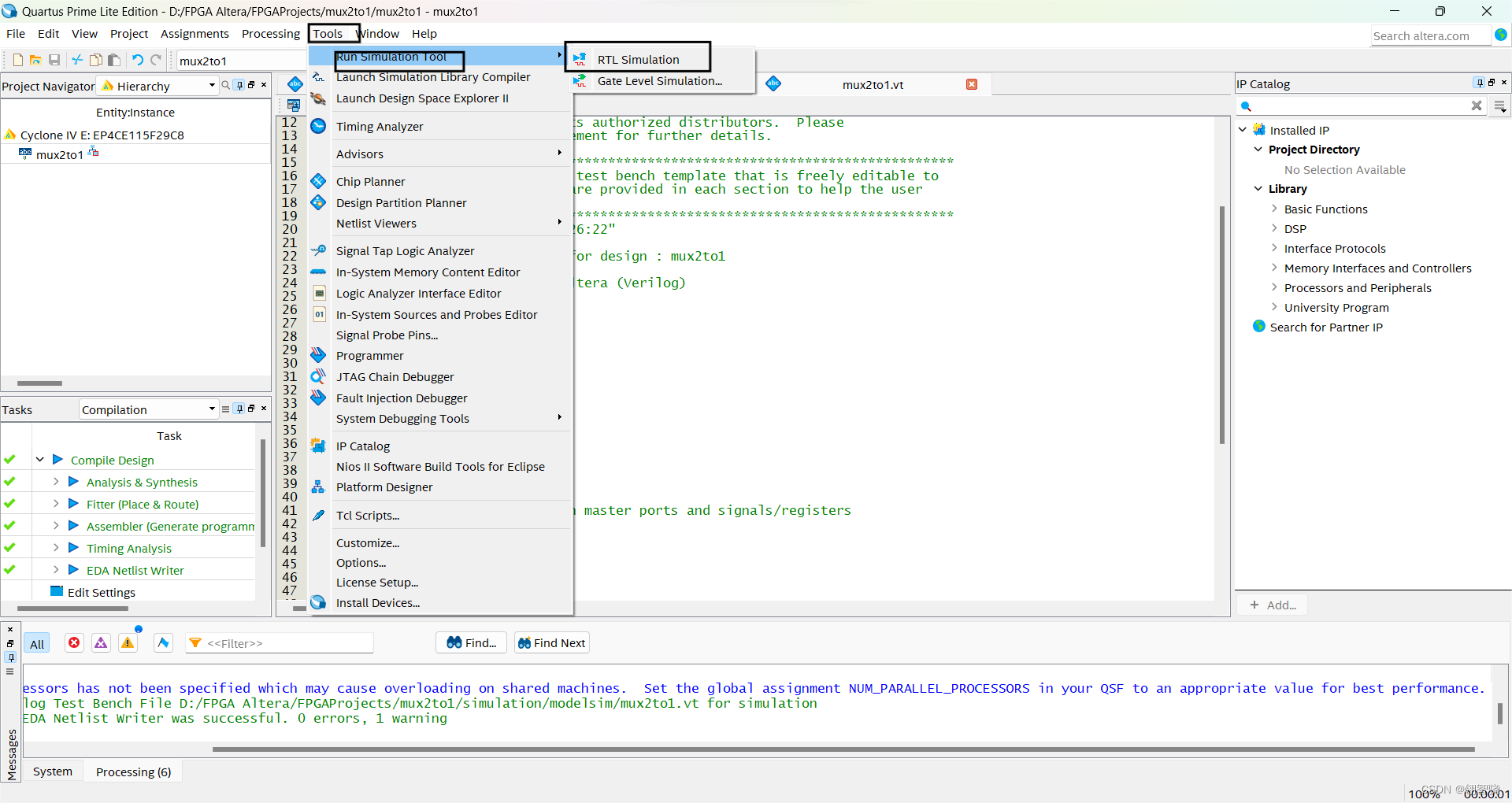

接着回到主页面,先点击三角形再编译一次,然后按照提示开始进行仿真

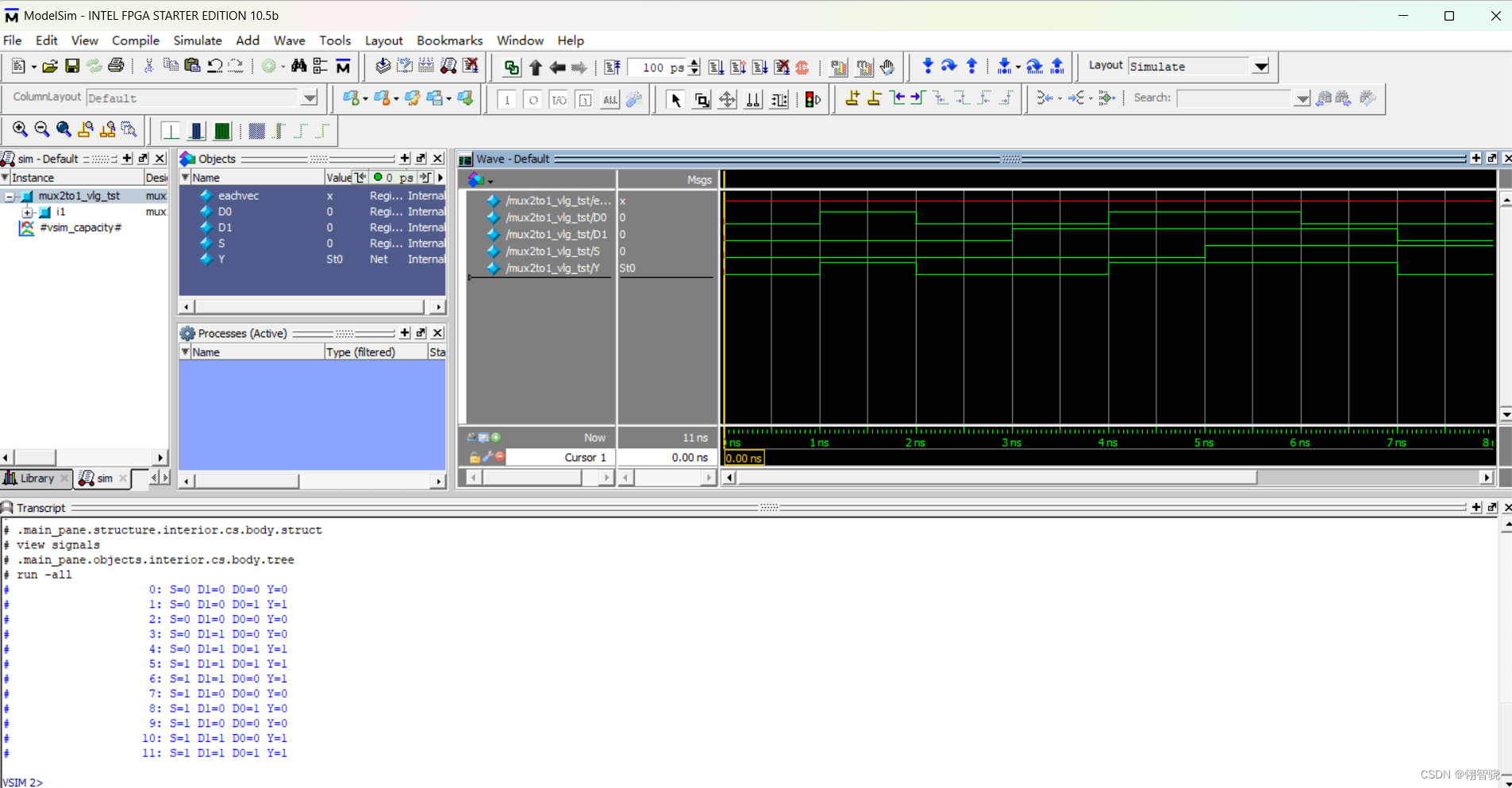

编辑器就会自动打开modelsim开始仿真并得到我们的波形

欢迎大家的讨论