热门标签

热门文章

- 1apk开发文档!面试完腾讯我才发现这些知识点竟然没掌握全,已开源_apk问价如何查看开发作者(2)

- 2Git报错解决:git@gitee.com: Permission denied (publickey)_gitee permission denied (publickey)

- 3应用层防火墙(WAF)规则设置未能有效防御针对应用的攻击_web应用防火墙无法有效保护

- 4MySQL并发控制_mysql 并发

- 520届华为勇敢星实习面试记录_华为勇敢星计划,什么时间面试

- 6MAC M2下安装Java及maven环境变量_mac m2 安装jdk

- 7【Spring Boot】掌握Spring Boot:深入解析配置文件的使用与管理_springboot如何解析properties文件的

- 8推荐项目:Tiktokenizer - 精确的OpenAI提示令牌计算器

- 9STM32调试MIPI RFFE协议_stm32 mipi

- 10Git报错解决:git@gitee.com: Permission denied (publickey)._gitee 你的访问权限受限

当前位置: article > 正文

【FPGA实验0】Quartus建立工程文件以及仿真_quartus怎么仿真

作者:羊村懒王 | 2024-06-12 11:12:47

赞

踩

quartus怎么仿真

FPGA的第一课,学习Quartus编程运行仿真烧录的这一个流程,以一个十位的计数器为例。

芯片商家:ALTERA

编程软件:Quartus II

试验箱上的芯片型号:EP4CE6E22C8N

一、新建一个工程

打开软件后会会弹出一个窗口,点击【创建向导】

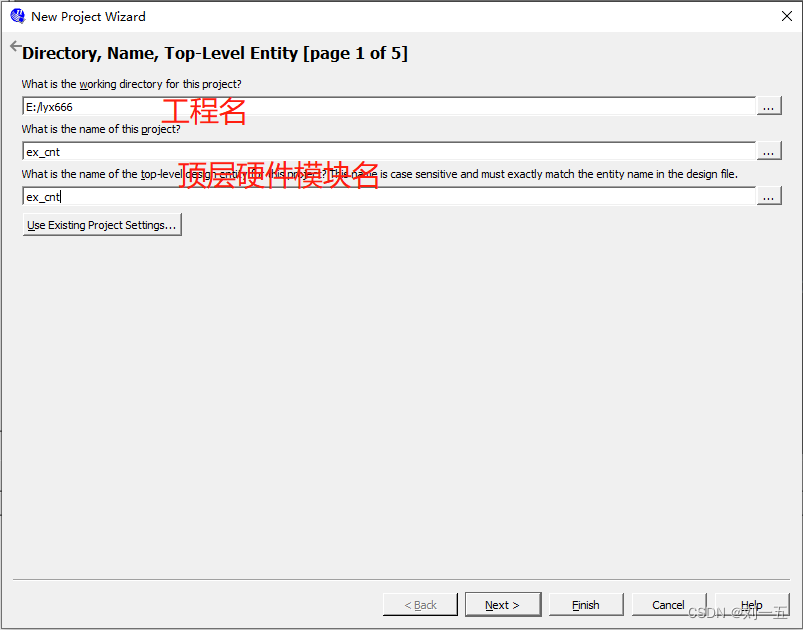

第一步:设置工程名和顶层硬件模块名

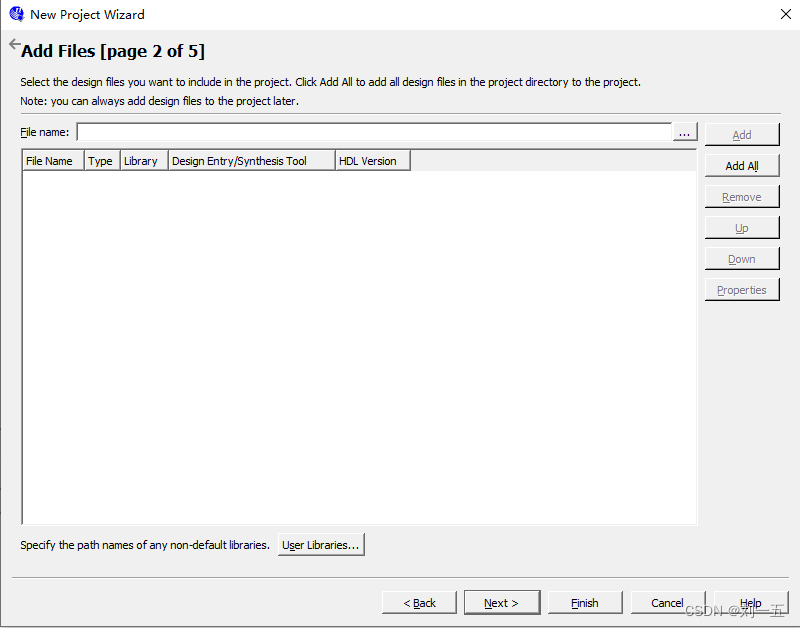

第二步:加入原先写好的文件,如若没有就直接点击下面的【next】即可

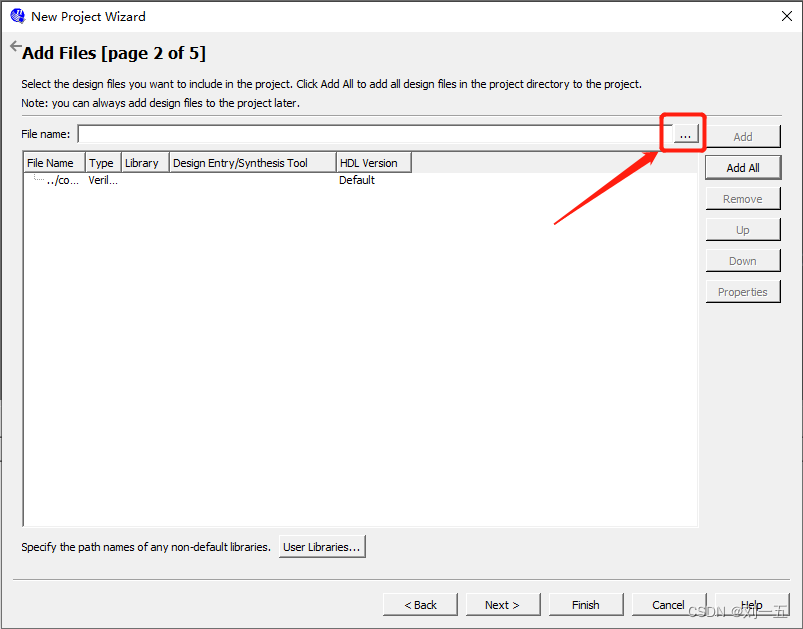

若要添加文件,则点击这个按钮

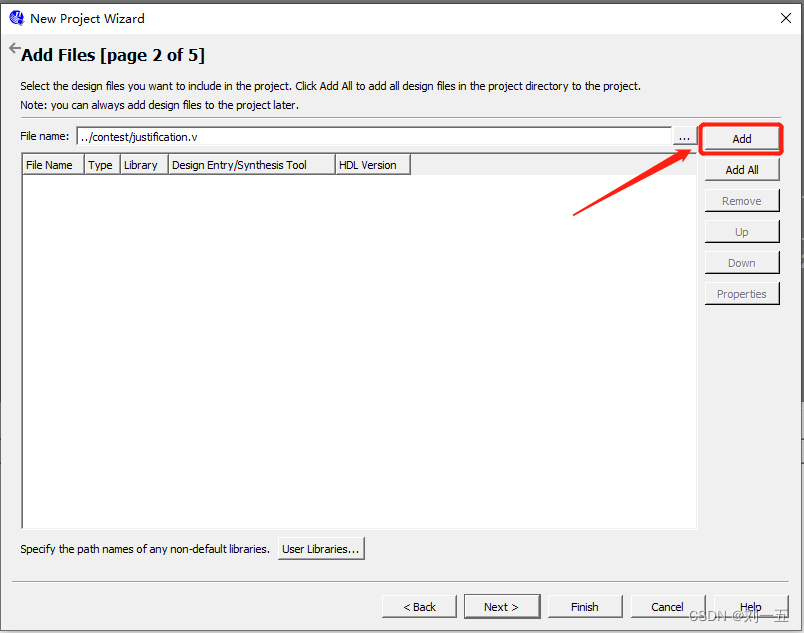

然后要记得点击【Add】不然添加进去的是一个只有文件名的空文件

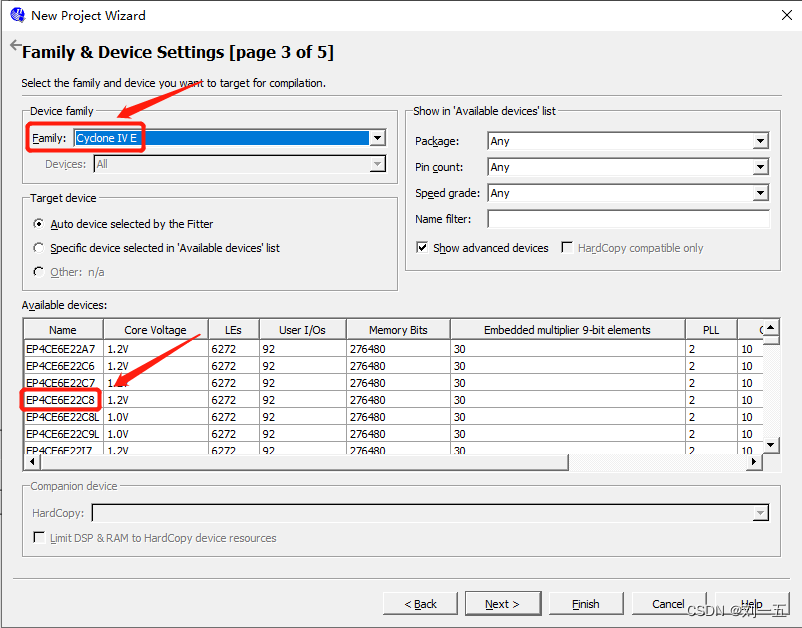

第三步:根据试验箱上芯片的型号我选择【Cydone IV E】系列,设备型号【EP4CE6E22C8】。

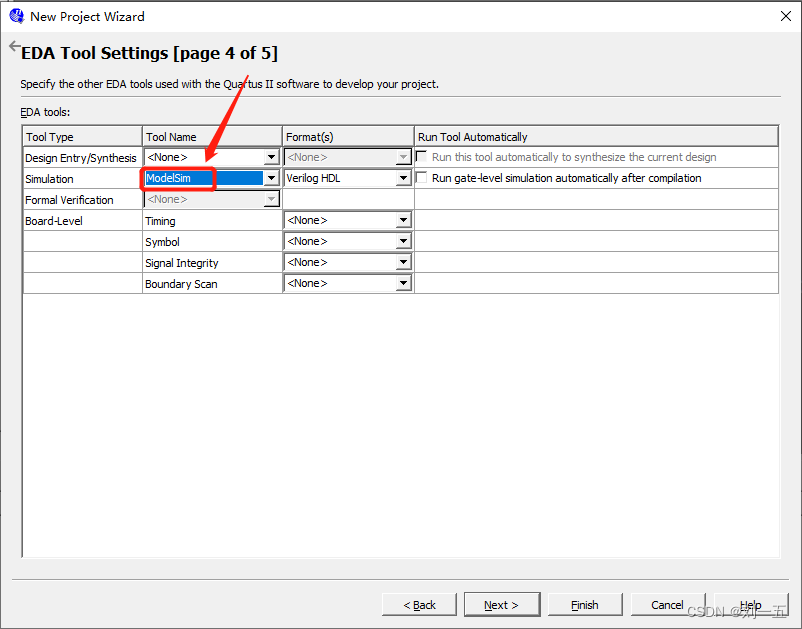

第四步:选择仿真模式为【ModelSim】

第五步:列出来刚刚的选择,确认无误后,点击【Finish】

到此,就完成了工程的新建。

二、编写程序

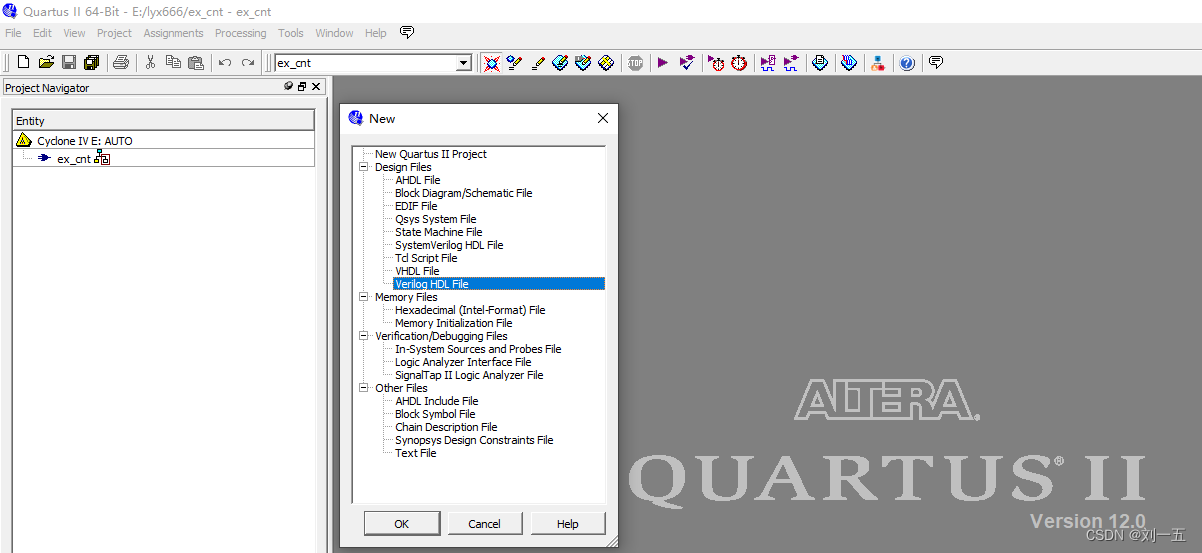

1、新建一个【Verilog HDL File】文件

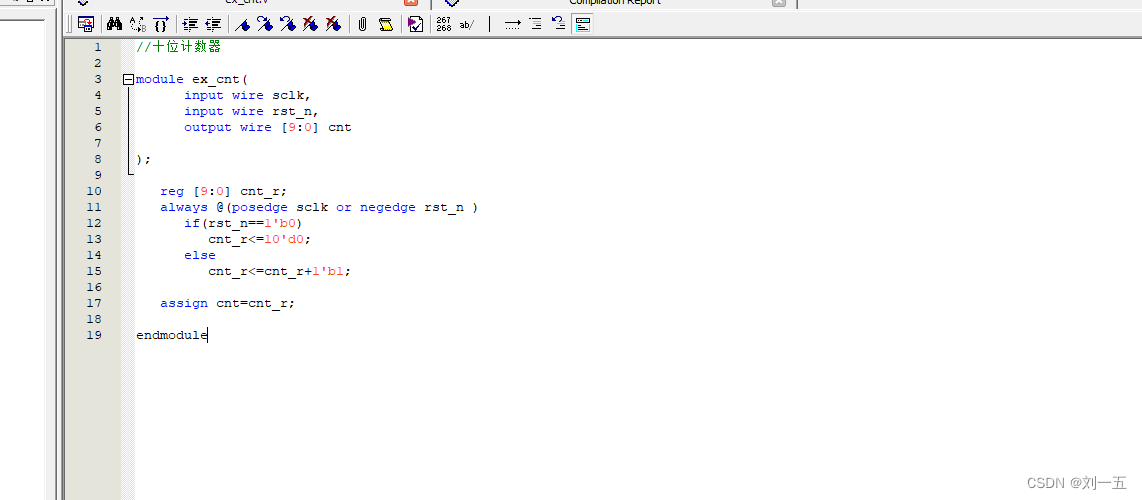

然后就开始码代码,以一个十位的计数器为例

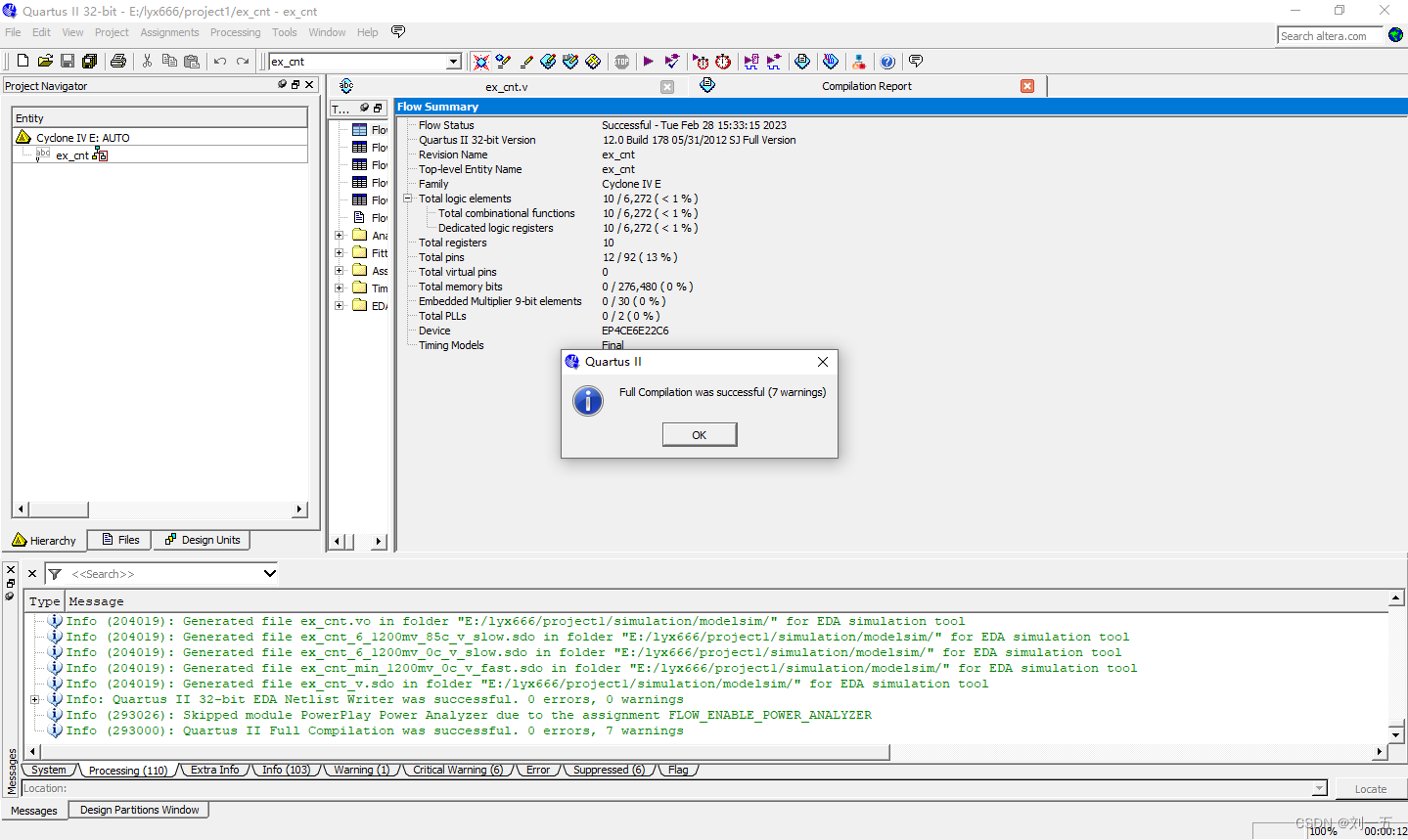

三、编译

点击菜单栏中的三角形进行编译

若编译无误则会弹出如下提示:

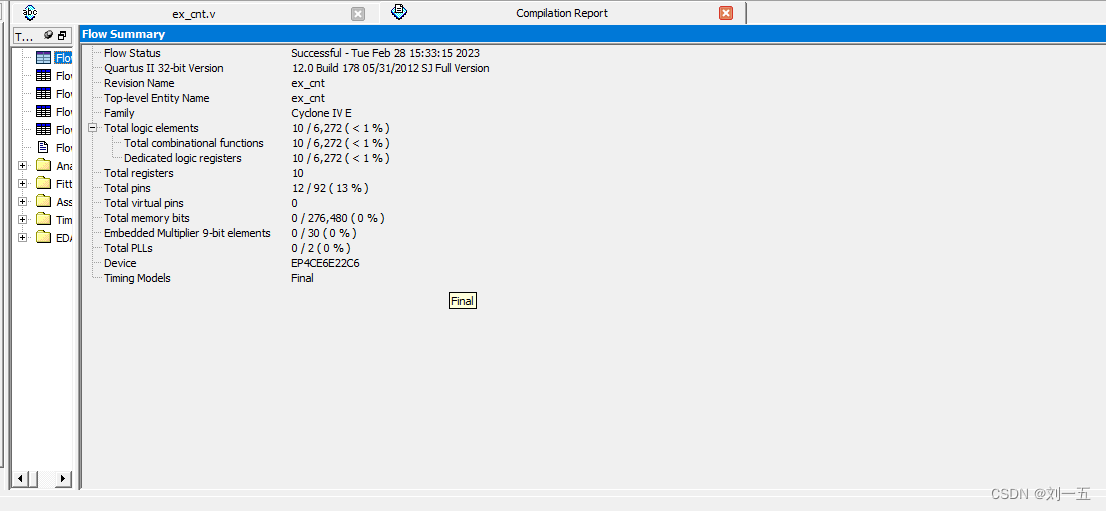

1、可以查看所用到的资源:

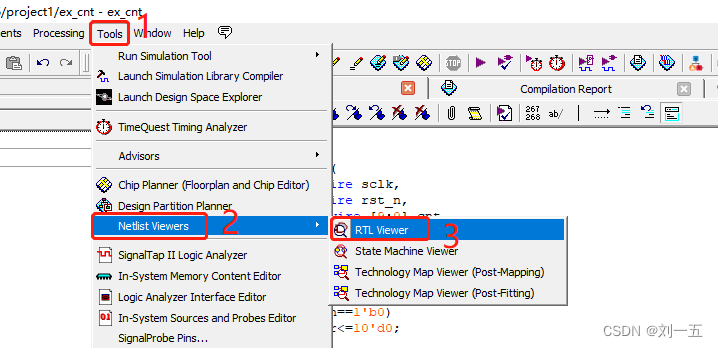

2、如何看生成的电路

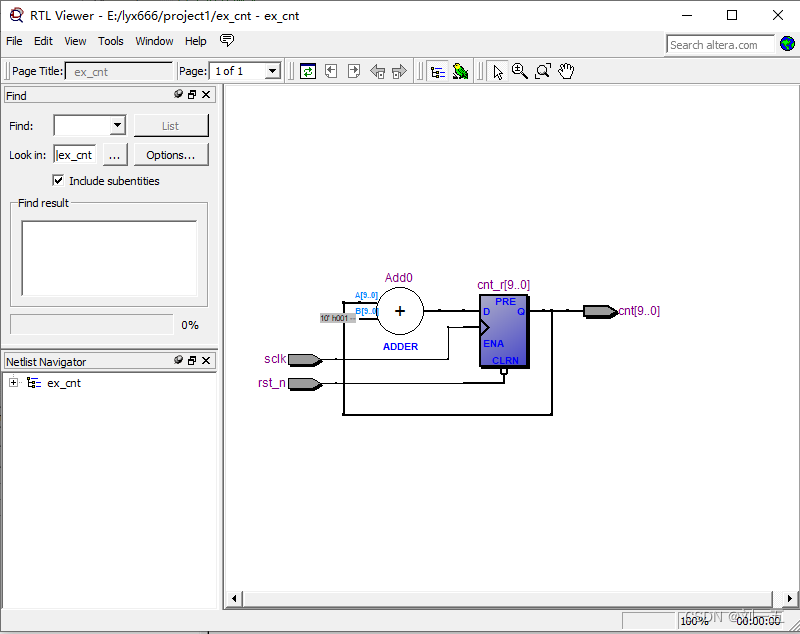

可以看到新建的电路如下:

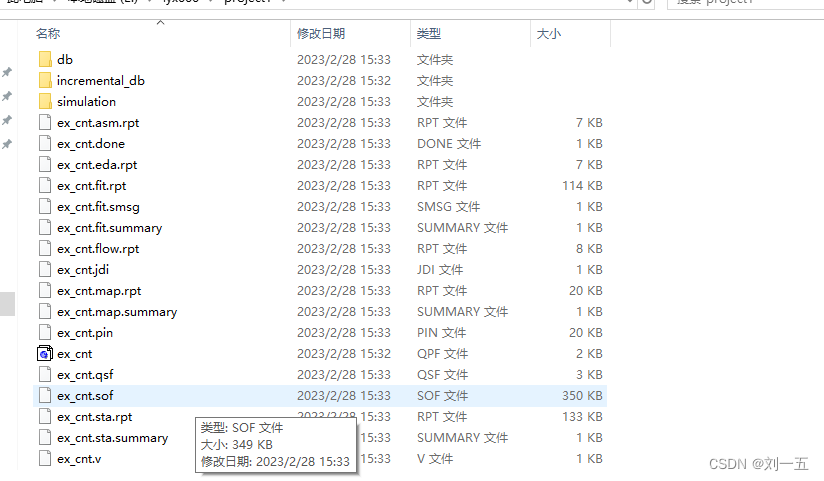

3、打开文件夹,可以看到需要烧录的文件

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/羊村懒王/article/detail/707830

推荐阅读

相关标签