- 1Win11安卓子系统怎么安装?_127.0.0.1:58526

- 2【Linux】文件描述符与重定向操作_将存放用户信息文件中的后5行通过重定向符号 导入到file02.txt中

- 3新概念英语(第二册)复习——Lesson 1 - Lesson5

- 4Jenkins配置远程服务器SSH Server流程_jenkins ssh server

- 5SpringBoot3整合Mybatis-plus报错IllegalArgumentException

- 6【深度学习笔记】6_5 RNN的pytorch实现

- 72023阿里最新发布Java后端面试八股文PDF合集,共计1700页_java面试八股文pdf 下载

- 8Flutter 成功在鸿蒙上运行;微信 8.0 发布;支付宝和微信支付达到反垄断标准 | 极客头条...

- 9linux----------2--3----(无名)管道通信原理及管道编程实战_无名管道为什么有两个文件按描述符

- 10在cmd命令行下使用VS Build Tools 编译运行C/C++源文件_vs_buildtools

折叠式共源共栅运算放大器_折叠式共源共栅运算放大器设计

赞

踩

绪论

研究工作的背景与意义

运算放大器(Operational Amplifier),简称运放(Op Amps),它最早是在1947 年由John R.Ragazzini 命名的,代表一种特殊类型的放大器,经由恰当选取的外部元件。它能够执行各种运算,诸如放大、加、减、微分和积分运算,从而能够在电路中实现各种功能:从直流偏置的产生到高速放大或是滤波。因此,运算放大器是许多模拟系统和混合信号系统中的一个重要组成部分。 随着集成电路技术的不断发展,高性能运算放大器得到广泛应用,成为模拟集成电路和混合信号集成电路设计的核心单元电路,并已被运用到各种电子系统之中,其性能直接影响电路及系统的整体性能。折叠式共源共栅运算放大器具有诸多优良特性,因此设计一个有实用价值的折叠式共源共栅运算放大器是非常有现实意义的。

国内外现状分析

集成电路产业是全球高新技术产业的前沿与核心,也是最具活力和挑战性的战略产业之一。纵观国际集成电路领域,最早的第一代集成运算放大器,基本上是按分立元件电路的思想制造的。它的特点是大部分采用 NPN 管,只有少量是 PNP管,但只能满足比较低的性能。之后的第二代集成运算放大器以采用有源负载为标志。到了第三代集成运算放大器,以晶体管作为差分输入级为特点,其值可高达 1000-5000,因此在相同的电路集成条件下,输入偏置电流比普通 NPN 管电流低一个数量级以上,输入电阻较高,电压放大倍数可达到 107 左右。而第四代集成运算放大器,则采用了中、大规模的集成电路技术,其质量性能指标己接近理想集成运放。在集成电路领域,每一年都有很多新型的、功能越来越高的运算放大器不断进入电子应用领域。最新一代运算放大器的带宽可从 5KHz 到几 GHz 不等;其工作电源可以从零点几伏到几百伏;输入失调电压和失调电流也正在变得越来越小。

而在国内集成电路领域,由于科研、生产、技术等各方面的条件,运算放大器的技术发展相对较缓慢,在很多方面仍与国际上有一定差距。特别是 CMOS 工艺的运算放大器,基本上还处于研发、试制和小型生产的阶段,其电路性能指标相对较低,因此停留在小规模而并没有批量生产和投放市场。对于各行业来说,这种现状已经远远不能满足国内应用电子领域高速发展和不断增长的需求。近几年,国家不断加大电子方面的科研投入,国内一些高等院校也在与科研单位共同开展集成运算放大器的设计与研究,不断寻求新的技术突破。

同时,国外的各大集成电路设计与制造公司也在高性能 CMOS 运算放大器的研究方面一直不断进行发展。这些公司不断研究新型的电路结构设计,对特殊参数要求和特殊功能的新产品不断面市,在一些特定领域的高性能运放也能很快地设计与生产,力争实现更加丰富和具备经济效益的功能。从这些研究和投入中可以看出,无论国家、科研机构还是企业,都对集成运算放大器的研究和开发十分重视。同时,运算放大器是模拟集成电路的基本模块,对于其它功能电路(如 PLL, A/D 与 D/A,开关电容)的研发有积极的技术支撑作用,这也是国外各大集成电路设计与制造单位重视运放研究的原因之一。 如美国的 ADI, TI 等集成电路公司皆有型号多样的各种 CMOS 运算放大器在不断的进军电子市场。

总体来看,运算放大器的发展目标和方向也在不断变化着,为了满足更高的要求, 运算放大器在未来的发展方向大概可分为以下几种方向:

- 双极型运算放大器,主要在于改进电路的输入特性;

- JFET 运算放大器,主要在改进其输入电压噪声;

- 低压低功耗运算放大器,一般是在功耗以及输入输出范围方面;

- 混合运算放大器,主要在高速、大功率和大电流缓冲中应用;

- 单片功率运算放大器,散热是其发展的主要障碍;

- 仪用放大器,它的特点是在输入失调电压、电流方面要求较苛刻;

- 介质隔离运算放大器,主要存在于在抗辐射方面的研究;

- CMOS 运算放大器,它在各方面皆有较大的优越性,近年来广泛运用于集成电路 设计、制造工艺等领域。

研究目标、研究内容与技术指标

研究目标

运算放大器(简称运放)是模拟电路的一个最通用的单元。所谓全差分运放是指输入和输出都是差分信号的运放,它与普通的单端输出运放相比有以下几个优点:更低的噪声;较大的输出电压摆幅;共模噪声得到较好抑制;较好地抑制谐波失真的偶数阶项等[1]。所以高性能的运放多采用全差分形式。近年来,全差分运放更高的单位增益带宽频率及更大的输出摆幅使得它在高速和低压电路的应用有更多的吸引力。随着日益增加的数据转换率,许多应用需要高速的模/数转换器(ADCs),而高速ADCs需要高增益和高单位增益带宽运放来满足其系统精度和快速建立的需速度和精度是模拟电路两个最重要的性能指标,然而,对电路这两方面的优化会导致相互矛盾的结果。所以同时满足这两方面的要求是困难的。折叠式共源共栅技术可以较成功地解决这一难题[2],这种结构的运放具有较高的开环增益及很高的单位增益带宽。

研究内容

论文首先介绍了国内外运算放大器的发展历史和现状。对已有的一些运算放大器电路结构展开了研究,讨论了其中放大电路及电流镜等基本模块的结构及数学模型,并在此基础上选择了折叠式共源共栅运算放大电路及共源共栅电流镜的电路结构进行放大器设计。根据各指标的要求,放大电路中各元件的参数及偏置条件,并以此为参考确定电流镜结构中各元件的参数。该电路结构预计将得到较大的低频增益和单位增益带宽,适当的相位裕度以及较小的建立时间。

关键技术

- 共源共栅技术

- 共源共栅结构相对于传统的共源放大器提高了输出电阻ro,进而实现了运放增益gm ro的增大。

- 折叠共源共栅技术

- 相较于传统的套筒式共源共栅结构,折叠式的共源共栅结构拥有更大的输入输出摆幅,并且可以用作单位缓冲器,具备更为广泛的应用。

技术指标

工作电压范围:3.3V±10%

运算放大器开环直流增益:Gain≥80dB

增益带宽:GBW≥100 Mhz

建立时间:<50 ns

负载电容:CL=4.5pF

相位裕度:PM≥45°

电路结构理论

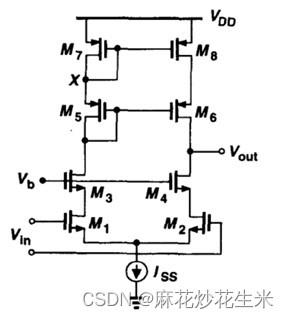

套筒式共源共栅运算放大器

套筒式运算放大器

图中给出了单端输出差动输入的套筒式运算放大器的电路结构。跟普通运算放大器相比较,可以发现套筒式结构在简单运放的基础上将单个 CMOS 管替换为共源共栅结构后得到[3]。根据图中运算放大器可以算出低频小信号增益:

Av=gm1gm3+gmb3ro1ro3gm5+gmb5ro5ro7

但是这是以减少输入范围和输出摆幅为代价。在如图所示的全差分电路中,其输出摆幅为:

2[VDD-(Vod1+Vod3+Vod5+Vod7+VSS)]

其中,VDD为电源电压,VSS为电流源两端电压,Vod为管子的过驱动电压。为使得输入管M1工作在饱和区,输入电压Vin1需要满足以下条件:

VDD-Vod3+Vod5+Vod7+Vth1≥Vin1 ≥VSS+Vth1

可以发现,当尾电流过大或者 MOS 管尺寸较小时,输入电压的范围也较小。

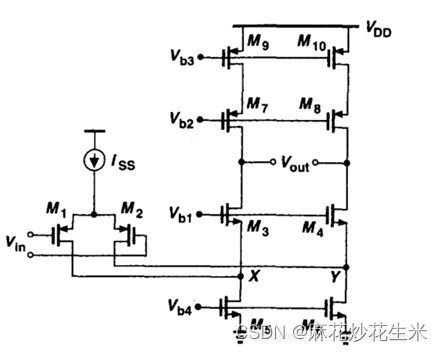

折叠式共源共栅运算放大器

为了缓解套筒式结构对输入电压范围的限制,提出了折叠式运算放大器,如图所示即为折叠式共源共栅运算放大器。

折叠式共源共栅放大器

和套筒式结构相比,该结构中输入管用相反型号的 MOS 管代替。因为在结构上的不层叠共源共栅管,因此输入电压范围增大为:

VDD-VSS-Vth ≥Vin1 ≥Vod-Vth

对比两个输入范围表达式可知,图中的折叠式共源共栅运算放大器的输入电压范围比对应套筒式输入电压范围大两个过驱动电压。

虽然折叠式结构比套筒式结构有更大的输入共模电平范围,但是这是以减少增益和带宽,增加功耗和噪声实现的[4]。对于图中给出的折叠式运算放大器,其低频小信号增益为:

Av=gm1gm3+gmb3ro3(ro5ro1 )gm7+gmb7ro9ro7

对比两个增益可以发现,造成折叠式运放增益减少的主要原因是加入的折叠管,使得共源共栅结构中的共源管和差分输入的 MOS 管并联,从而减少了从输入端看到的等效阻抗。

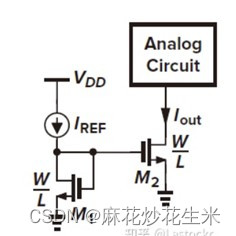

电流镜

电流镜基本结构

图中给出了基本电流镜的结构图,当给定一个确定的Vgs会产生一个确定的Id,相反一个确定的Id也会产生一个确定的Vgs。利用这个原理可以使用参考电流通过M1,同时将M1,M2的栅连接,使得M2支路获得相应的电流。根据电流公式:

Id=12μCoxWL(Vgs-Vth)2

由公式知当工艺参数相同时,IREF和Iout的电流值仅仅是两个管子的宽长比数值,当我们想得到目的电流只需改变管子的宽长比即可。

M=IoutIREF=W2L2W1L1

但是这些都只是理论的情况,实际设计中会存在阈值电压不匹配,宽长比不匹配,沟道长度调制效应等带来的非理想因素,使得电流的拷贝不是那么的精确。

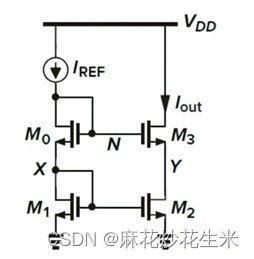

共源共栅电流镜

为了更好的体现沟道长度调制效应,将电流公式表现为:

Id=12μCoxWLVgs-Vth2(1+γVds)

通过该式子可以清楚的看到来自沟道调制效应的影响,为了增加输出阻抗,减少沟道长度调制效应,并且为折叠式共源共栅放大器提供一个自偏置直流工作点[5],选择共源共栅电流镜。

共源共栅电流镜

可以通过分析知道该电流镜输出阻抗增加了Av倍,使得其电流特性更加接近理想电流源。但是相应的该电路和 cascode 电路一样牺牲了输出摆幅。输出电压的下限变成了两个过驱动电压和一个阈值电压。

为了改善由于自偏置带来的摆幅损失,选择使用更为广泛的低压 cascode 电流镜。

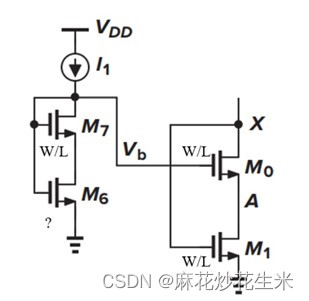

低压 cascode 电流镜

在该电流镜结构中,M0,M1,M7工作在饱和区,M6工作在线性区。为了使得电流的拷贝更加准确需要将M7的源端和M0的源端电压相等。而在调整偏置点Vb时,M0电流确定,过驱动电压确定,即改变WL即可调整直流工作点。而在电流镜的拷贝过程中,通过计算来自M6的线性区电流和饱和区电流相等,可得M7的宽长比至少是M6的三倍,而M0和M7拷贝的电流,所以M7和M0为一对电流镜,不能改变其比例[6]。

关键电路模块

折叠式共源共栅运算放大器

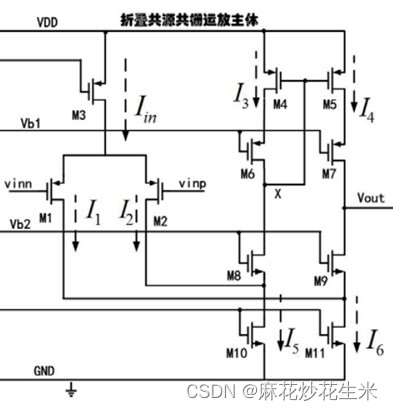

折叠共源共栅运放主体电路结构

根据电路设计指标,首先设计电路功耗。通过查阅资料当I1,I2,I3,I4电流相等时,可以避免输入大幅差分信号时 cascode 支路MOS 管偏离饱和区。所以设计得支路电路分别为

I1=I2=220μA, I3=I4=220μA, I5=500μA, I4=500μA, Iin=440μA.

通过对PMOS,NMOS 的工艺探究测得Kn = 1.15×10-4 AV2,Vth=0.742V,Kp=2.83×10-5AV2, Vth=0.742V。

考虑放大器的转换时间可得 Iin≥SR×CL即电流要大于90uA。考虑到为避免共源共栅出现0电流情况,令I5=I6≈1.1Iin。

分配好了电流,接下来确定电流的静态工作点。首先预设运放主体所有部分的MOS管过驱动电压Vds为0.3V,则可以确定偏置电压Vb1,Vb2,在确保M5,M7饱和的情况下,其输出摆幅为:

VDD-Vod5-Vod7-Vod9-Vod11

结合设计指标要求0db增益带宽为100Mhz,输入对管有

gm1=gm2=2πGBW×CL

计算得

gm1=gm2≥2.826mS

又因为gm=KpWLVod 计算得WL1> 332:1 ,取值为400:1。

根据电流公式

Id=12μCoxWL(Vgs-Vth)2

分析得到M4到M11的宽长比分别为

WL4,5=2IKpVod2≈345

同理计算得到WL3≈345, WL8,9≈345, WL6,7≈172, WL10,11≈345。

共源共栅电流镜

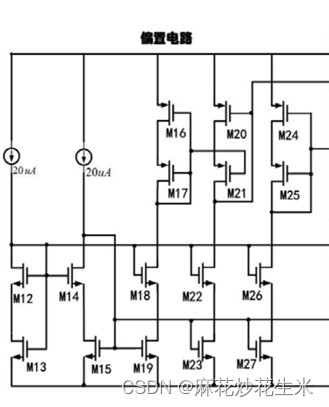

偏置电路电路结构

关于共源共栅电流镜构成的偏置电路:M12,M13,M14,M15构成低压共源共栅电流镜,偏置电流流经 M12,M13 产生偏置电压 Vb2,为 M8、M9 提供偏置电压。M18、M19、M22、M23、M26、M27 镜像 M14 的电流,提供给 M16、M17、M20、M21、M24、M25,而 M16、M17、M20、M21 构成共源共栅电流镜,为运放输入管 M3 提供电流。M24、M25 镜像的电流提供给M6、M7 ,两管的栅压为Vb1。根据电流比例计算可得:

WL3=22WL20,

WL10=WL11=24WL15,

WL15=WL19=WL23=WL27,

WL8=22WL14,

WL14=WL18=WL22=WL26.

由折叠式共源共栅模块计算得到的宽长比确定电流镜宽长比为:

WL15=17:1

低压电流镜模块为提供Vb,得到

WL12=12:1, WL13=4:1.

非理想效应

1. 沟道长度调制效应

沟道长度调制效应是指MOS晶体管中,栅下沟道预夹断后、若继续增大Vds,夹断点会略向源极方向移动,导致夹断点到源极之间的沟道长度略有减小,有效沟道电阻也就略有减小,从而使更多电子自源极漂移到夹断点,导致在耗尽区漂移电子增多,使Id增大的效应。

2. 衬底偏置效应

对于MOS-IC而言,在电路工作时,其中各个MOSFET的衬底电位是时刻变化着的,如果对器件衬底的电位不加以控制的话,那么就有可能会出现场感应结以及源-衬底结正偏的现象。一旦发生这种现象时,器件和电路即告失效。所以,对于IC中的MOSFET,需要在衬底与源区之间加上一个适当高的反向电压,即衬偏电压,以保证器件始终能够正常工作。

3. 寄生效应

理想状态下,导线的电阻、电容及电感均为零。而在实际制造时,由于导线的材料具有一定电阻率,将会产生电阻;两条平行的导线间存在电压差将会产生电容;通电的导线周围会形成磁场,电流变化时,磁场会变化,进而在附近产生电感。故而实际制造中的电路内,均会产生寄生的电阻电容及电感。在直流或者低频情况下,这种寄生效应不明显,但在交流,尤其是高频条件下,其影响将十分显著。

考虑到如上众多非理想效应,通过反复调试更改,最终确定电路内各MOS管参数如下:

电路各MOS管参数(单位:um)

| M1 | M2 | M3 | M4 | M5 | M6 | M7 |

| 480/1 | 480/1 | 1768/1 | 360/1 | 360/1 | 300/1 | 300/1 |

| M8 | M9 | M10 | M11 | M12 | M13 | M14 |

| 255/1 | 255/1 | 1200/1 | 1200/1 | 3/1 | 1/1 | 17/1 |

| M15 | M16 | M17 | M18 | M19 | M20 | M21 |

| 16/1 | 2/1 | 6/1 | 17/1 | 16/1 | 17/1 | 17/1 |

| M22 | M23 | M24 | M25 | M26 | M27 | |

| 17/1 | 16/1 | 1/1 | 3/1 | 17/1 | 16/1 |

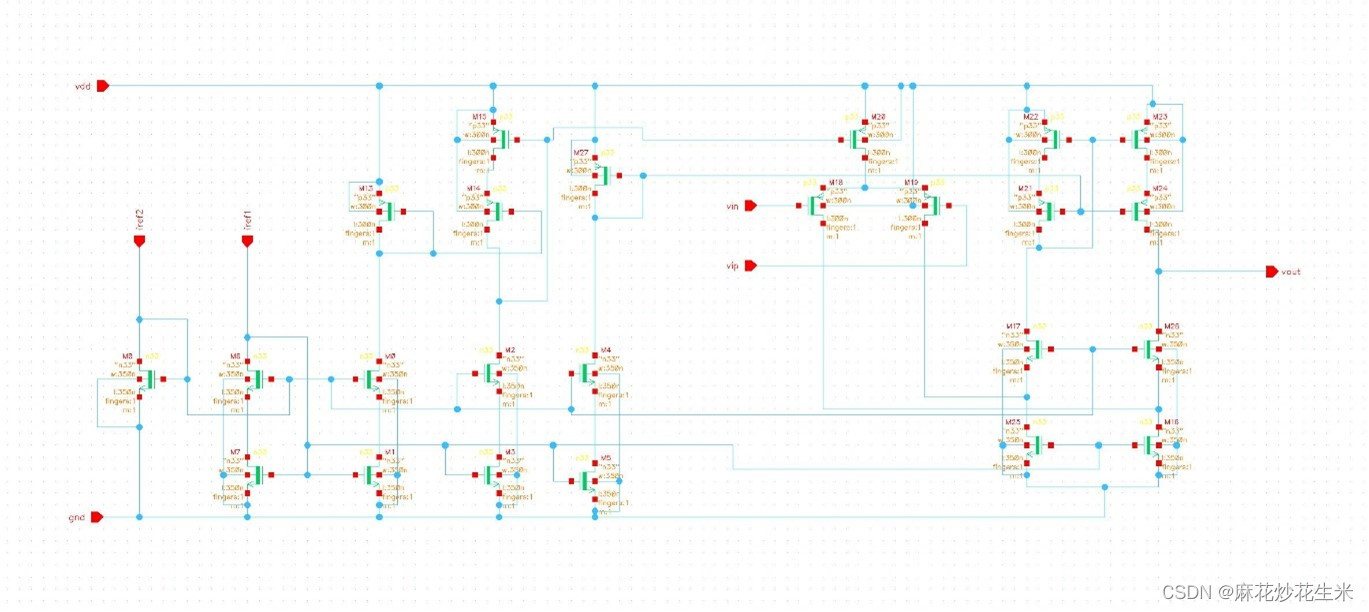

电路设计结构

结合多种电路结构,选择折叠式共源共栅运算放大器,并使用共源共栅结构的电流镜为其提供偏置电路,以达到设计要求。

电路整体结构图

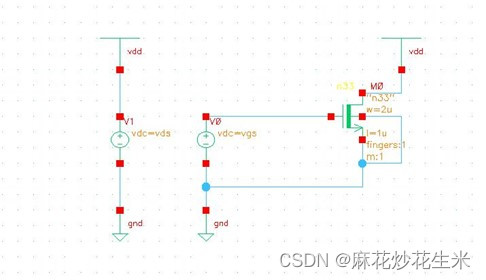

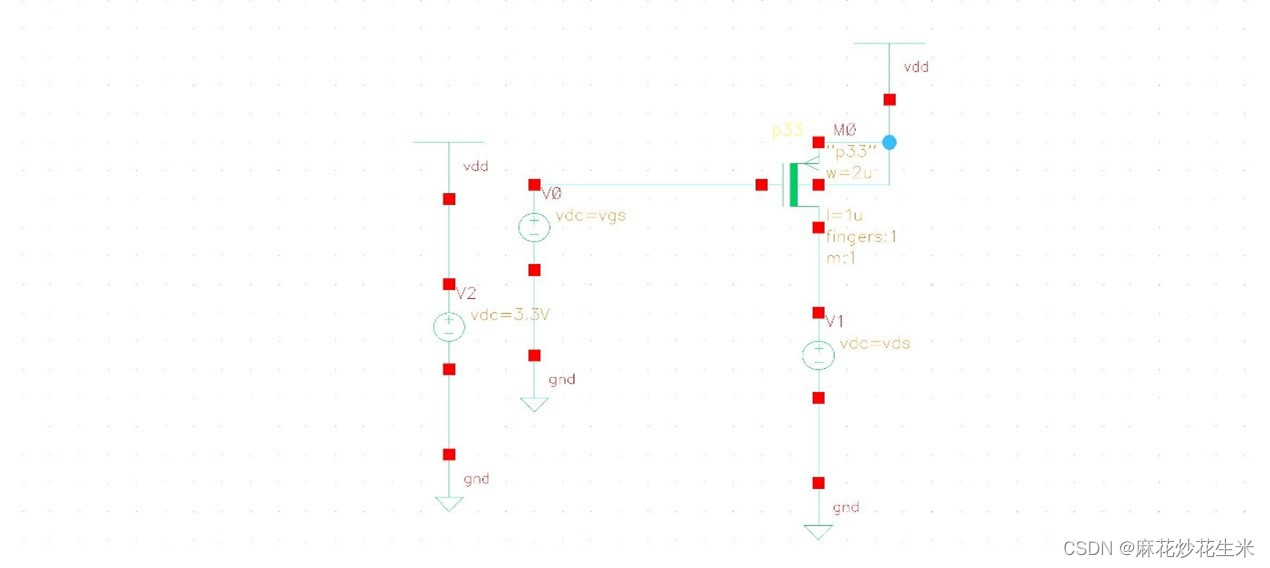

MOS管测量电路

通过对NMOS及PMOS的阈值和工艺参数测量,为接下来的宽长比计算提供帮助。

NMOS管测量电路

PMOS管测量电路

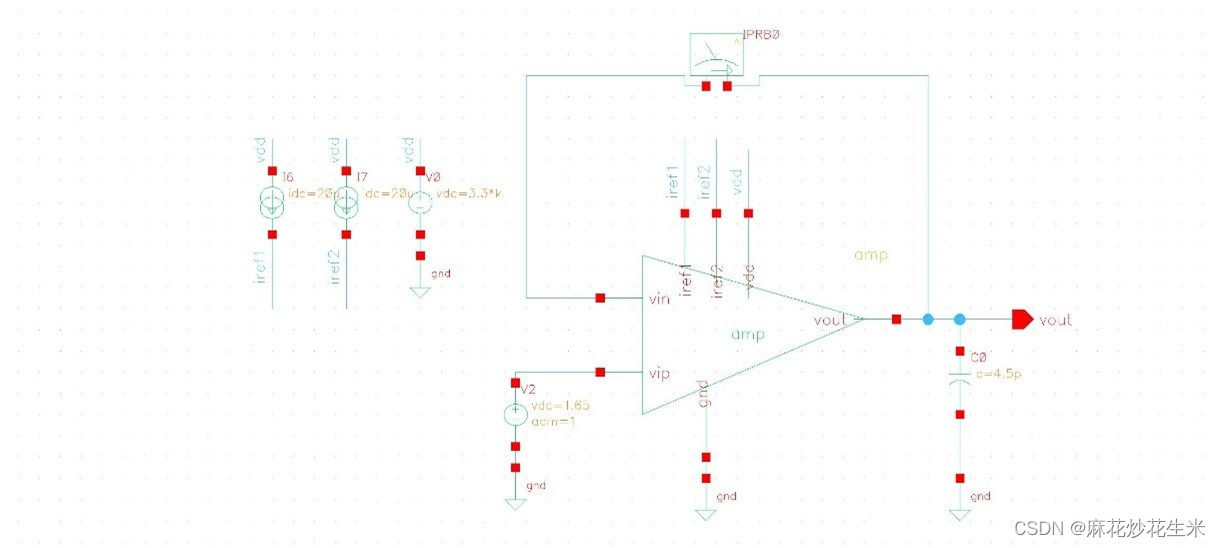

放大器开环测试电路

搭建开环测试电路测量折叠式共源共栅放大器的开环参数。

包括增益,带宽,相位裕度:

放大器开环测试电路

通过stb仿真即可了解环路的特征,同时在电源电压设置系数k,用来对电压波动进行仿真,验证电路的可靠性。

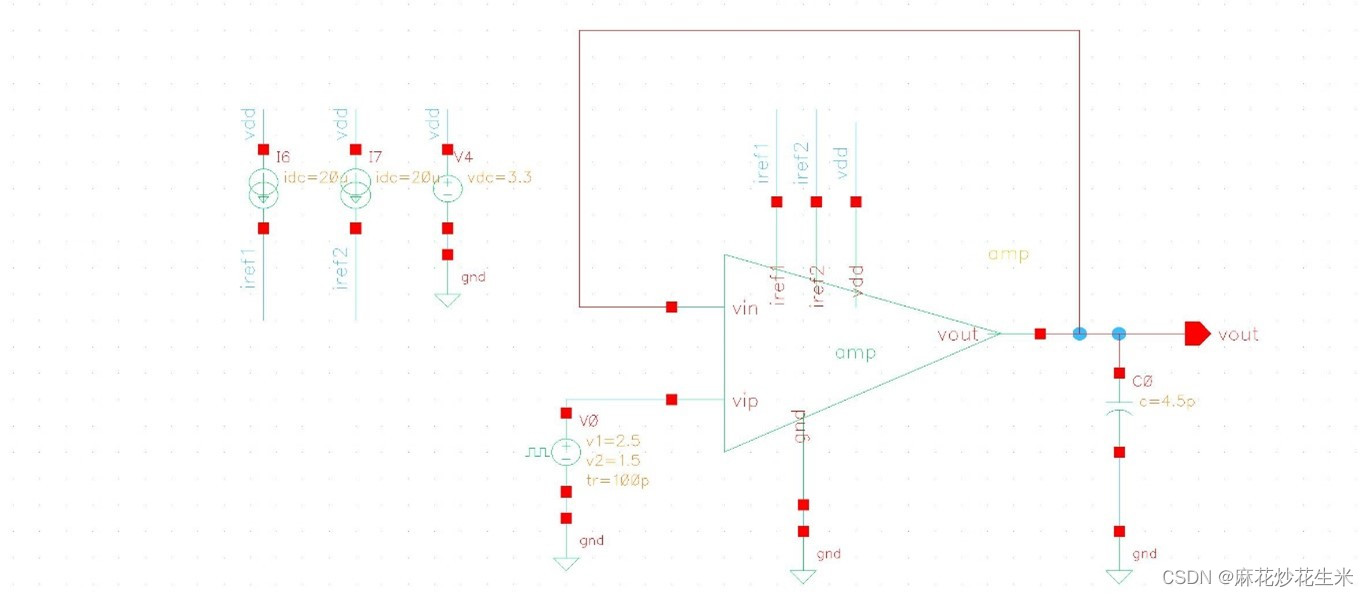

放大器转换速率测试电路

搭建闭环测试电路,构成单位增益负反馈时,当输入方波信号时测量输出信号的斜率即为运算放大器的转换速率。

MOS阈值测量结果

对NMOS测量阈值和Kn:

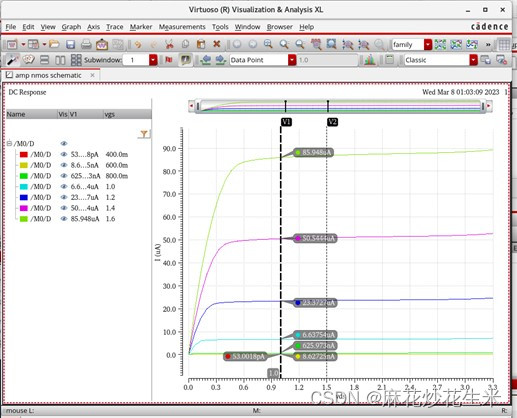

NMOS阈值测量结果图1

NMOS阈值测量结果图2

NMOS管阈值测量结果

| W/L = 2um/1um | Vgs = 1.4v | Vgs = 1.6v |

| Vds = 1v | 50.544uA | 85.948uA |

| Vds = 1.5v | 51.026uA | 86.843uA |

带入引入沟道调制效应的公式

Ids=12μnCoxVgs-Vth2(1+γVds)

令Kn=μnCox,

得γ=0.01944, Kn=1.15×10-4AV2, Vth=0.742V.

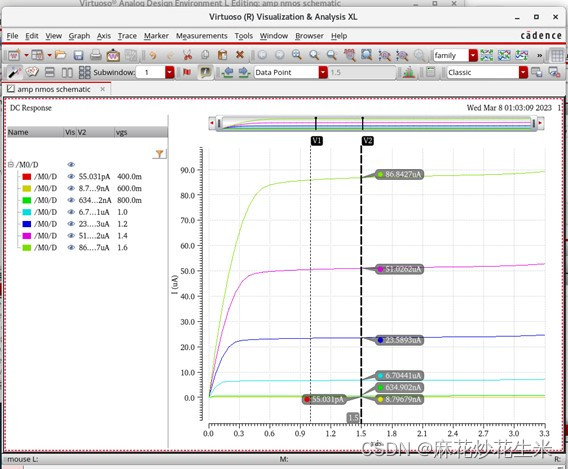

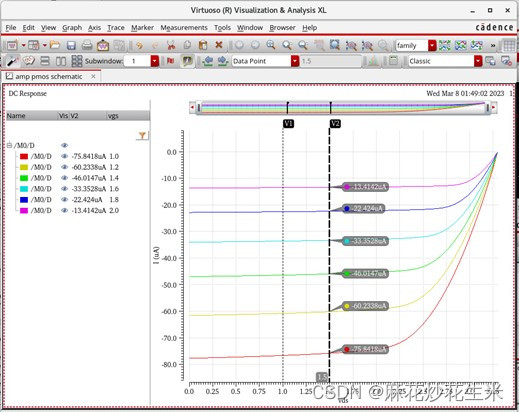

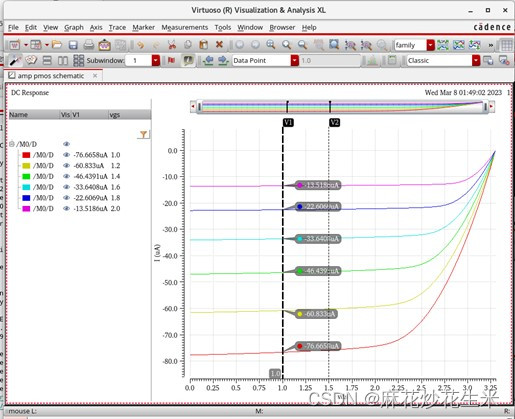

同理,对于PMOS来说可得

PMOS阈值测量结果图1

PMOS阈值测量结果图2

PMOS管阈值测量结果

| W/L = 2um/1um | Vgs = 2.0v | Vgs = 1.8v |

| Vds = 1.5v | 13.518uA | 22.607uA |

| Vds = 1v | 13.414uA | 22.424uA |

带入引入沟道调制效应的公式

Ids=12μpCoxVgs-Vth2(1+γVds)

令Kp=μpCox,

得:γ=0.01564, Kp=2.83×10-5 AV2, Vth=0.617V

放大器开环测量结果

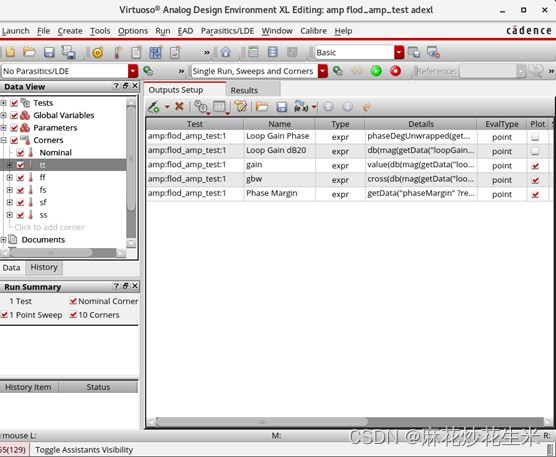

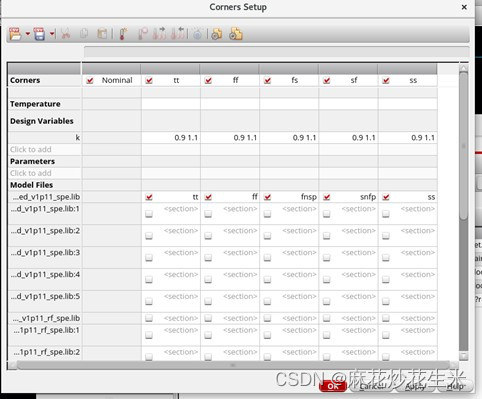

对于多工艺角的情况下的仿真一般调用ADE XL 进行仿真。通过设置多工艺角以及变量,可以一次性得到多个电路参数。

放大器开环测量结果1

放大器开环测量结果2

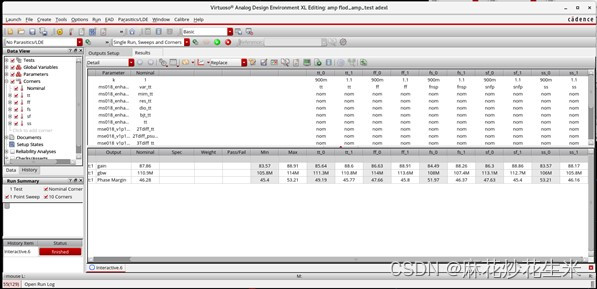

通过仿真结果可以看到各个 corner 下的增益,带宽,相位裕度情况:

各 corner 下测试结果

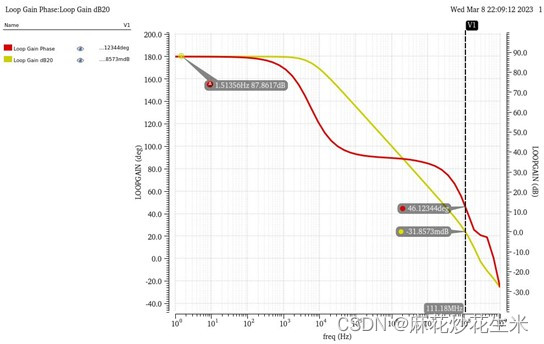

也可以通过画出相位和增益的曲线得到两者之间的结果:

相位、增益曲线

具体结果如下表所示。

开环测试结果

| Normal | Min | Max | |

| Gain(dB) | 87.86 | 83.57 | 88.91 |

| GBW (Mhz) | 110.9 | 105.8 | 114 |

| PM (°) | 46.28 | 45.4 | 53.21 |

以上开环仿真结果都满足实验要求。

放大器转换测速测量结果

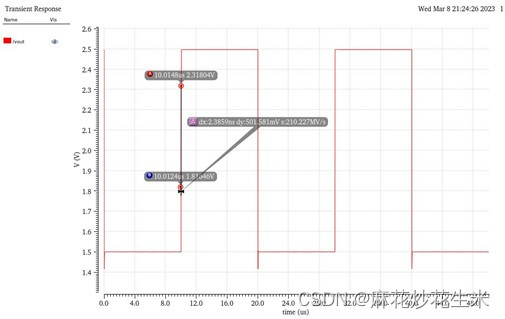

对于闭环仿真结果,通过测量瞬态斜率可得:

瞬态仿真曲线图

对于输入的方波信号,通过计算斜率SR>210MV/s,远远大于目标要求。其他工艺角也都满足设计要求。

总结

本设计实现了高速高增益的折叠式共源共栅运算放大器的设计,采用了经典的结构设计,实现了可靠的功能,各项指标均满足要求,该高增益高速运放可以应用于高速的模/数转换器(ADCs),也可以用作单位缓冲器作为多级运算放大器的输入级,具有不错的发展前景。