热门标签

热门文章

- 1App抓包提示网络异常怎么破?教你一招_xposed+justtrustme抓包依然断网

- 2java实现批量插入数据_java批量写入数据库

- 3相似图片分类 [华为]【并查集】_小明想要处理一批图片,将相似的图片分类。他首先对图片的特征采样,得到图片之间的

- 4JAVA提取嵌套夹带文件之Apache Tika_illegal ioexception from org.apache.tika.parser.mi

- 5关于mysql的lower_case_table_names引发的思考_mysql 查看lower_case_table_names

- 6SparkUI任务启动参数介绍(148个参数)_kyuubi.engine.submit.time

- 7【Git学习】在一台电脑上配置多个git账户(账户、来源)_多个git账号

- 8角色动画(六)——总结_人物动作k帧

- 9Git 2.33+版本 代码拉取失败缘由_fatal: invalid hash

- 10解决idea [08S01] 无法连接 sql server 数据库,报错:驱动程序无法通过使用安全套接字层(SSL)加密与 SQL Server 建立安全连接_sqlserver 08s01

当前位置: article > 正文

格雷码计数器_格雷码计数器的优点

作者:花生_TL007 | 2024-04-27 01:35:53

赞

踩

格雷码计数器的优点

作用:实现FIFO存储器读写指针比较好的方法就是使用格雷码计数器。格雷码计数器的优势在于其相邻两个数值之间只有一位发生变化,提高了系统的抗干扰能力,而且在计数时,各个输出的门电路翻转次数要远远小于二进制计数器,从而可以大幅度降低系统的功耗。

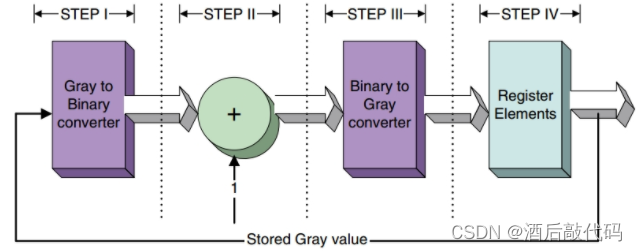

实现步骤:

- 将格雷值转换为二进制值。

- 根据条件递增二进制值。

- 将二进制值转换为格雷码

- 将计数器的最终格雷值保存到寄存器中。

格雷码转二进制

格雷码转二进制的公式如下:

binn−1 = grayn−1

bini = grayi⨁bini+1

格雷码转二进制Verilog代码如下:

- module gray_to_bin (gray,bin);

-

- parameter WIDTH = 8;

-

- input [WIDTH-1:0] gray;

- output [WIDTH-1:0] bin;

- wire [WIDTH-1:0] bin;

-

- assign bin[WIDTH-1] = gray[WIDTH-1];

- genvar i;

- generate

- for (i=WIDTH-2; i>=0; i=i-1)

- begin: gry_to_bin

- assign bin[i] = bin[i+1] ^ gray[i];

- end

- endgenerate

-

- endmodule

二进制转格雷码

二进制转格雷码公式如下:

grayn−1 = binn−1

grayi = bini⨁bini+1

二进制转格雷码Verilog代码如下:

- module bin_to_gray (bin,gray);

-

- parameter WIDTH = 8;

-

- input [WIDTH-1:0] bin;

- output [WIDTH-1:0] gray;

- wire [WIDTH-1:0] gray;

-

- assign gray = bin ^ (bin >> 1);

- endmodule

格雷码计数器

将四个步骤组合在一起(格雷码转二进制、加法器、二进制转格雷码、保存格雷码的寄存器)即可实现格雷码计数器,其Verlog代码如下:

- module gray_counter(clk, rst_n, gray_dout);

- parameter WIDTH = 8;

- input clk;

- input rst_n;

- output [WIDTH-1:0] gray_dout;

-

- reg [WIDTH-1:0] gray_dout;

- wire [WIDTH-1:0] gray_temp;

- wire [WIDTH-1:0] bin_dout;

- wire [WIDTH-1:0] bin_add;

-

- assign bin_add = bin_out + 1'b1;

- assign gray_temp = bin_add ^ (bin_add >> 1);

- always@(posedge clk or negedge rst_n) begin

- if(!rst_n)

- gray_dout <= {WIDTH{1'b0}};

- else

- gray_dout <= gray_temp;

- end

-

- gray_to_bin gtb(.gray(gray_dout), .bin(bin_dout));

- defparam gtb .WIDTH = WIDTH;

-

- endmodule

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/花生_TL007/article/detail/494147

推荐阅读

相关标签