热门标签

热门文章

- 1服务级别协议 (SLA)管理_sla管理

- 2MySQL5.7升级到MySQL8.0的最佳实践分享_数据库5.7升级到8.0

- 3AI一键去衣技术:窥见深度学习在图像处理领域的革命(最后有彩蛋)_ai去衣

- 41064 -you have an error in your SQL syntax_在linux中运行select id from 'book' limit 100报1064 - yo

- 5【SQL语法】MySql、Oracle、SqlServer实现批量插入insert_sqlserver insert

- 6NLP(二)词袋模型及余弦相似度、编辑距离相似度_用开源embedding模型测试句子余弦距离

- 7客达天下项目案例

- 8【刷题记录15】Java工程师丨腾讯面试真题(3)

- 9uniapp中加载Echarts图表H5可以显示正常图表, 打包app图表不显示的问题_uniapp打包发布至app端 echarts图表不显示问题

- 10整数对最小和【华为OD机试JAVA题解】

当前位置: article > 正文

Vivado工程创建、仿真、下载与固化全流程_vivado下载程序到板子

作者:花生_TL007 | 2024-05-26 22:10:56

赞

踩

vivado下载程序到板子

本文以一个简单工程为例,介绍使用Vivado新建工程、代码的编写、Testbench代码的编写、波形仿真分析、引脚约束、生成bit流文件、通过JTAG将网表下载到开发板、程序的固化与下载全流程。

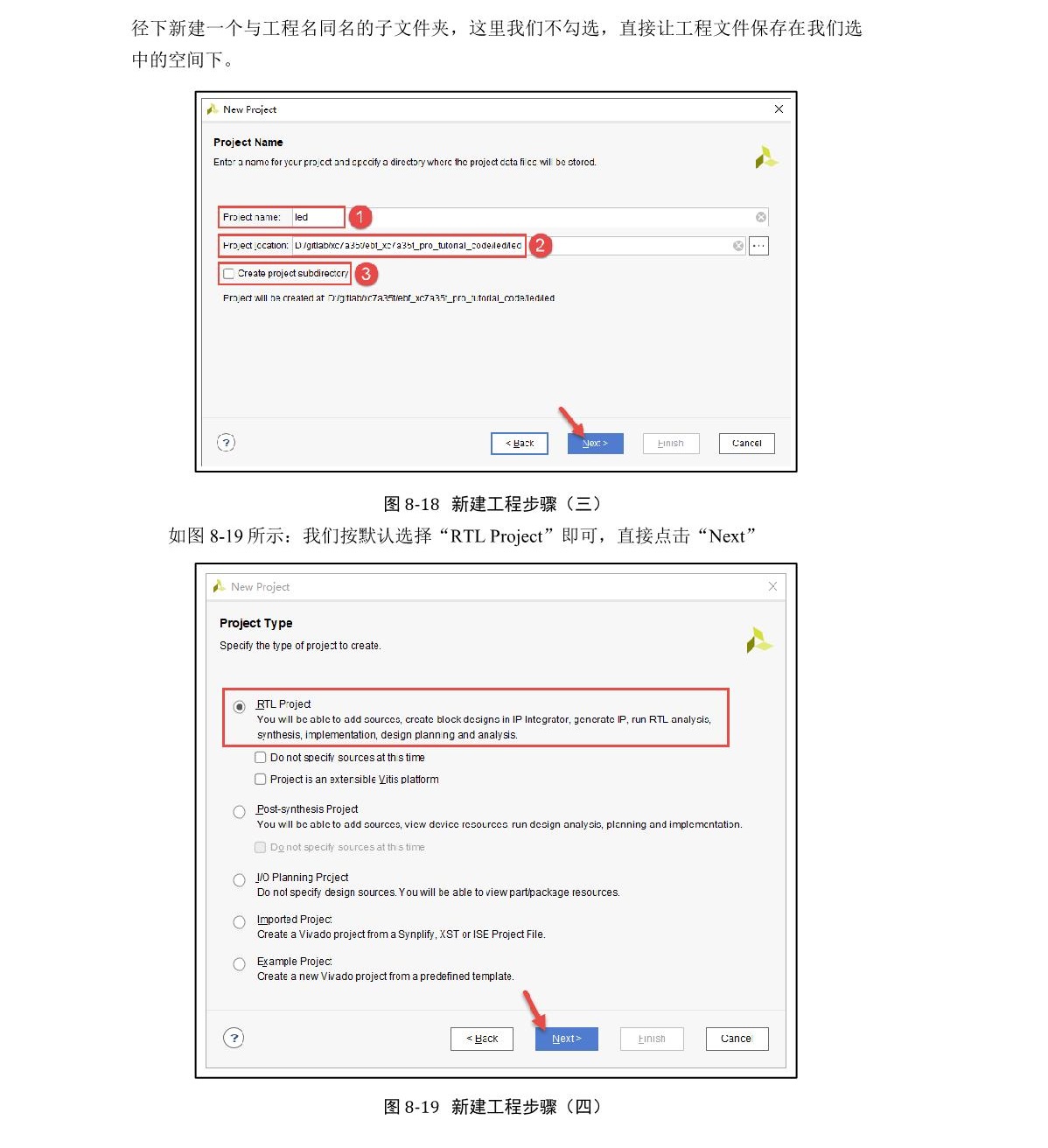

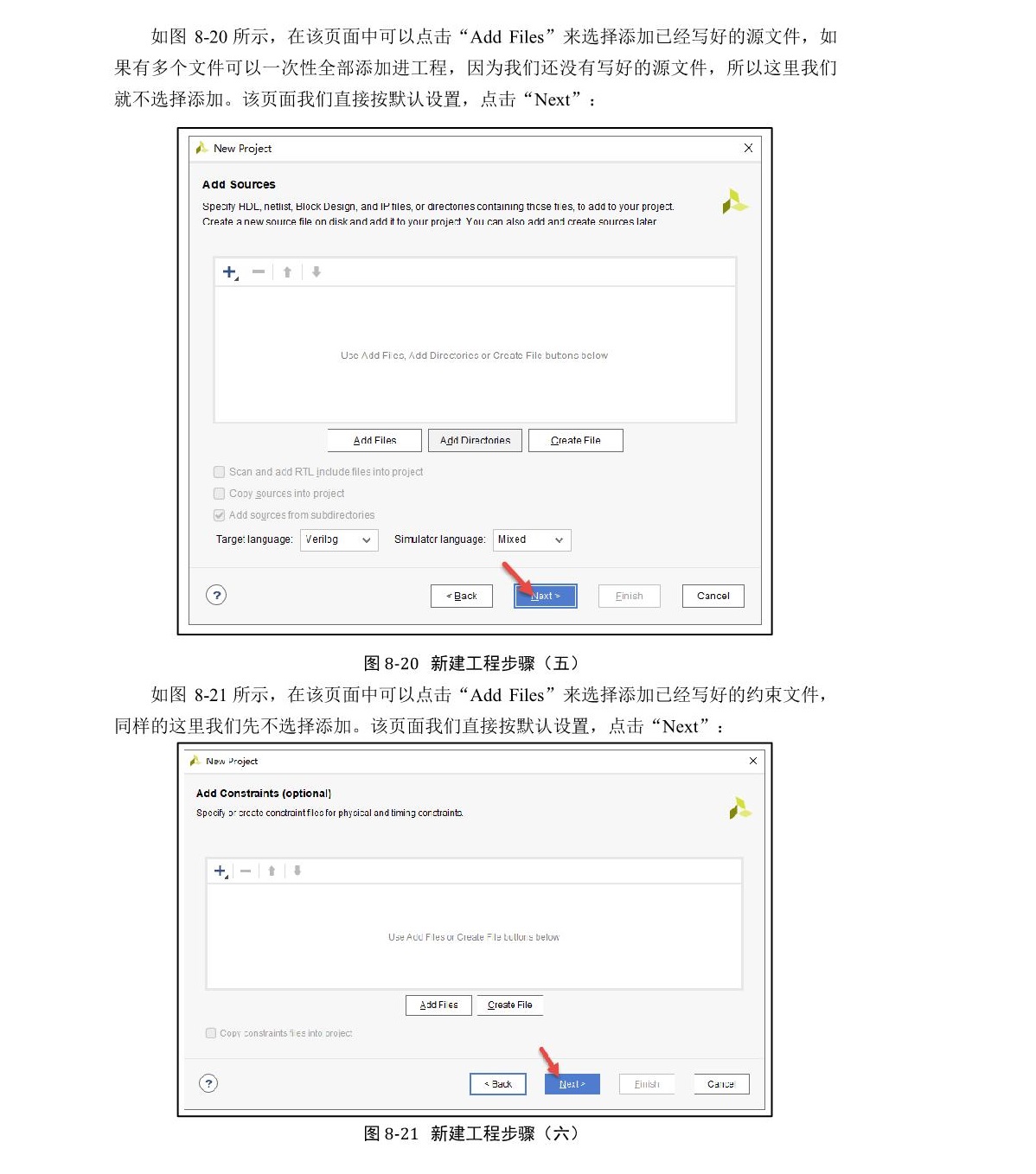

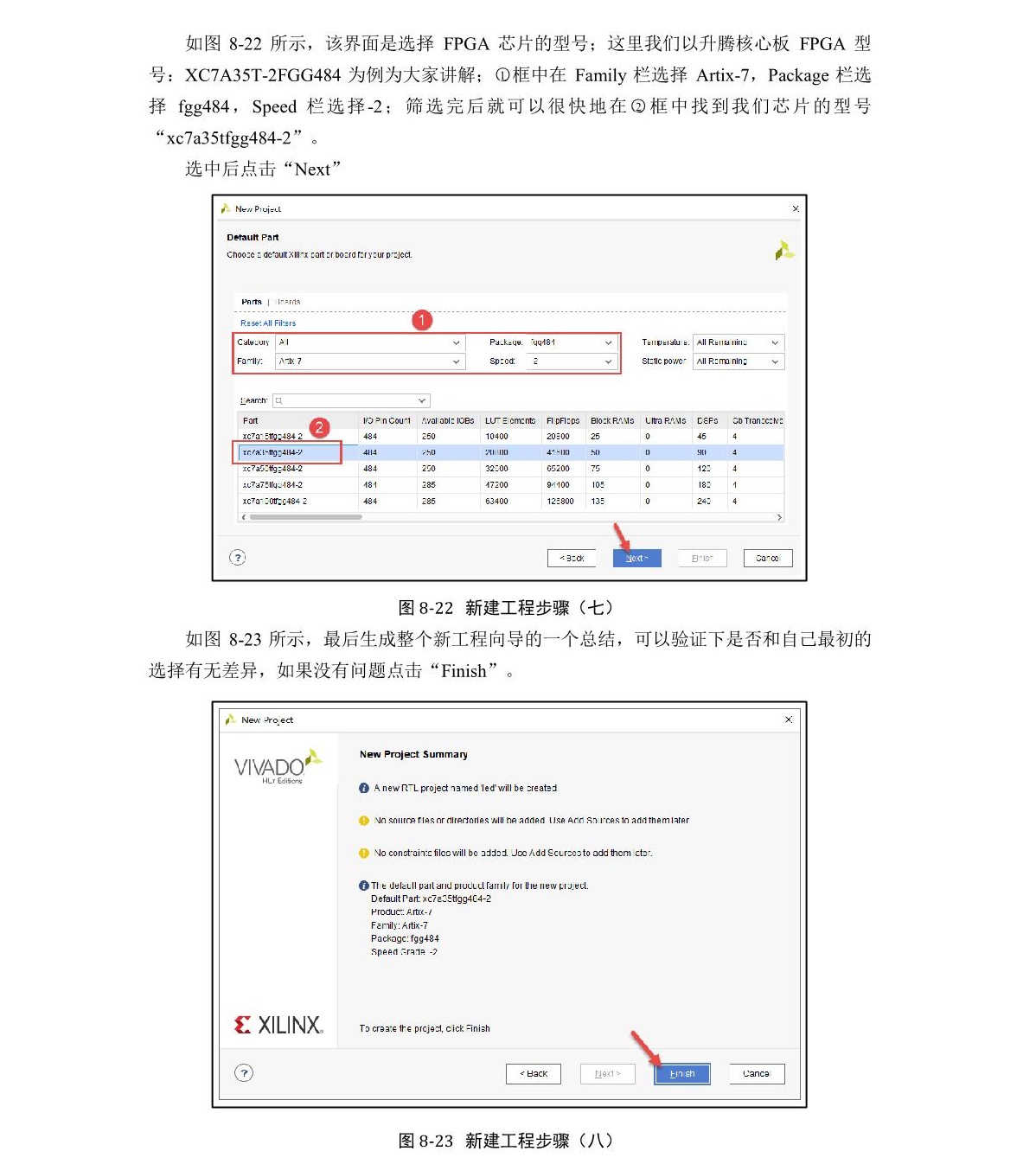

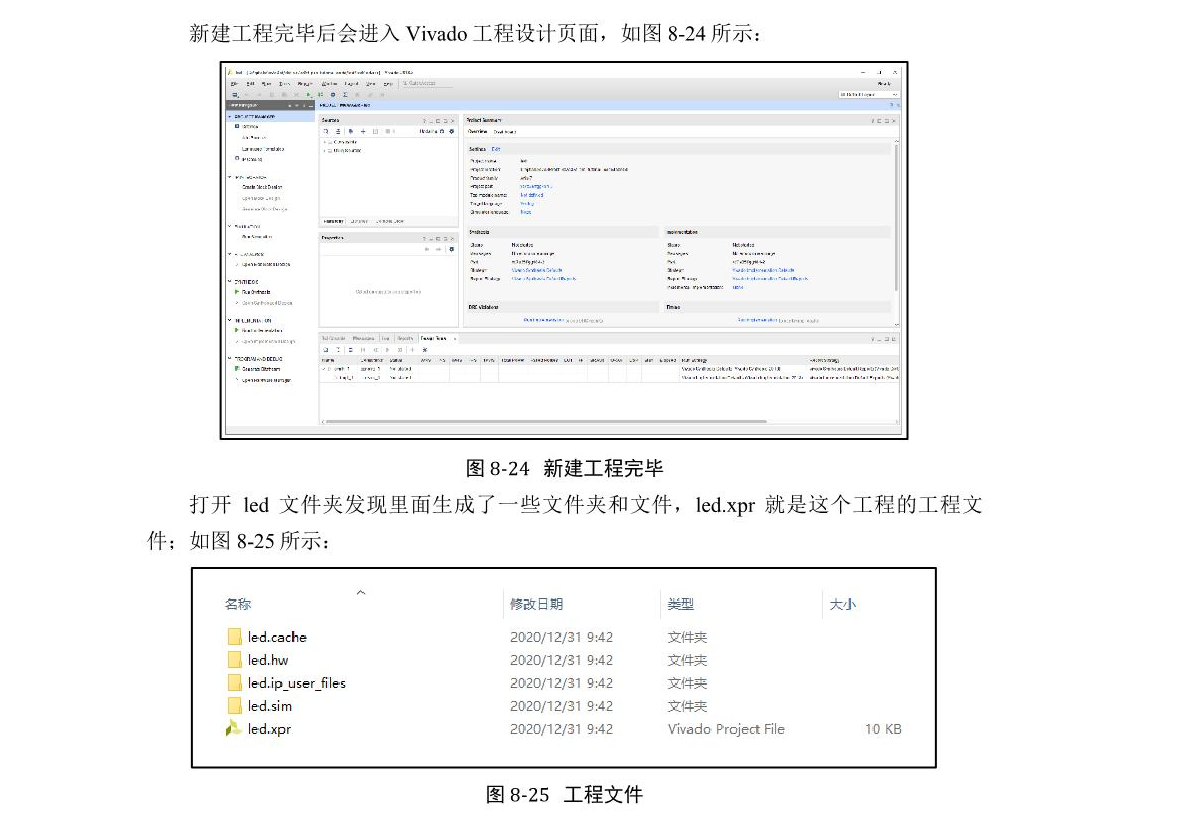

1.新建工程

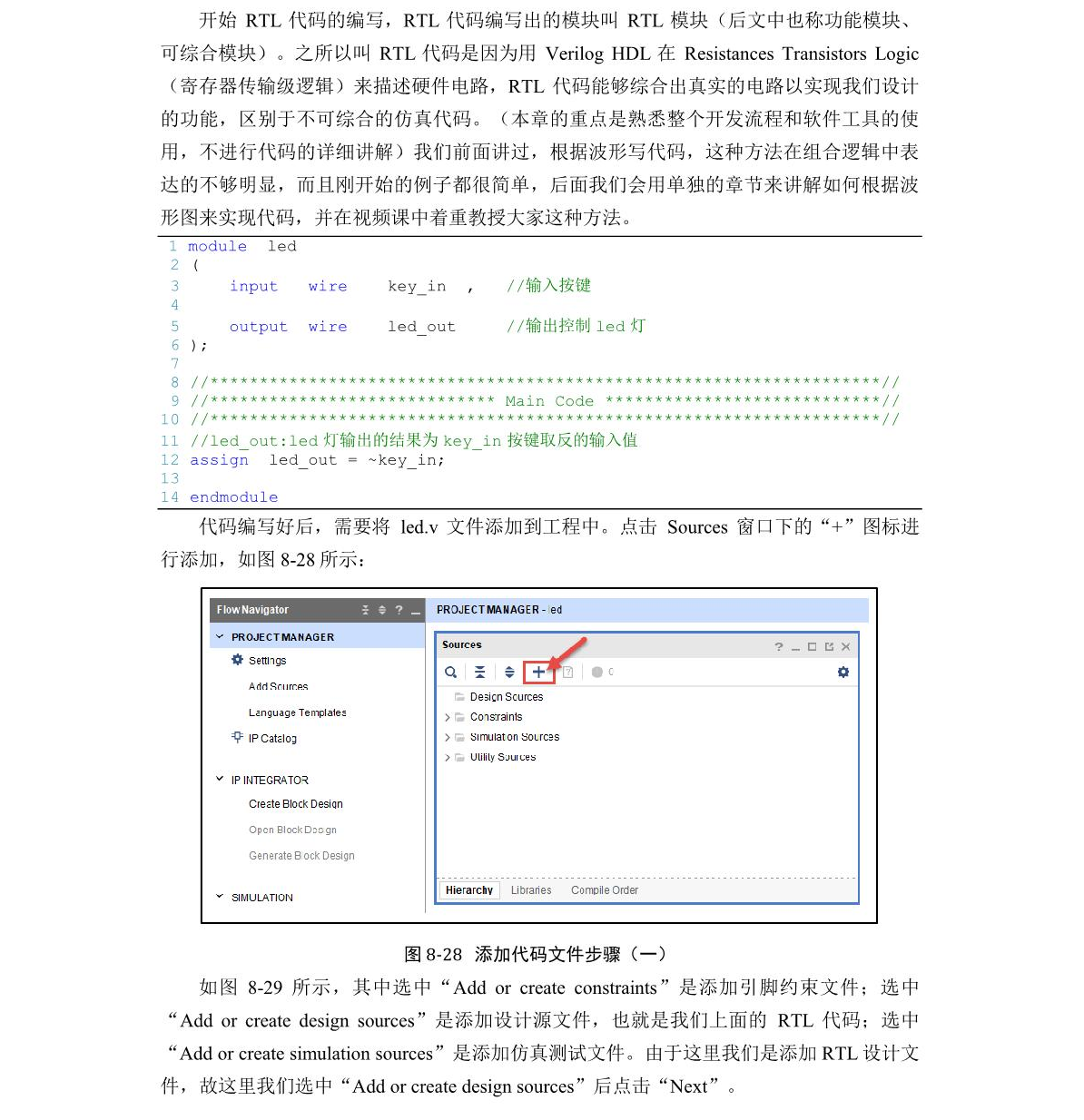

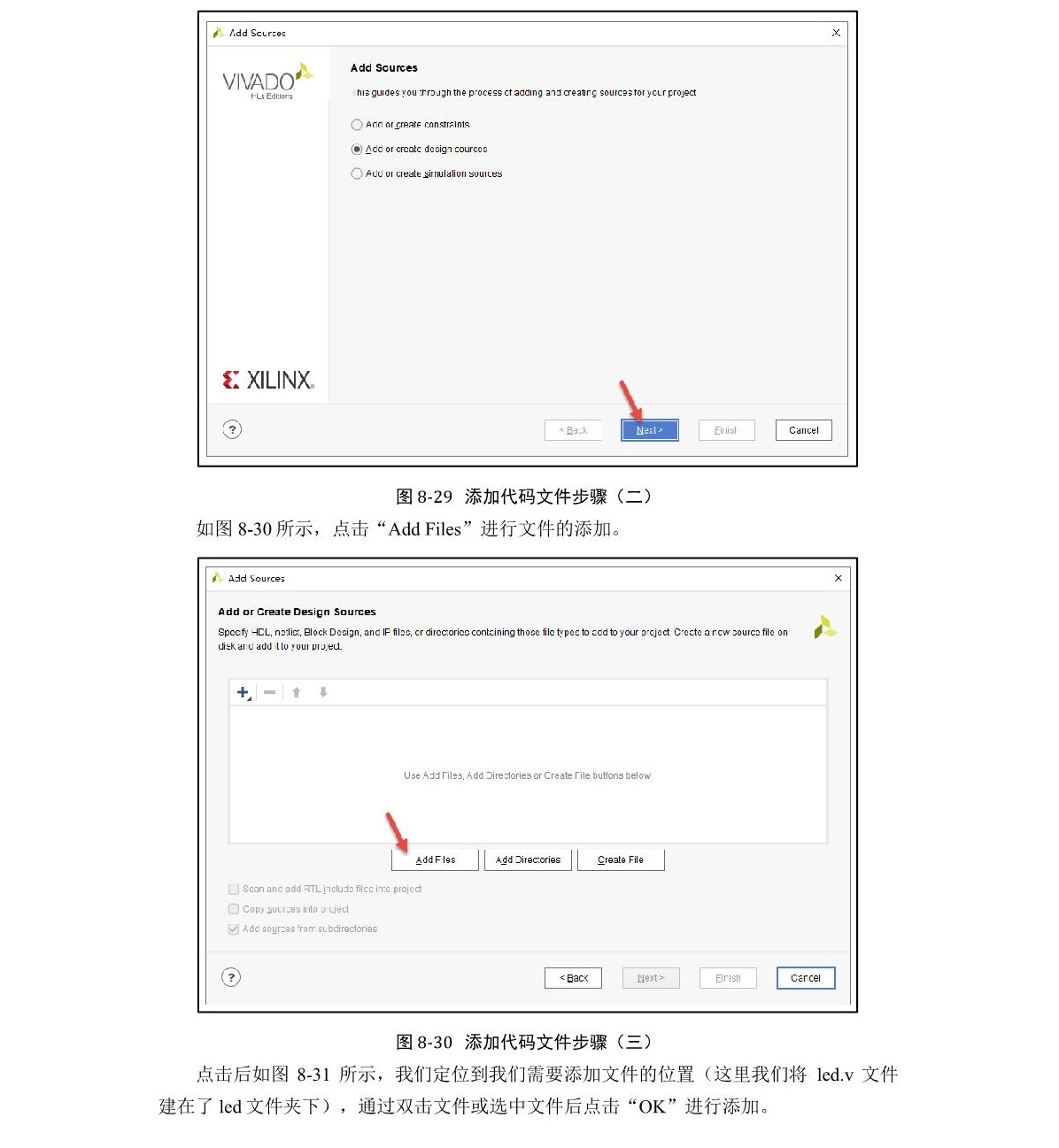

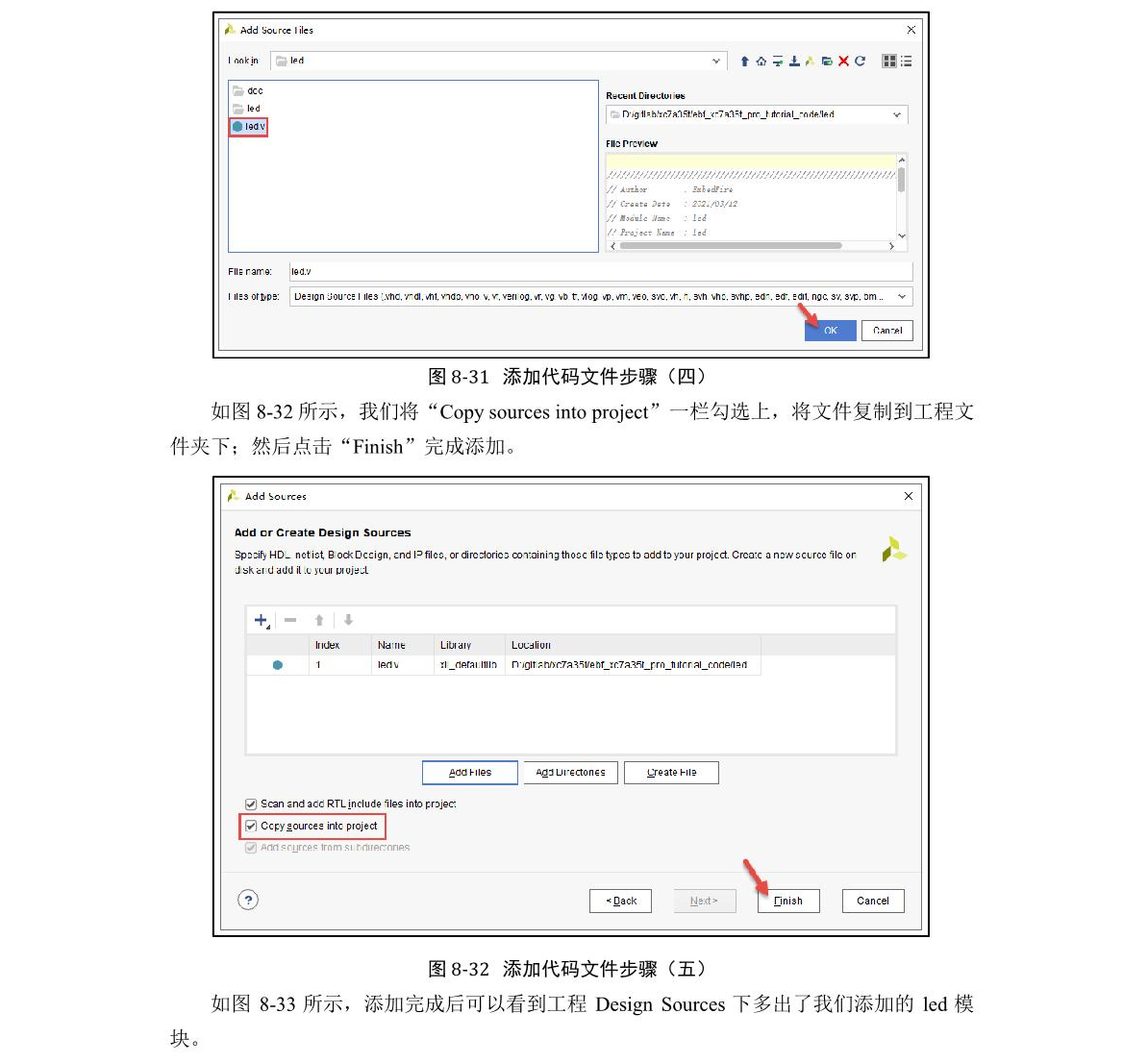

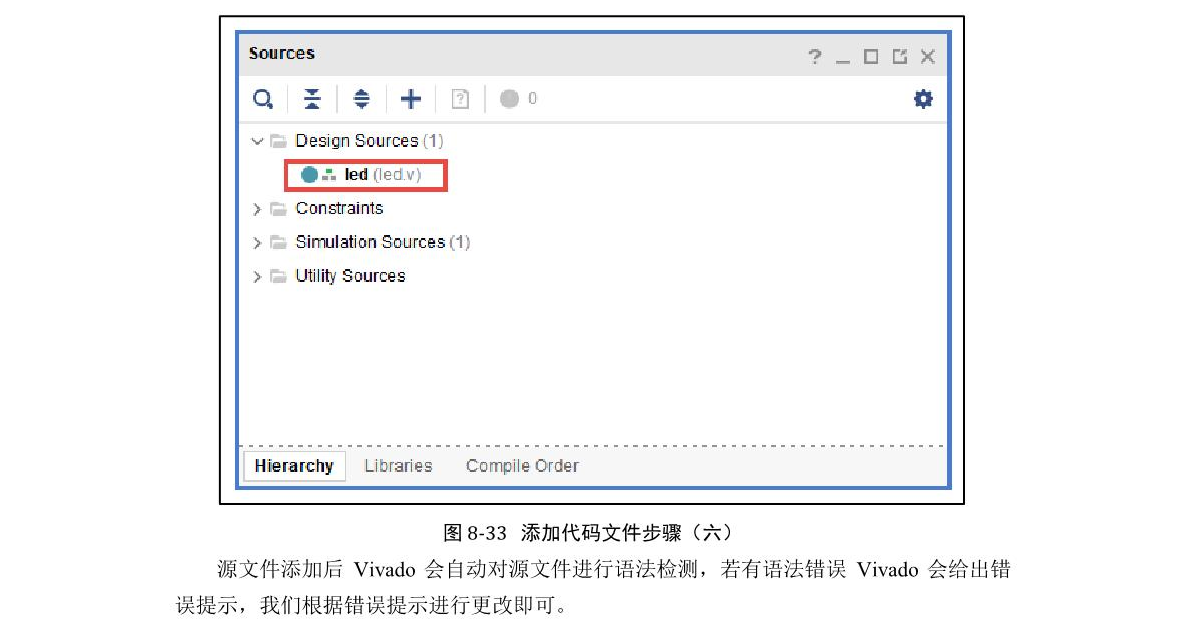

2.RTL代码的编写

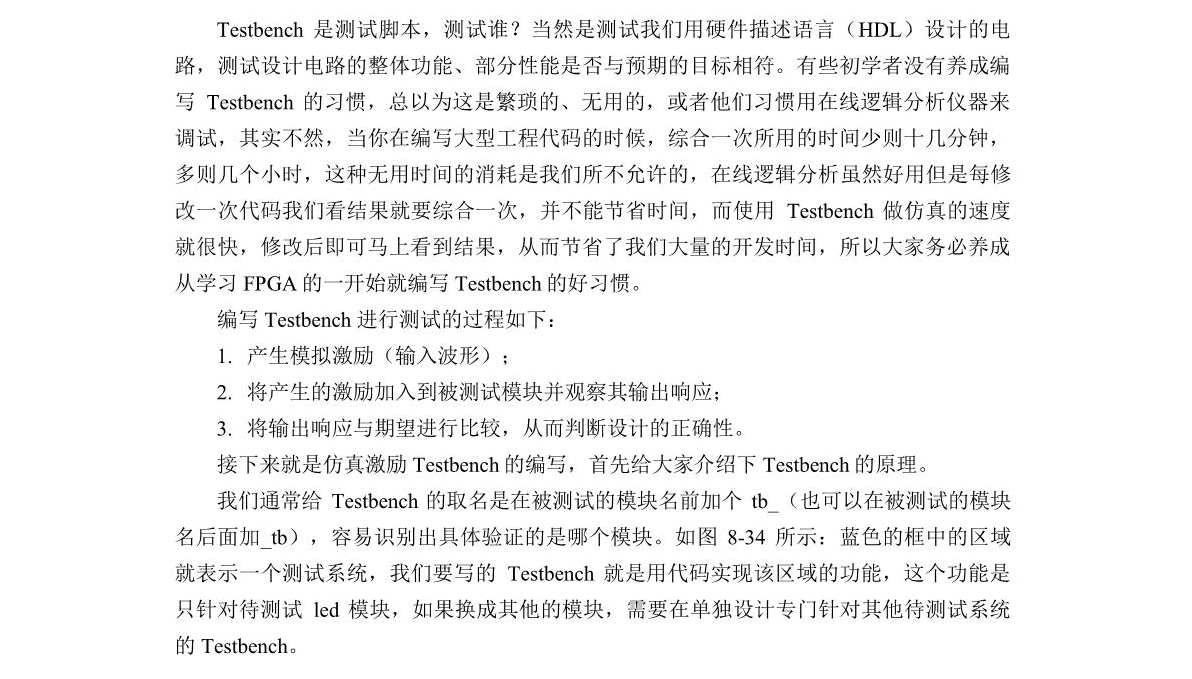

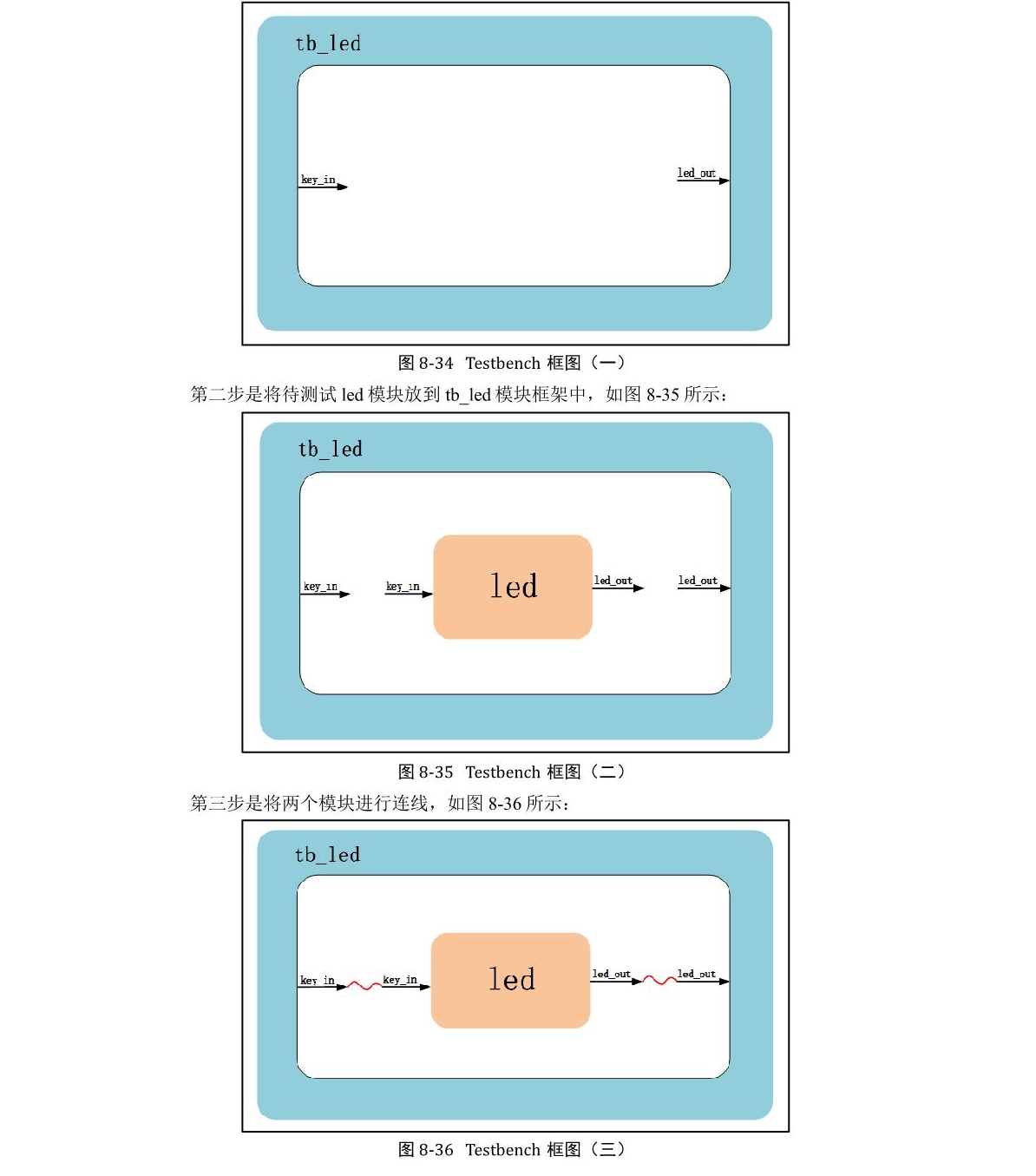

3.Testbench的原理

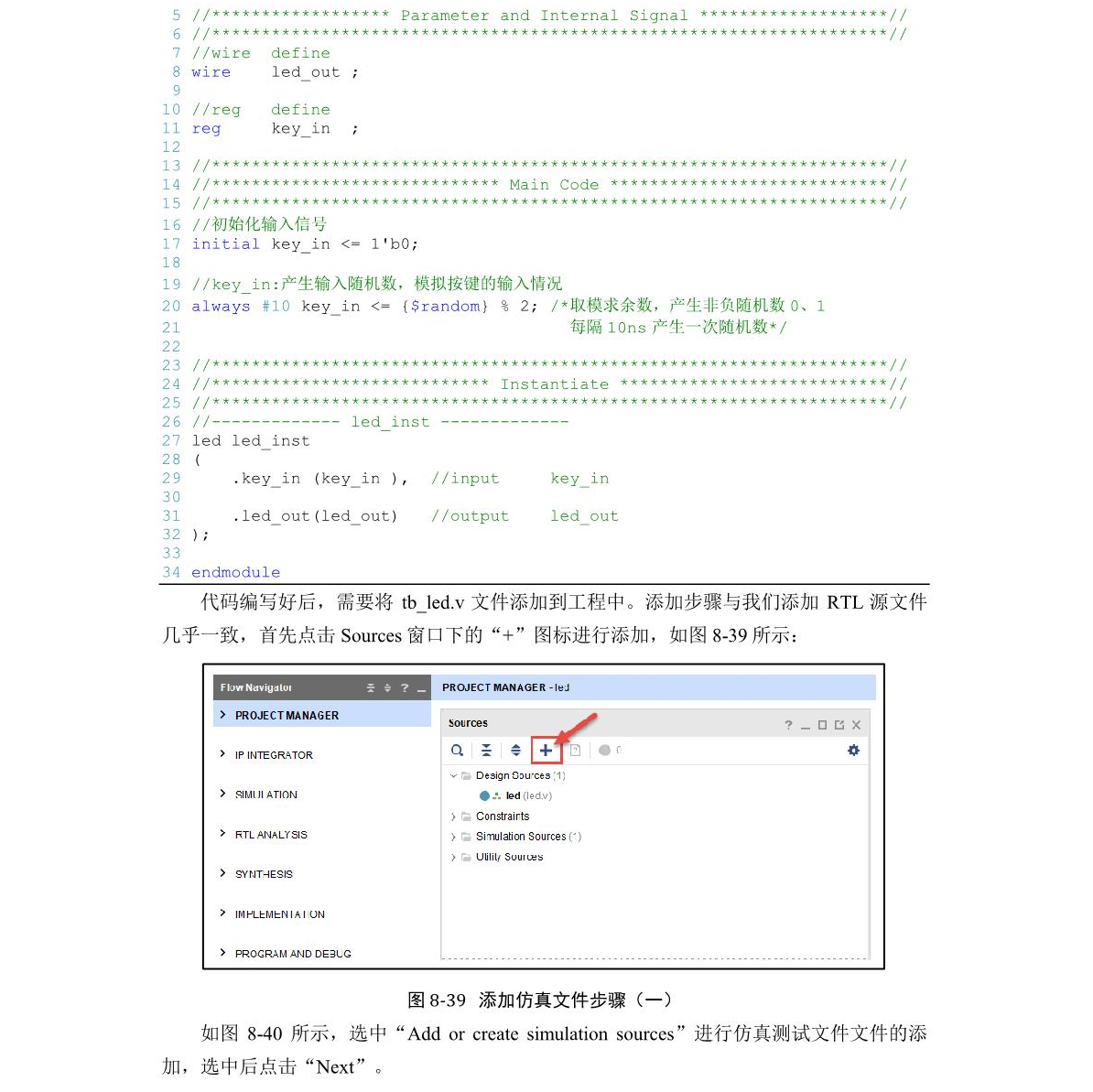

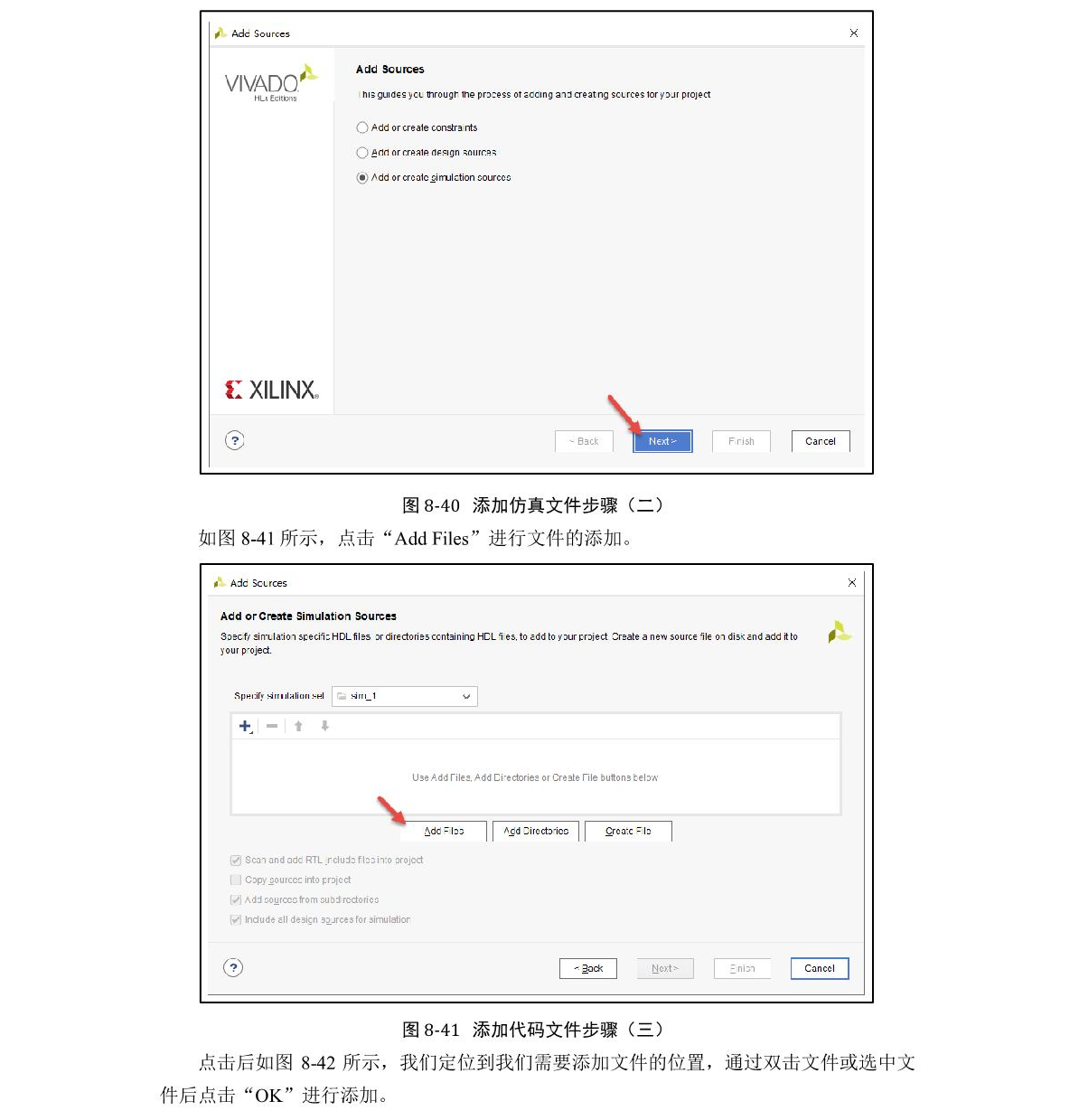

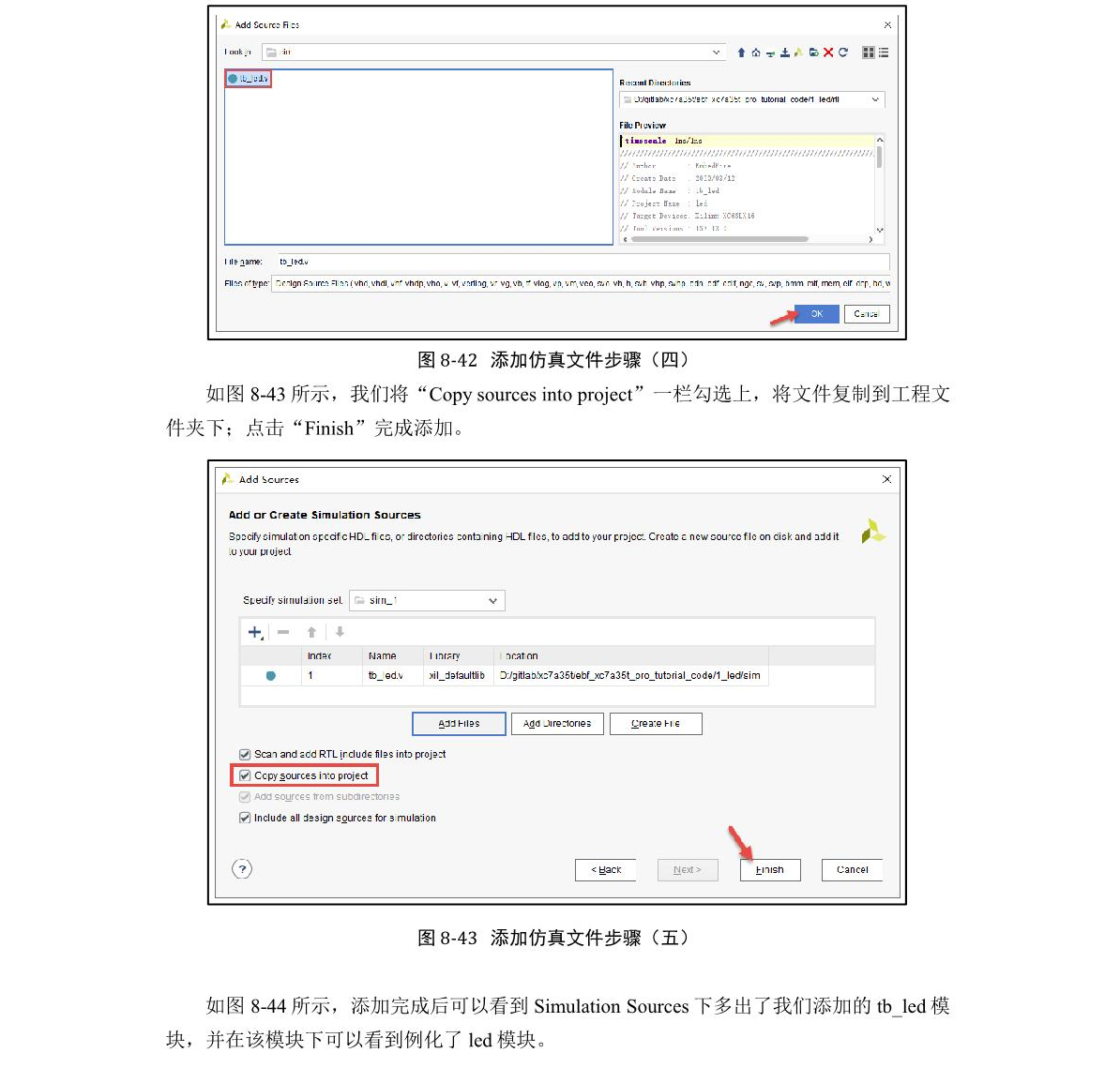

4.Testbench代码的编写

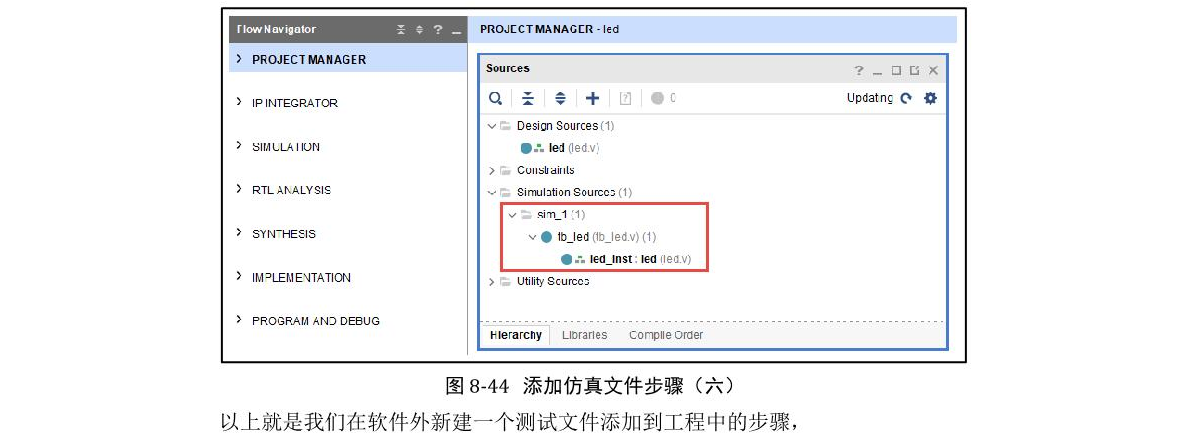

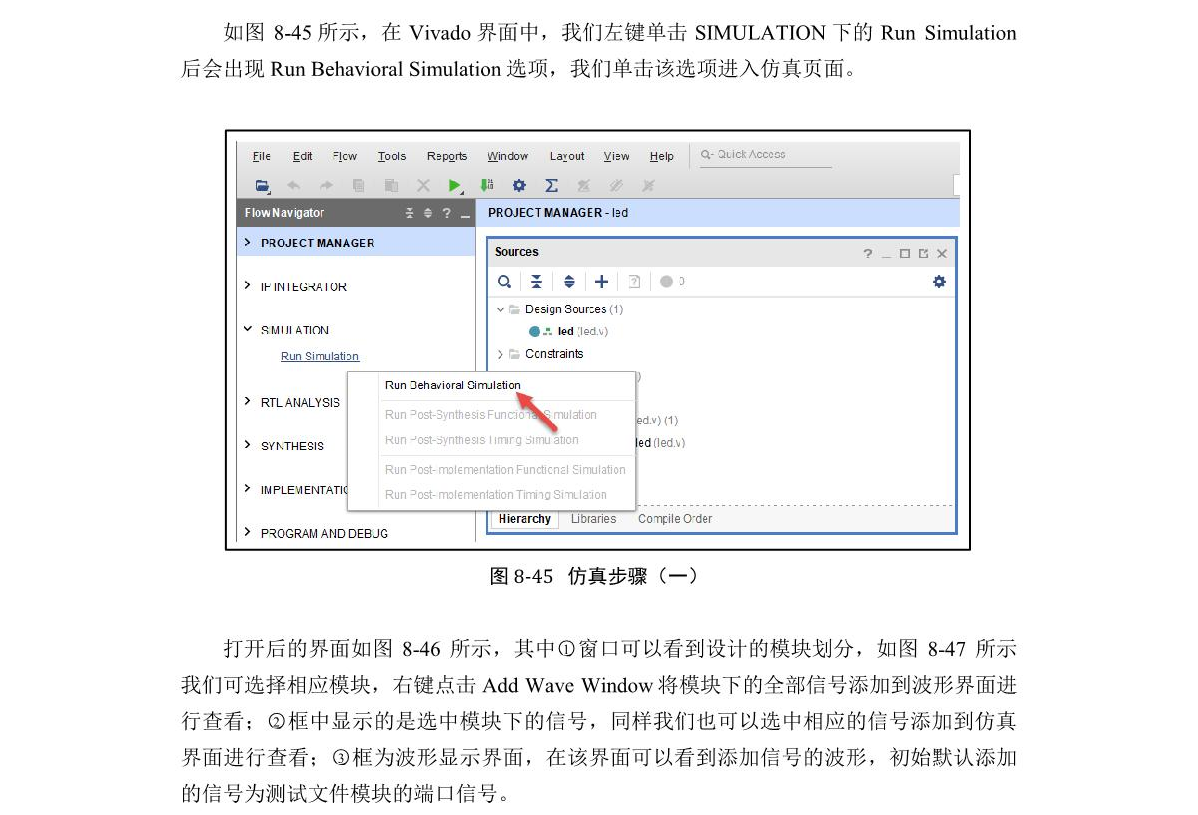

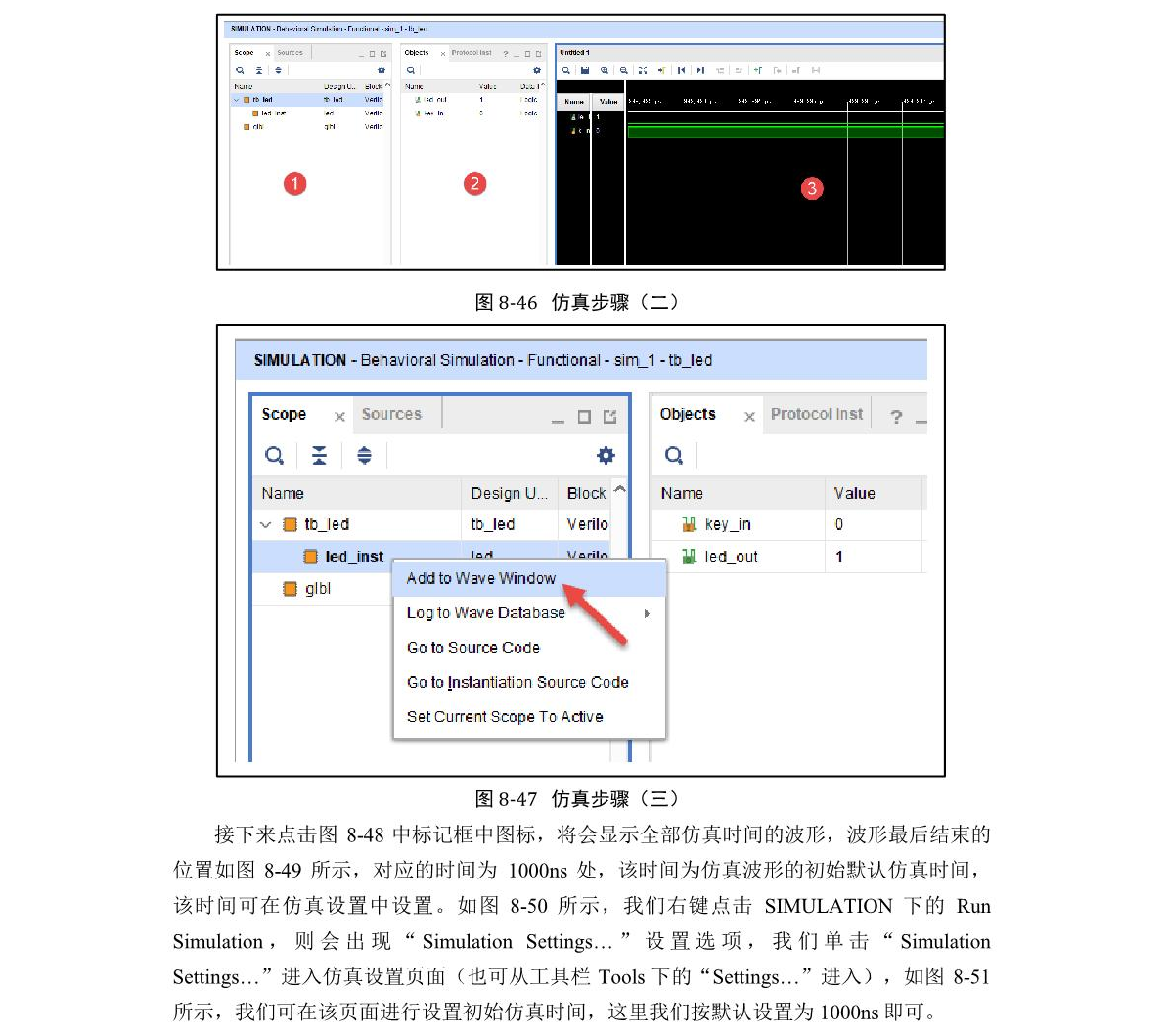

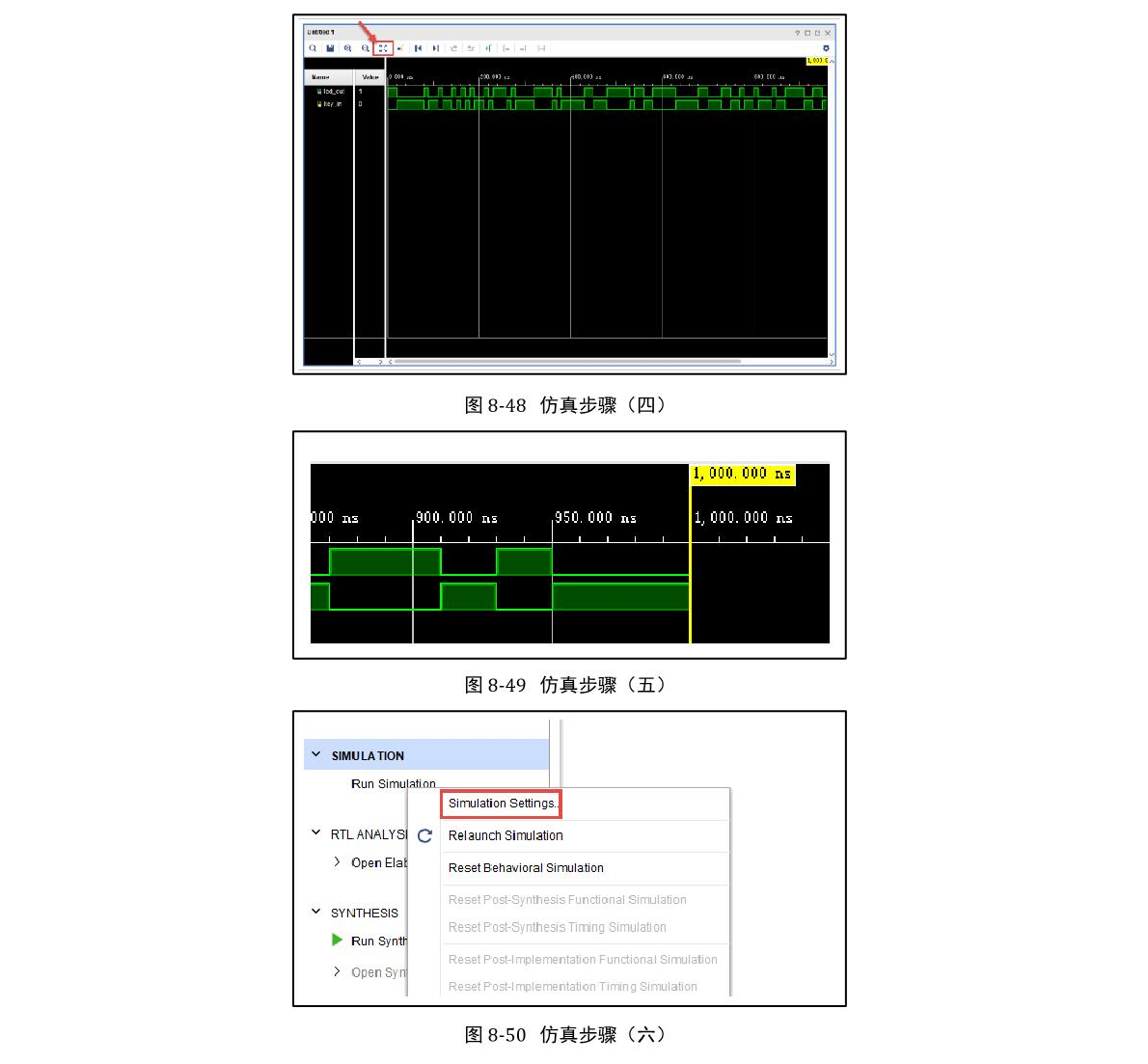

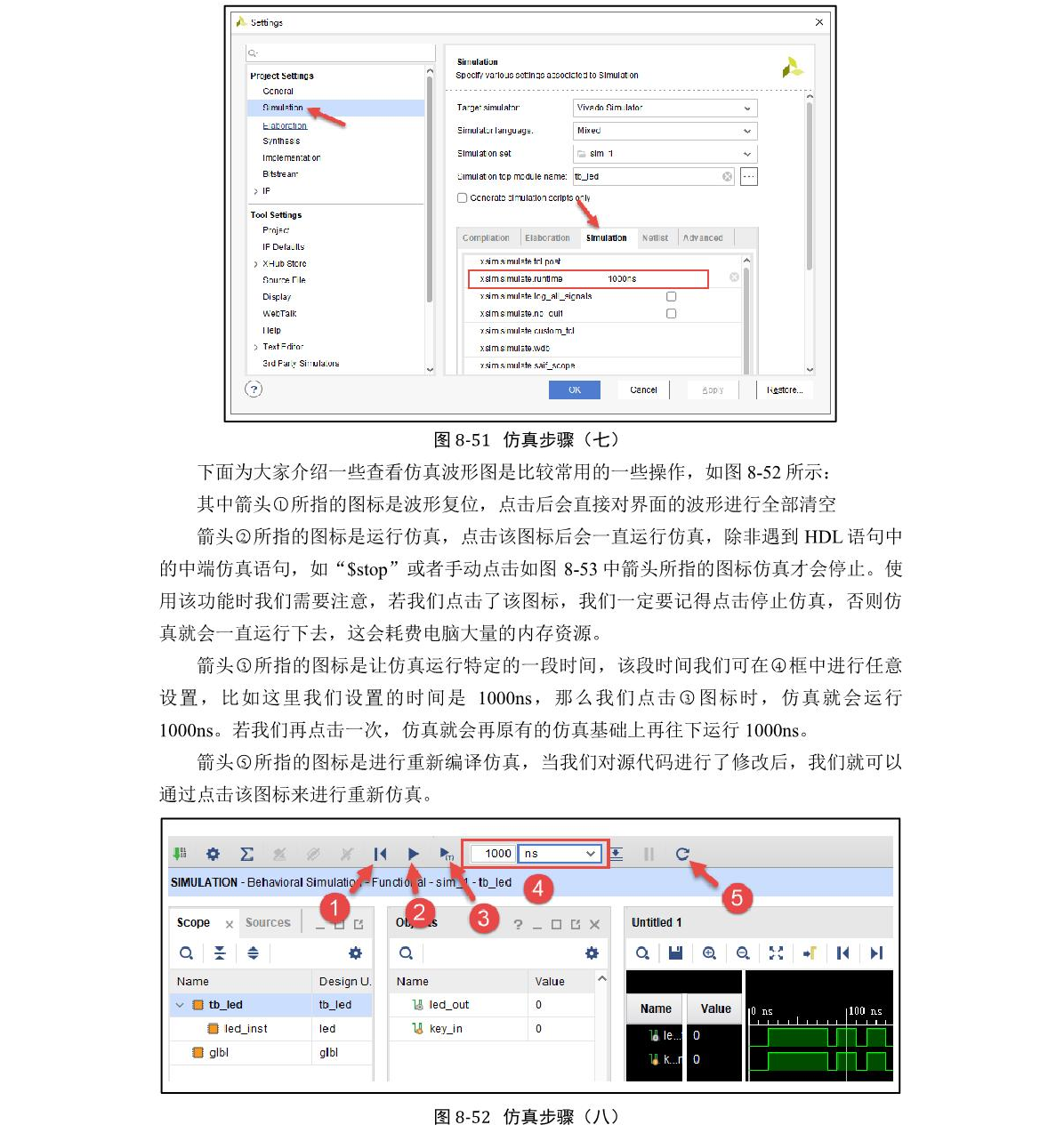

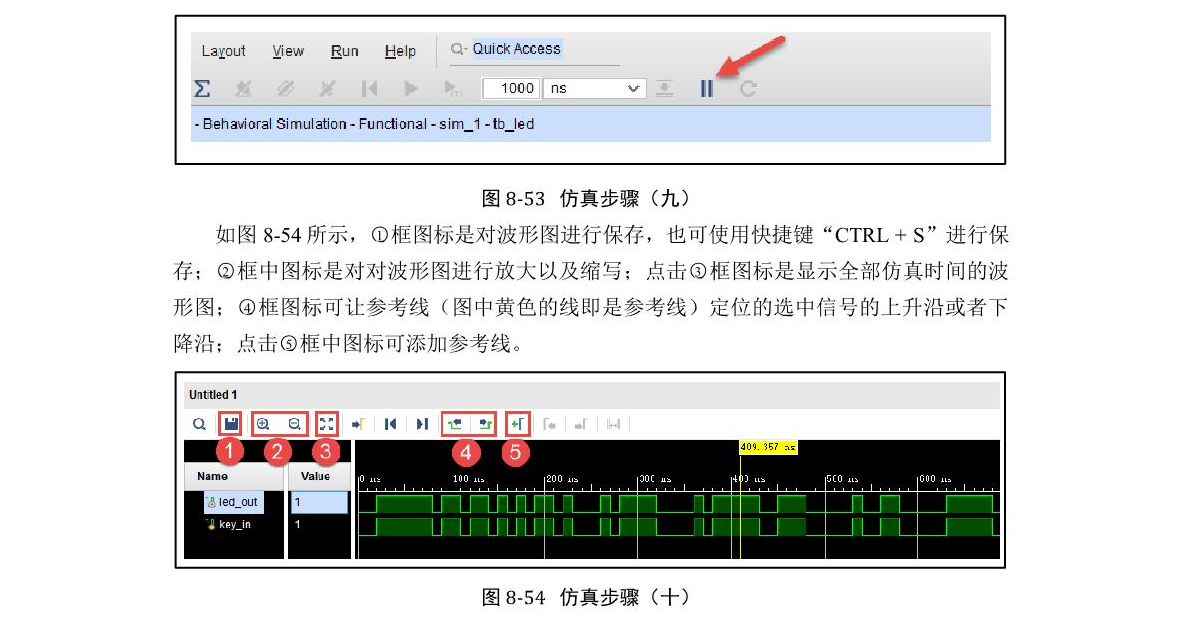

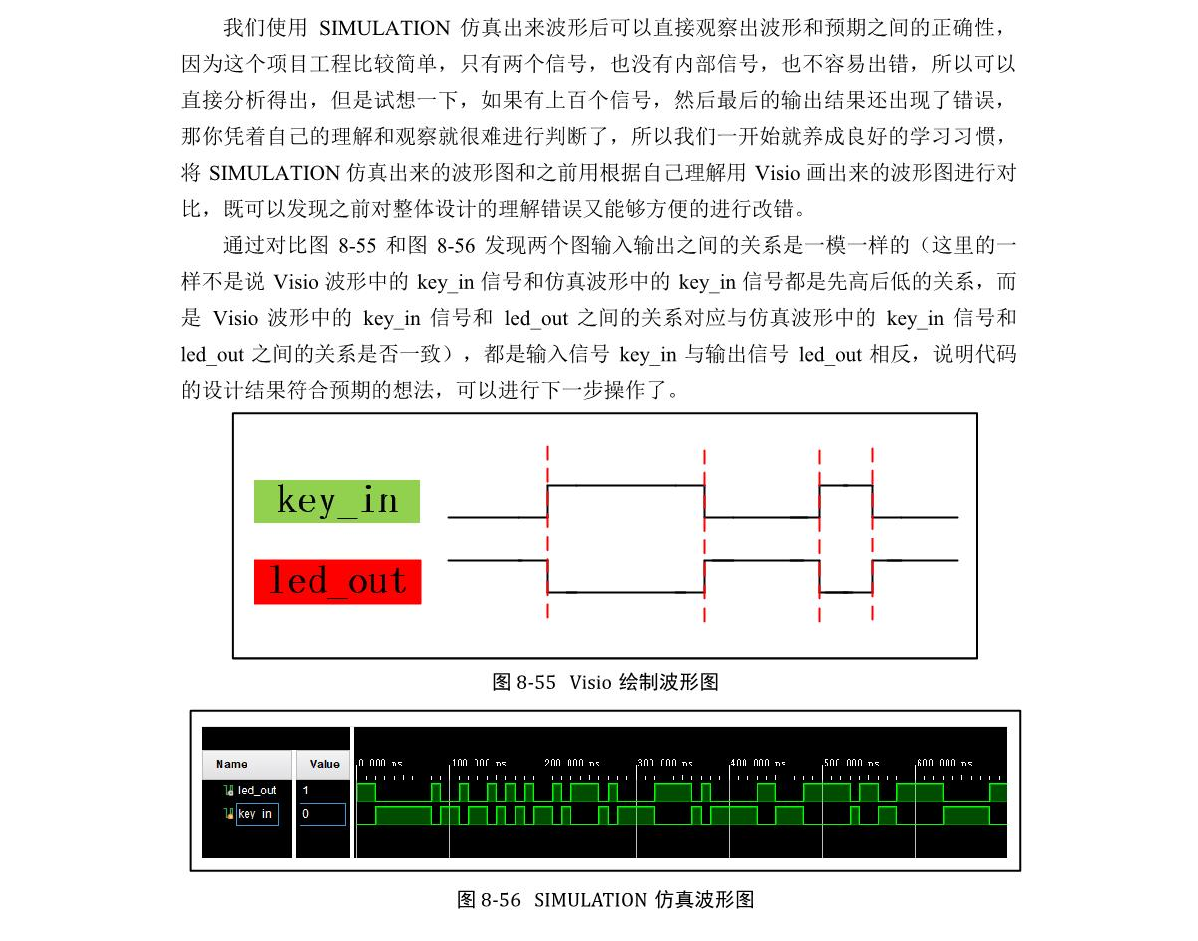

5.打开SIMULATION观察波形

6.仿真波形分析

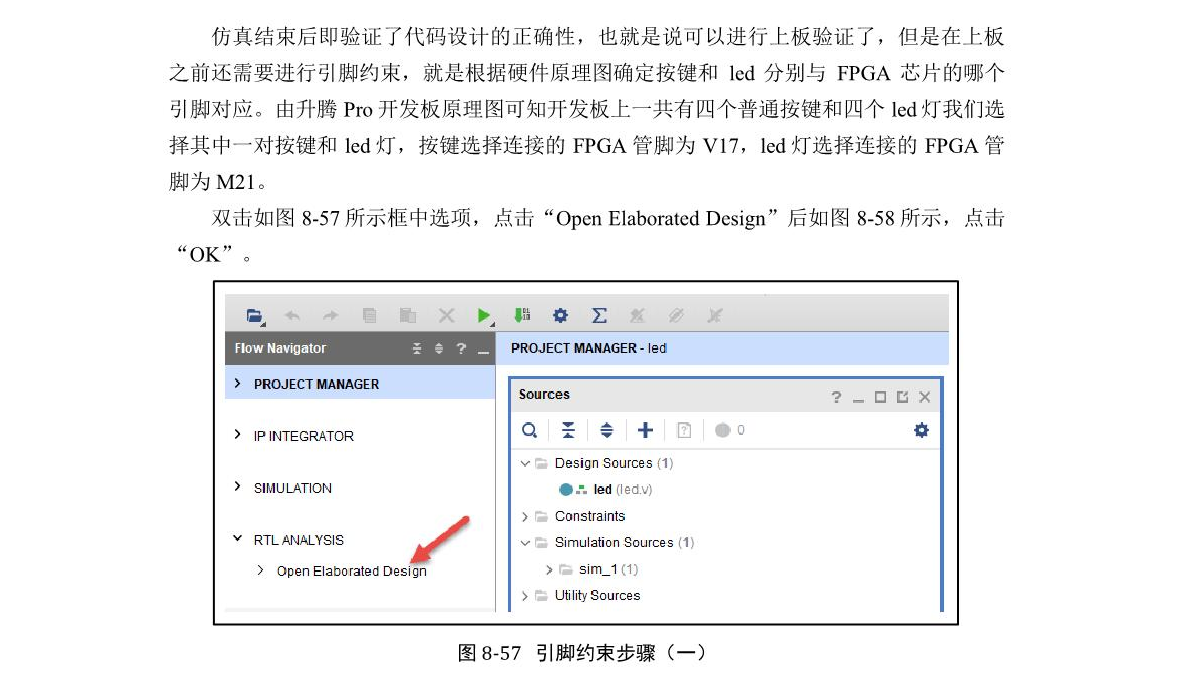

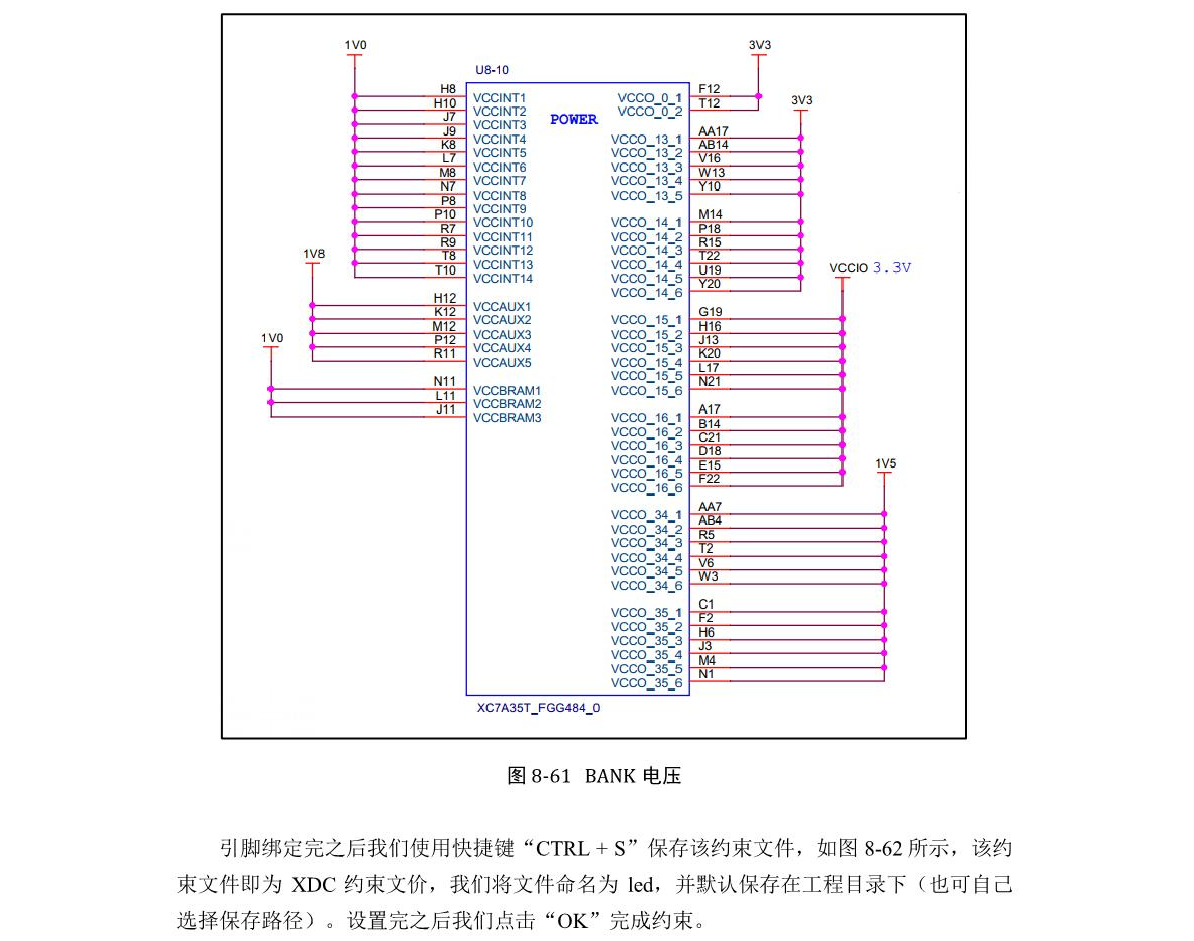

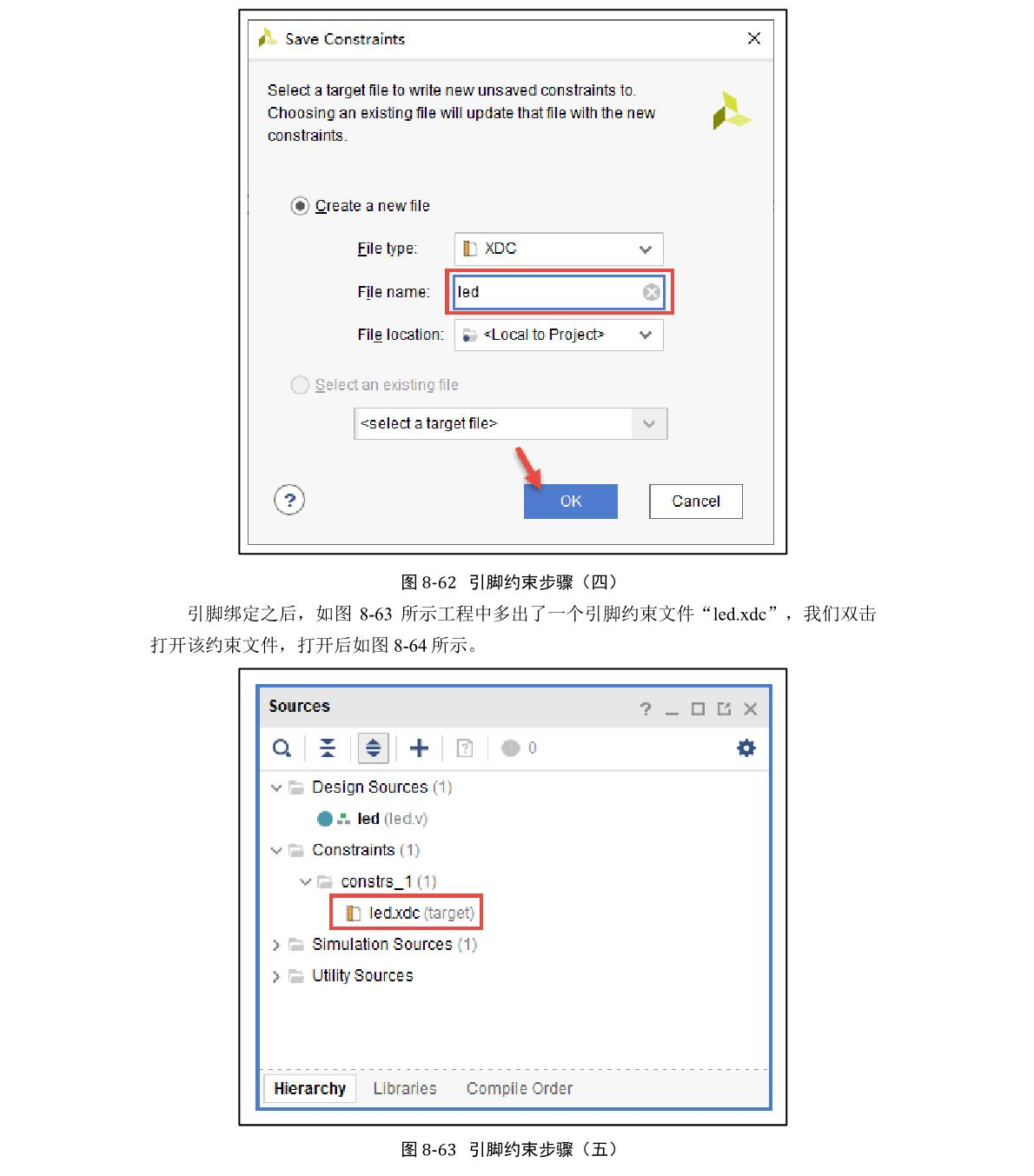

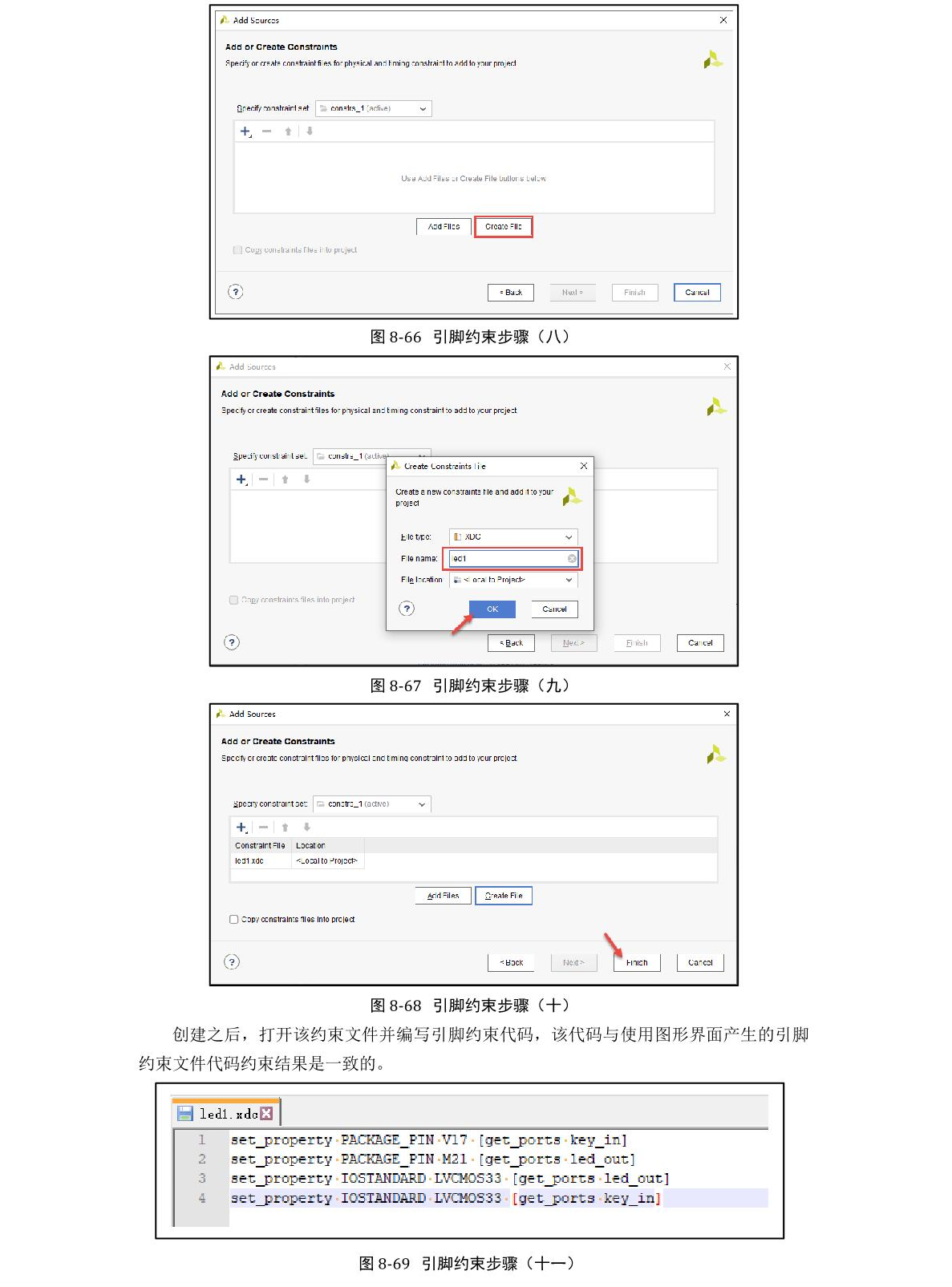

7.引脚约束

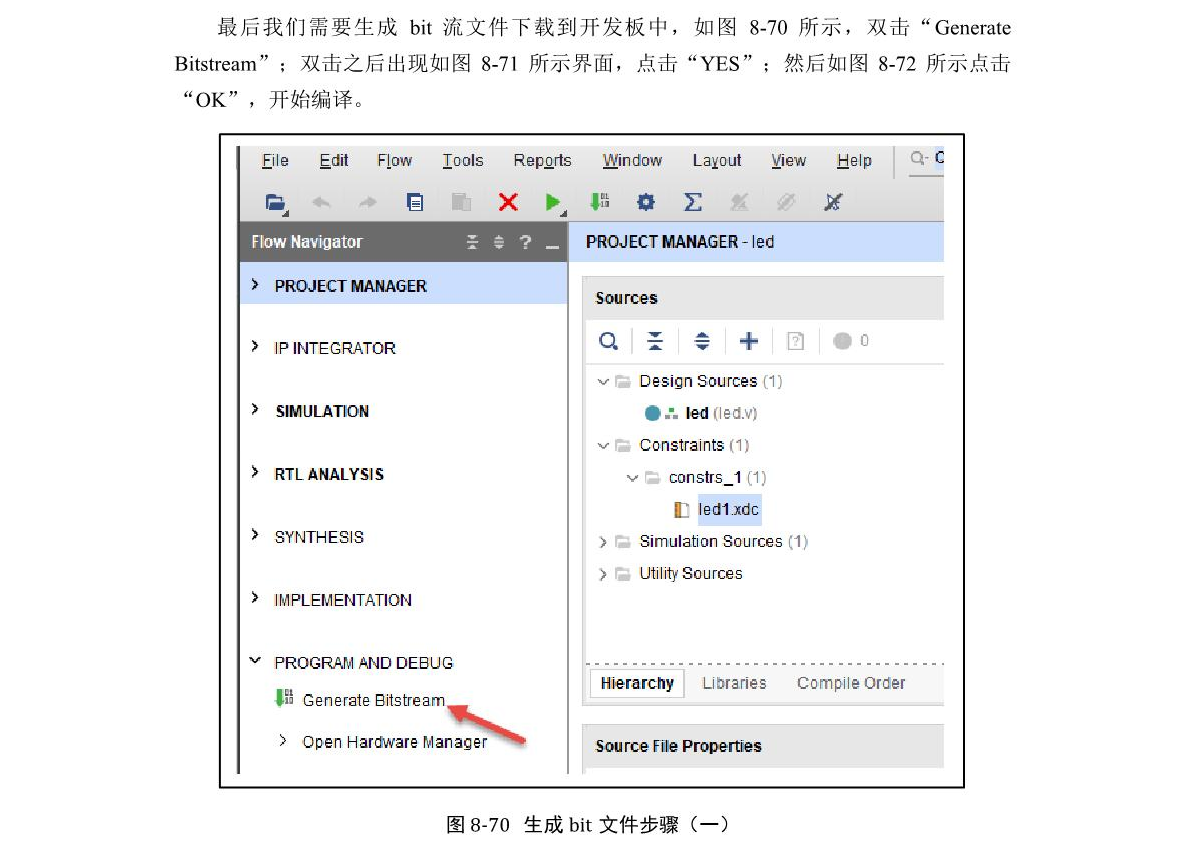

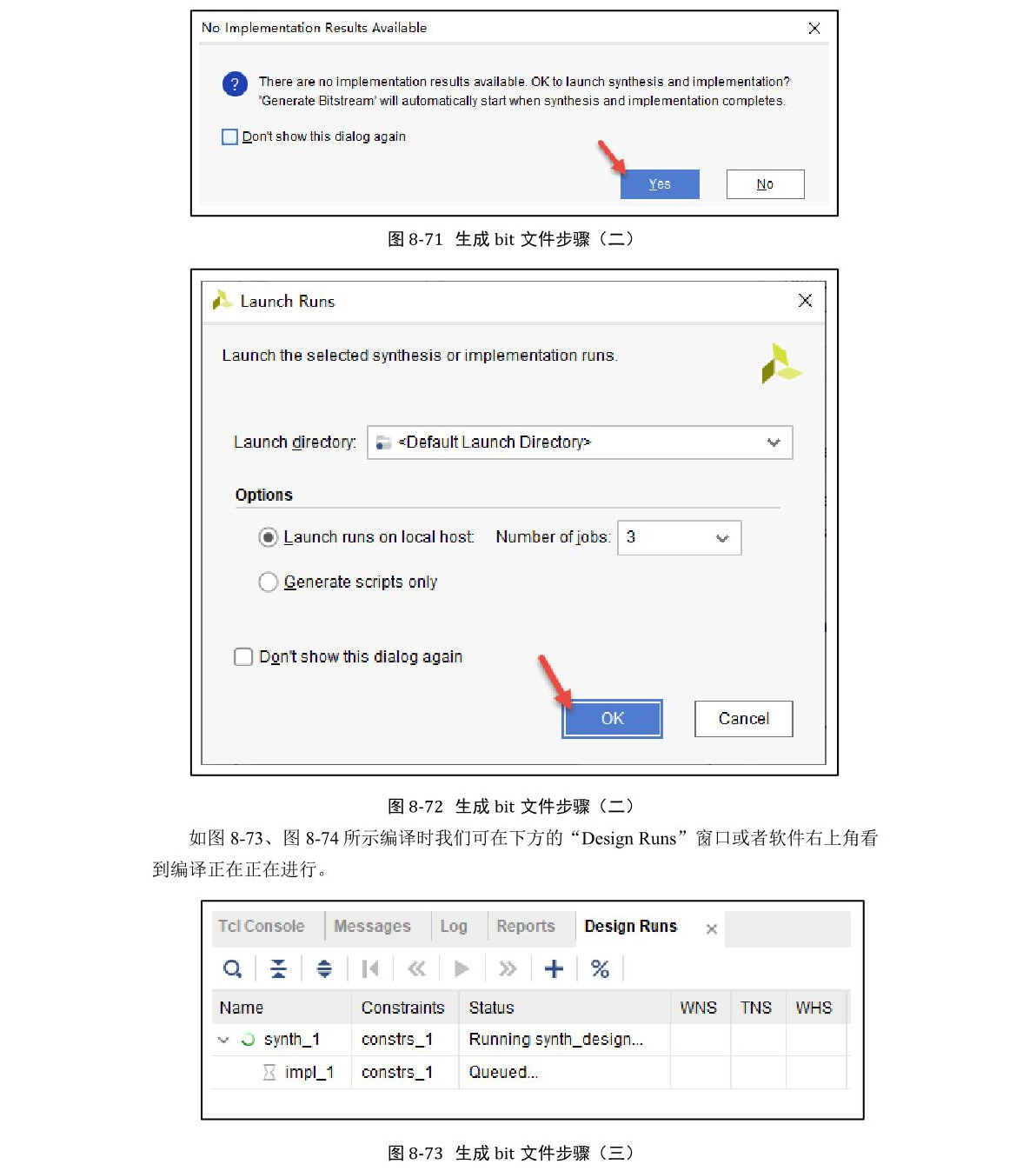

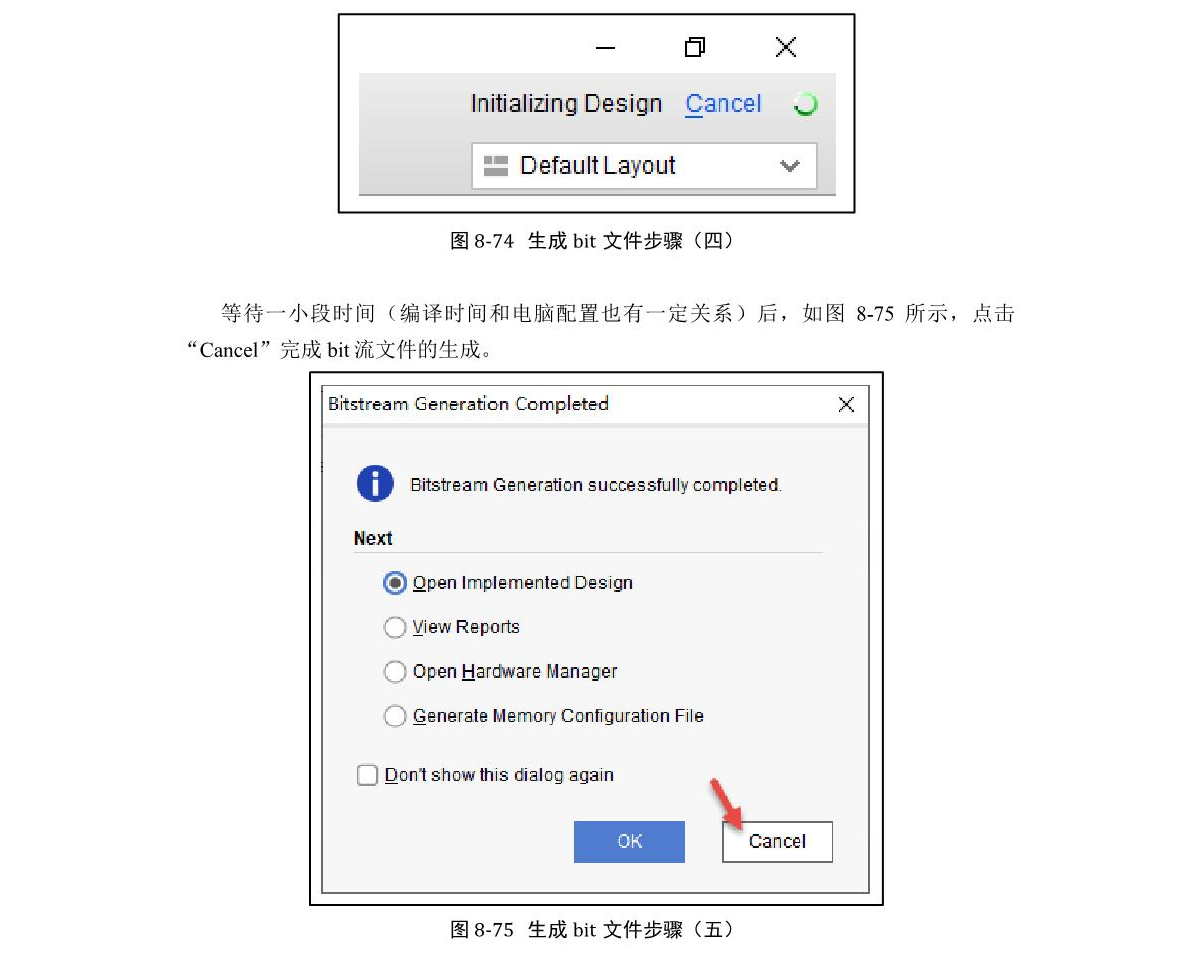

8.生成bit流文件

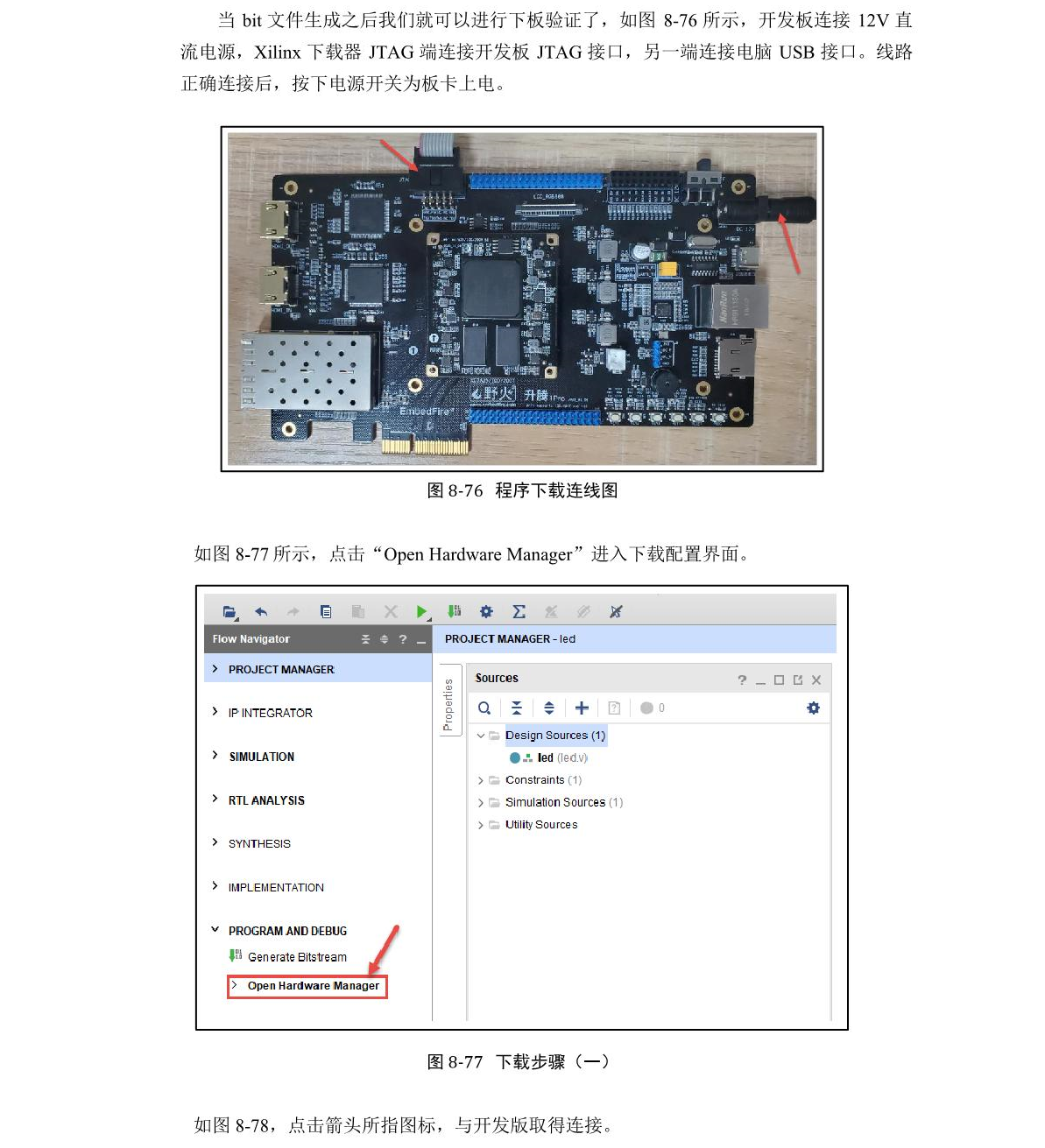

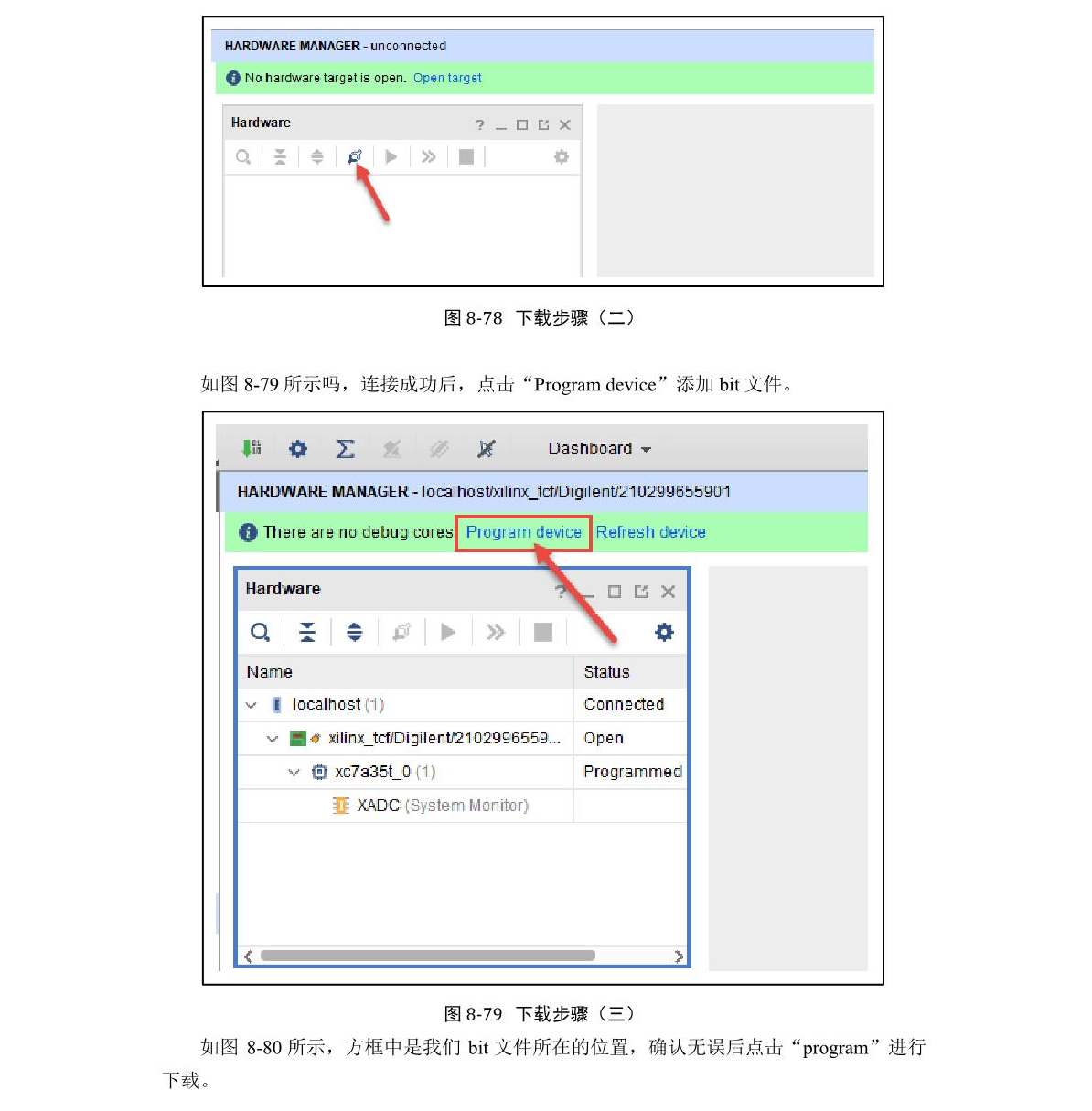

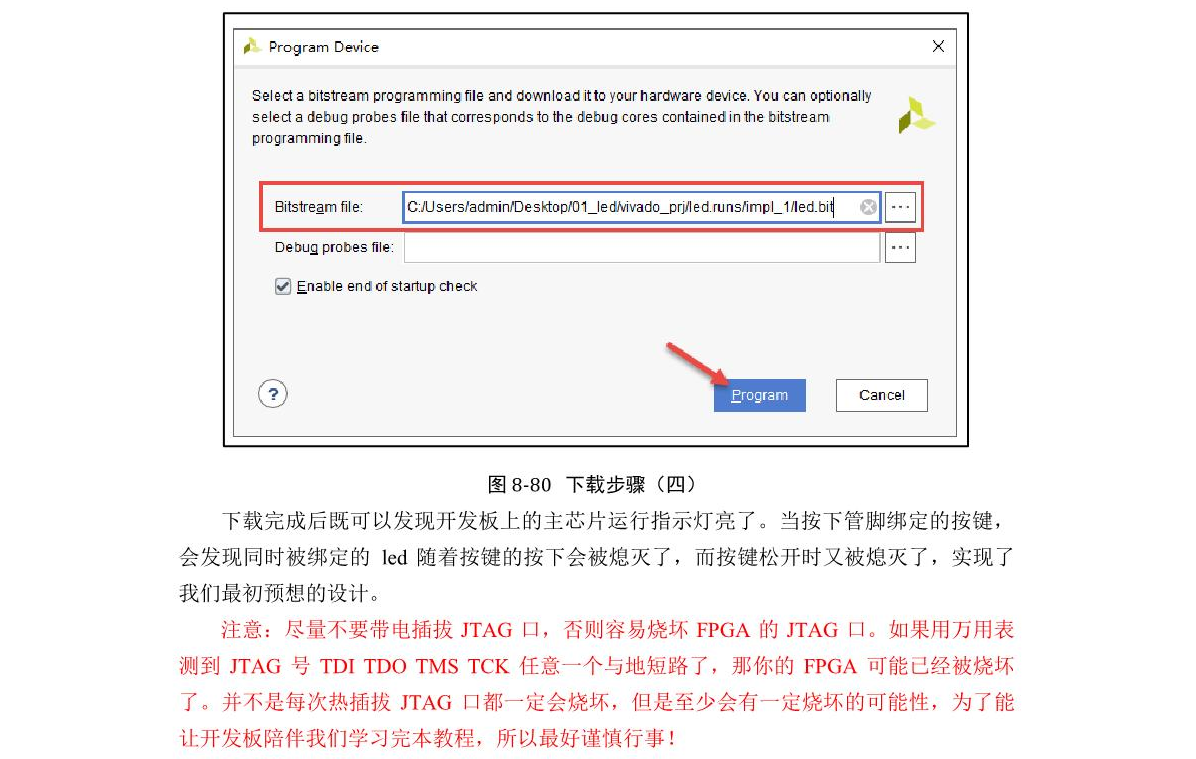

9.通过JTAG将网表下载到开发板

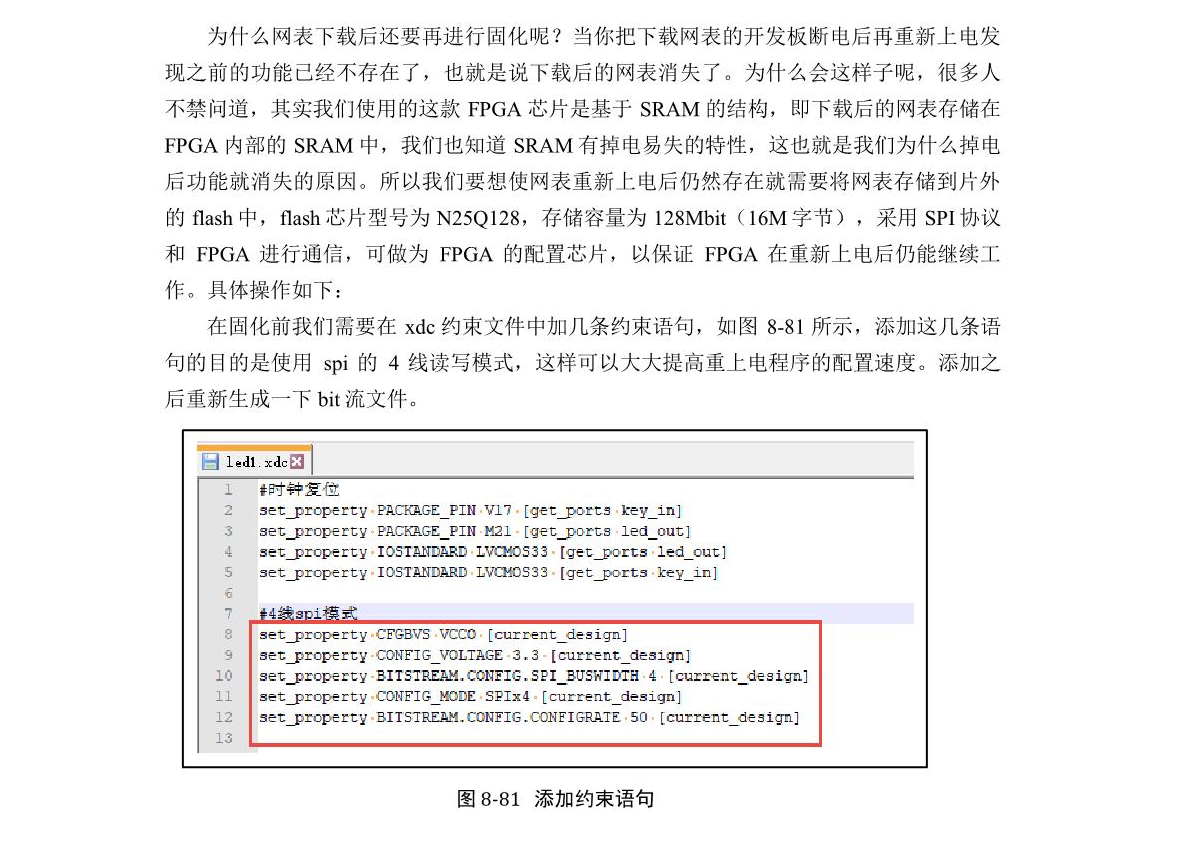

10.程序的固化

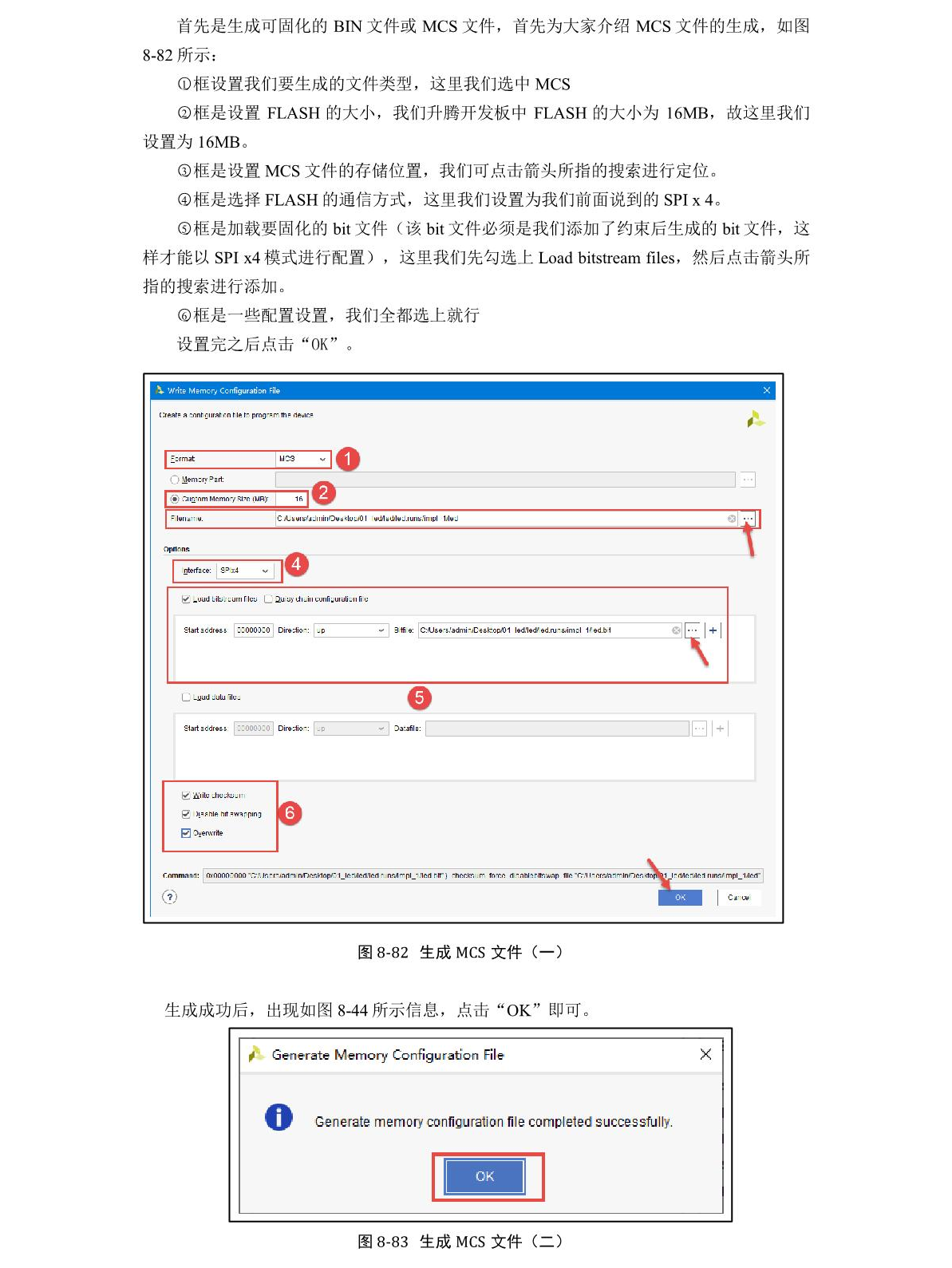

10.1 MCS文件的生成

10.2 BIN文件的生成

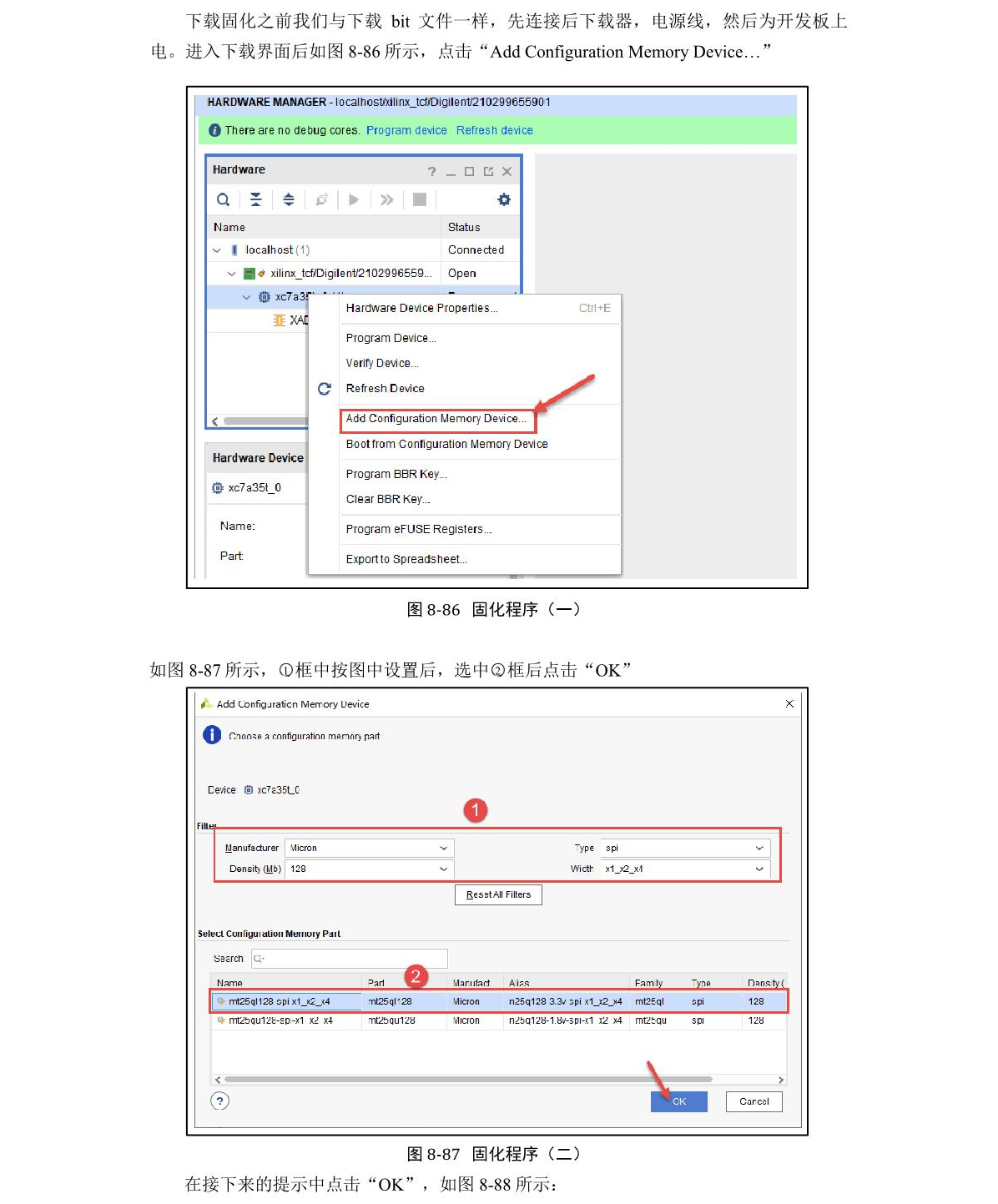

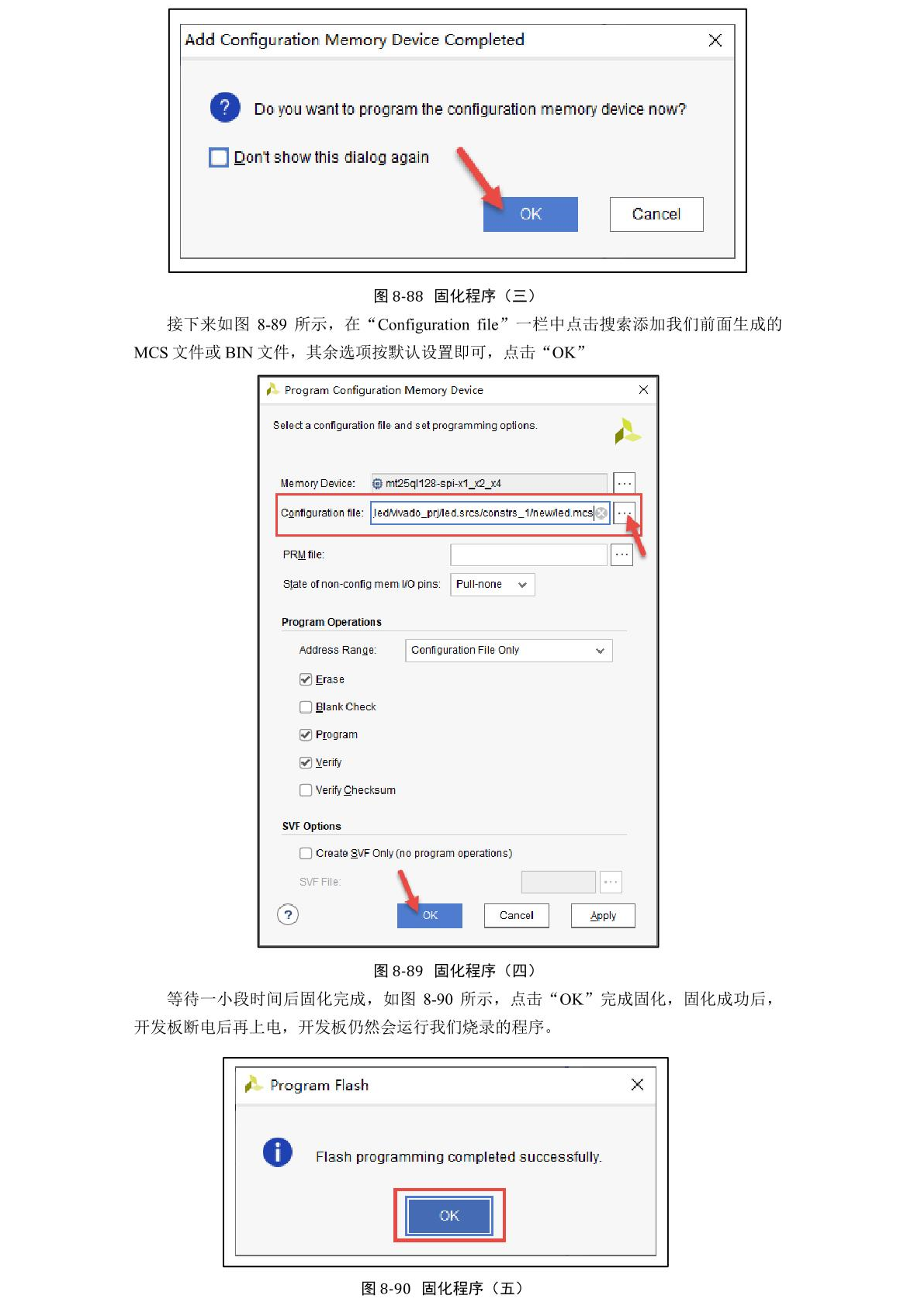

10.3 下载固化文件

参考文献

选自 野火《FPGA Verilog开发实战指南——基于Xilinx Artix7》

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/花生_TL007/article/detail/628609

推荐阅读

相关标签