热门标签

热门文章

- 1Android——APP启动流程&&Android开机流程_安卓app 启动 顺序

- 2微信小程序getUserProfile详解_wx.getuserprofile

- 3[UNet]通过一个小测试了解Command和ClientRpc的功能

- 4Git Manual / Git使用手册 / Git, GitLab, Git Bash, TortoiseGit (建议全文复制到Word文档中通过导航窗格查看)...

- 5王道考研购物网站(JSP+java+springmvc+mysql+MyBatis)

- 6WPF 登录窗口demo示例

- 7NumPy的实用函数整理之where_numpy where

- 8机器学习 决策树_头歌决策树案例

- 9Pandas透视表大揭秘:从基础到高级技巧的完整指南_pandas数据透视表函数

- 10五种常见的电子商务模式对比:B2B、B2C、C2B、C2C、O2O

当前位置: article > 正文

m基于FPGA和MATLAB的数字CIC滤波器设计和实现_cic算法

作者:花生_TL007 | 2024-06-10 11:58:16

赞

踩

cic算法

目录

1.算法概述

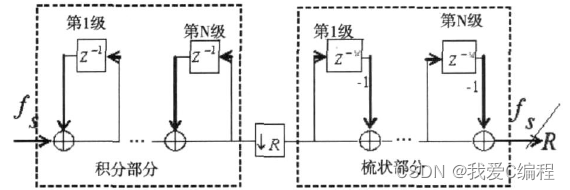

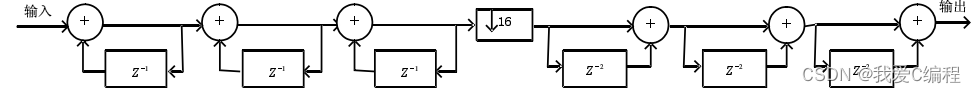

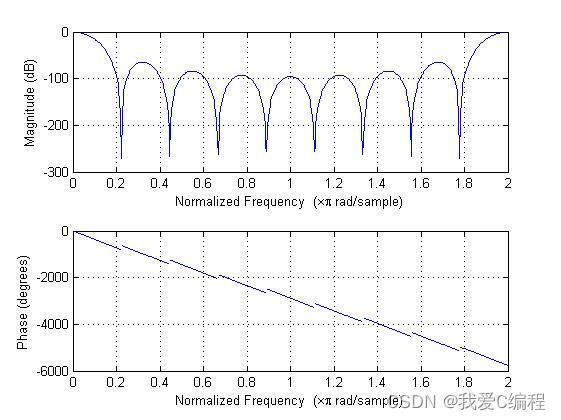

CIC滤波器由一对或多对积分-梳状滤波器组成,在抽取CIC中,输入信号依次经过积分,降采样,以及与积分环节数目相同的梳状滤波器。在内插CIC中,输入信号依次经过梳状滤波器,升采样,以及与梳状数目相同的积分环节。CIC滤波器是一种基于零极点相抵消的FIR滤波器。N级CIC抽取滤波器的基本结构框图如图1所示。

我们将这个系统模块话,然后在实际应用的时候,我们只要改变其中的参数就可以了。

系统分为如下三个模块。

模块一的设计:

delay_one(

i_clk,//输入时钟

i_rst,//输入复位信号

i_data,//输入信号

o_data//输出信号

);

模块二的设计:

down(

i_clk,//输入时钟

i_rst,//输入复位信号

i_M, //抽取值

i_data,//输入信号

o_data//输出信号

);

模块三的设计:

delay_M(

i_clk,//输入时钟

i_rst,//输入复位信号

i_data,//输入信号

o_data//输出信号

);

那么其在顶层,我们只要调用这些模块就行了。

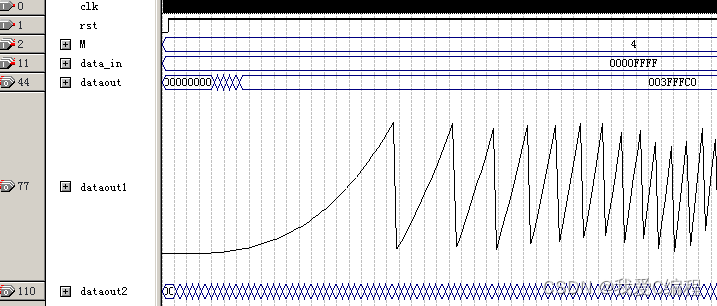

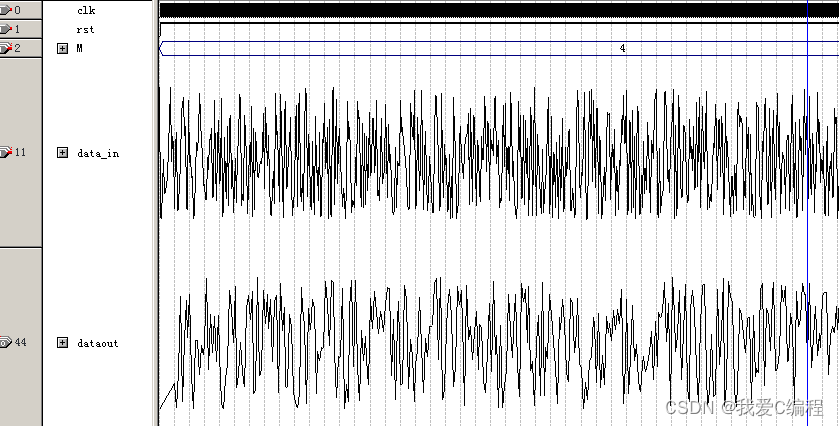

2.仿真效果预览

QUARTUS12.1

matlab2022a仿真

3.MATLAB/FPGA部分代码预览

- .......................................

- b4=conv(b3,b3);

- a4=conv(a3,a3);

- b5=conv(b4,b3);

- a5=conv(a4,a3);

- b6=conv(b4,b4);

- a6=conv(a4,a4);

- b7=conv(b6,b3);

- a7=conv(a6,a3);

- figure(1);

- freqz(b7/D^5,a7,'whole');

-

- %CIC抽取滤波器

- % 抽取因子

- r = 2;

- hm = mfilt.cicdecim(r);

- %原始的采样率 44.1kHz.

- fs = 44.1e3;

- %10240个采样点

- n = 0:10239;

- %原始信号

- x = sin(2*pi*1e3/fs*n);

- %得到抽取后的5120个采样点

- y_fi = filter(hm,x);

- x = double(x);

- y = double(y_fi);

- y = y/max(abs(y));

- figure(2);

- stem(n(1:44)/fs,x(2:45)); hold on;

- stem(n(1:22)/(fs/r),y(3:24),'r','filled');

- xlabel('时间(sec)');ylabel('信号值');

- title('CIC抽取滤波器');

-

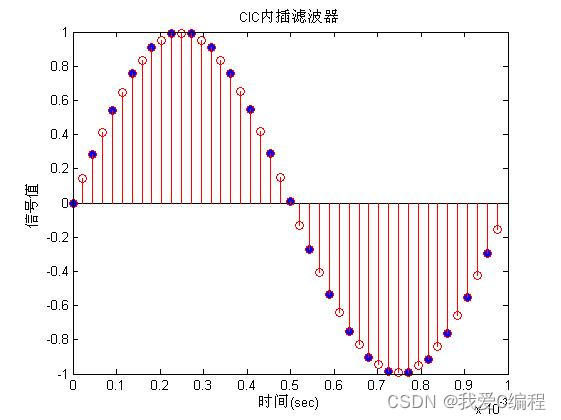

- %CIC内插滤波器

- %插值因子

- R = 2;

- hm = mfilt.cicinterp(R);

- % 原始采样频率:22.05 kHz.

- fs = 22.05e3;

- % 5120个采样点

- n = 0:5119;

- %原始信号

- x = sin(2*pi*1e3/fs*n);

- y_fi = filter(hm,x);

- x = double(x);

- y = double(y_fi);

- y = y/max(abs(y));

- figure(3);

- stem(n(1:22)/fs,x(1:22),'filled'); hold on;

- stem(n(1:44)/(fs*R),y(4:47),'r');

- xlabel('时间(sec)');ylabel('信号值');

- 01-23M

- module down(

- i_clk,//输入时钟

- i_rst,//输入复位信号

- i_M, //抽取值

- i_data,//输入信号

- o_data,//输出信号

- r_clk

- );

-

- input i_clk;//输入时钟

- input i_rst;//输入复位信号

- input [7:0] i_M; //抽取值

- input signed[31:0] i_data;//输入信号

- output signed[31:0]o_data;//输出信号

- output r_clk;//输出信号

- reg [7:0] r_cnt =8'd0;

- reg signed[31:0]o_data=32'd0;

- reg r_clk =1'b0;

- always @(posedge i_clk)

- begin

- if(!i_rst)//系统复位

- begin

- r_cnt<=8'd0;

- r_clk<=1'b0;

- end

- else begin

- if(r_cnt==i_M/2-1)//分频

- begin

- r_clk<=~r_clk;

- r_cnt<=8'd0;

- end

- else begin

- r_cnt<=r_cnt+1'b1;

- r_clk<=r_clk;

- end

- end

- end

- always @(posedge r_clk)

- begin

- if(!i_rst)//系统复位

- begin

- o_data<=32'd0;

- end

- else begin

- o_data<=i_data;//抽取

- end

- end

-

-

- endmodule

4.完整MATLAB/FPGA程序

V

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/花生_TL007/article/detail/698664

推荐阅读

相关标签