热门标签

热门文章

- 1 一步一步创建ASP.NET MVC5程序[Repository+Autofac+Automapper+SqlSugar](一)

- 2Qt初学者的一些学习方法、参考资料_qt要学数据结构吗

- 3OpenCV 人脸检测(易上手版)

- 4详解各种LLM系列|(2)LLaMA 2模型架构、 预训练、SFT、RLHF内容详解 PART-2_llm sft prompt predict fft

- 5OpenCV 直方图均衡化_opencv直方图均衡化函数

- 6sql server的具体安装教程_sql server安装博客教程

- 7【CVPR 2020】用于目标检测的统一样本加权网络

- 8Qt使用Qt Designer进行界面设计_qt 拖拽界面设计

- 9cassandra可视化工具_2020年十个最好用的大数据分析工具

- 10大一大二的计算机专业同学应该学习什么?如何学习?_计算机大二学生该干什么

当前位置: article > 正文

基于ZYNQ的PCIE高速数据采集卡的设计(一)

作者:菜鸟追梦旅行 | 2024-03-05 19:39:36

赞

踩

基于ZYNQ的PCIE高速数据采集卡的设计(一)

作为信息处理的第一步,数据采集的作用越来越重要。目前,数据采集已经在航

空、民用、军事、医疗等领域得到广泛应用。随着相关技术的不断发展,信号频率越

来高,带宽越来越大,使得数据采集技术逐渐向高速大数据的方向发展。在电子对抗

应用中,各种复杂宽带雷达体制的出现,使得电磁信号在空间中更为复杂。在复杂电

磁空间中识别出特定信号,首先需要高速

ADC

对电磁信号进行采样,然后经过高速

数据传输至处理器进行数据处理和分析,以便获取电磁信号里面的信息。通常由高速

数据采集卡完成电磁信号的采集和传输,而数据处理既可以由采集卡内高性能的处理

器完成,也可以将数据保存,由

PC

机后续完成。

目前处理器主要有

FPGA

、

ARM

、

DSP

、

PowerPC

等,并且大多数处理器提供高

速串行接口,以实现高速数据传输。高速串行接口是以多通道的差分对进行传输,与

传统并行总线相比,高速串行接口具有抗干扰能力强,速度高的特点,避免了并行总

线的串扰和同步问题

[1]

。

ARM

和

DSP

等处理器是基于

CPU

的架构的,每一时刻只能

执行一条命令。而

FPGA

是以数字电路为基础的芯片,各个模块之间的工作不会受影

响,因此

FPGA

的并行处理性能是

ARM

、

DSP

等处理器无法比拟的

[2]

,然而

FPGA

不适合用来数据处理,通常搭配

ARM

或

DSP

来进行数据处理。

通常采集卡通常使用

FPGA+ARM

或

FPGA+DSP

的处理架构,

FPGA

完成信号

的采集和传输,

ARM

或

DSP

用来对数据进行处理。由于这种架构使得处理器分离,

使这种结构的电路设计更为复杂,并且软件设计需要不同的开发平台,因此开发的周

期较长。本设计采用

Zynq7000

系列

SoC

为主控芯片,该芯片内部为

FPGA+ARM

的

架构,封装至一个芯片内

[3]

。电路设计简单,而且用一个平台就可以实现

FPGA

和

ARM

的功能,大大节省了开发时间。采集卡的接口通常采用以太网口或

PCIE

接口,

以太网口的传输速度较慢,不适合高速数据的传输。而

PCIE

接口可轻松实现几十

Gbps

的传输速率,在高速数据采集卡方面得到广泛应用。

本课题针对雷达辐射源的高速数据采集需求,设计并实现了一种

PCIE

高速数据

采集卡。使用

Zynq7000 SoC

芯片作为处理芯片,采用

PCIE2.0

协议完成采集卡与雷

达辐射源信号识别平台之间的数据交互,使用

DDR3 SDRAM

实现数据的缓存功能,

最终实现了最高

40Gbps

的数据传输速率。本设计为高速信号采集和传输提供了一种

设计思路和实现方法,具有一定的意义和参考价值。

1.2

国内外相关课题研究和发展现状

1.2.1

高速数据采集卡现状

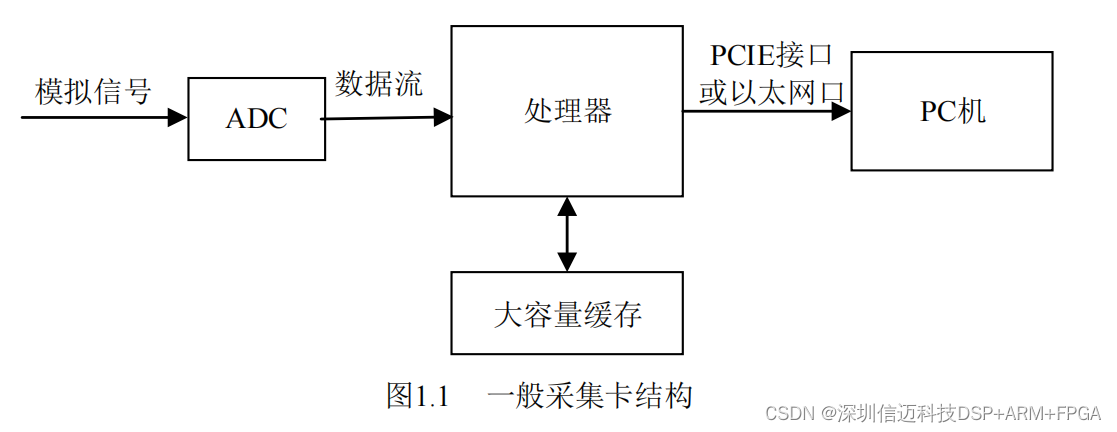

一般的高速数据采集卡采用如图

1.1

所示的结构,模拟信号经

ADC

采集后进入

处理器,数据经过缓存、处理后可以通过

PCIE

接口或者以太网口接入电脑。处理器

通常采用

FPGA+DSP

或者

FPGA+ARM

的架构。其中,

FPGA

用来完成数据采集工

作,

DSP

和

ARM

负责完成数据处理工作;大容量缓存一般采用

DDR2

芯片或者

DDR3

芯片,用来暂存数据。采样的数据也可直接由高速

PCIE

接口之间传输至

PC

机,供

下一步处理。高速数据采集依赖于高速

ADC

和高速总线的发展,下面详细说明一下

ADC

的发展现状和处理器的架构。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/193388

推荐阅读

相关标签