- 1Vue 3.0学习笔记之 组件注册_vue3注册组件

- 2AIGC笔记--关节点6D位姿按比例融合

- 3列表的两端对齐布局_两端对齐什么样子

- 4ai聊天机器人免费的哪个好?这篇文章会告诉你_ai回复机器人免费

- 5微信公众账号开发教程(一) 基本原理及微信公众账号注册 ——转自http://www.cnblogs.com/yank/p/3364827.html...

- 6OVER(PARTITION BY)开窗函数常见荤素搭配

- 72021人工智能状况分析报告

- 8Android studio 连接华为真机调试_android studio连接华为手机

- 9Linux sed命令实现替换文本内容_sed替换文件里的内容

- 10sql注入(总结)_sql echo

体系结构复习2——指令级并行(分支预测和VLIW)_rsvsrob

赞

踩

第五章内容较多,接体系结构复习1

5.4 基于硬件推测的指令级并行

动态分支预测是在程序运行时,根据转移的历史信息等动态确定预测分支方向,主要方法有:

- 基于BPB(Branch Prediction Buffer)和BHT(Branch History Table)的方法

- 高性能指令发送(High Performance Instruction Delivery)

5.4.1 基于BPB和BHT的方法

(1)1-bit BHT

分支指令PC的低位索引1位记录上一次转移是否成功(不是预测是否正确),不做地址检查

1-bit BHT有无法避免的问题,在一个循环中会造成至少两次预测错误:

- 最后一次循环,前面均循环成功,但这次需要跳出循环即需要预测失败

- 首次循环,前面最后一次循环失败,但这次需要预测成功

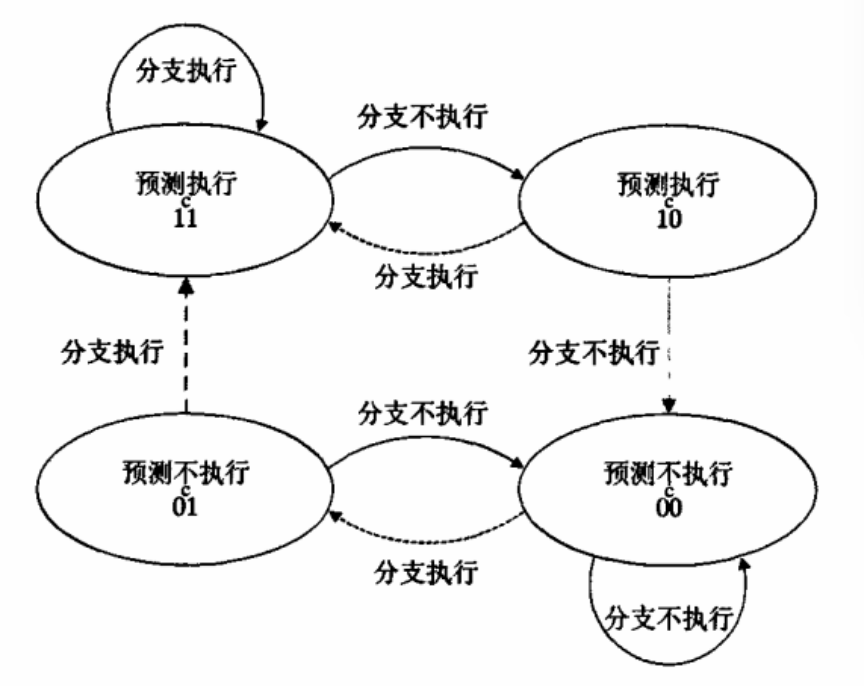

(2)2-bit BHT

用两位表示预测,设1表示分支成功、0表示分支失败,那么有如下状态转移表:

| 状态 | 当前失败 | 当前成功 | 预测 |

|---|---|---|---|

| 00 | 00 | 01 | 预测失败 |

| 01 | 10 | 11 | 预测失败 |

| 10 | 00 | 01 | 预测成功 |

| 11 | 10 | 11 | 预测成功 |

看FSM比较好理解一点:

把2位预测器想像成一个黑盒(只知道是基于两次历史分支记录),执行分支语句是查看该黑盒是“预测执行”还是“预测不执行”(即和当前分支情况无关的预测),然后根据当前分支执行与否修改状态

BHT性能分析:

- 会发生预测错误:只是用PC低位查找,可能会找错历史纪录

- 经分析当表项达到一定数量以后,通过增加表项提高准确率几乎没有效果

(3)相关分支预测器

相关分支预测把其他分支的历史行为也纳入考虑,相关分支预测能够捕捉到邻近的分支之间的相关性,又叫两级预测

两级预测器的一般表达形式为(m,n)预测器,其含义是根据全局最近的m个分支的行为,来从2^m个n位预测器中做出预测

m个分支的行为一共有2^m种情况,根据具体情况选择与最近m个分支的行为对应的预测器,该预测器记录的是n位局部分支历史(n和m完全独立)

5.4.2 动态调度预测——ROB Tomasulo

扩展Tomasulo支持预测,需要用旁路的思想去执行不能确定的指令,旁路执行只是执行指令并保存它的中间结果,但不更新任何寄存器或存储器

当一条指令不再具有不确定性时(也就是确定执行时),才更新寄存器或存储器的值,把这一操作叫做提交(Commit)

不确定指令的旁路执行的时刻可能快于其准备好提交的时刻,因此需要用一组硬件缓冲区来保存已经完成执行但还没有提交的指令结果,称之为重排缓冲区(Reorder Buffer,ROB),ROB保证指令循序提交

ROB有四个域:指令类型、执行状态、目的地址和值,ROB可以向RS一样作为操作数据源;当指令执行完毕后用ROB编号代替RS中的值

Tomasulo增加一个Commit阶段,由以下四阶段构成ROB Tomasulo:

| 阶段 | 内容 |

|---|---|

| Issue发射 | 如果对应RS空闲且ROB中有空插槽(无结构相关)则发射指令。如果寄存器或ROB中已经有操作数,则发送到保留站。为结果分配的ROB项目编号也发送给RS,以便标记CDB上广播的结果 |

| Execute执行 | 两操作数就绪后RS开始执行,若没准备好随时监听CDB以获取所需的操作数(避免RAW) |

| Write写结果 | CDB传送所有结果给等待结果的RS和ROB,并修改Register result status |

| Commit提交 | 按照ROB表中顺序,如果分支结果已出是分支成功,则处理器用ROB结果更新寄存器或存储器,并在ROB表中删除该指令;如果分支结果已出是分支失败,则刷新ROB表 |

注意:ROB Tomasulo在Register Status里记录的寄存器值也是ROB编号,除非Commit提交更新

5.6 多发射&静态调度的指令级并行

如果想要理想CPI<1,则需要允许在一个时钟周期内发射多条指令,多发射处理器主要有以下三类:

- VLIW超长指令字处理器:

- 静态调度超标量处理器

- 动态调度超标量处理器

Superscalar DLX允许一个周期内发送一条fp指令和一条其他指令,如果指令间整数操作和浮点操作易于区分组合(无任何相关)则可以达到理想CPI=0.5;但不是同时发射越多指令就越好,多发射给译码和发射带来不少困难

5.6.1 VLIW的循环展开

VLIW使用多个独立运算单元,书上假设有:1个整数/分支单元、2个浮点单元和2个存储器引用单元,但VLIW不是想单元发送多条独立指令,而是将多个操作包装在一条非常长的长指令中或发送包中;静态调度时可以不用在意VLIW实现方式,而是直接用多发射的思想来考虑

把上面的循环:

Loop: LD F0,0(R1)

ADDD F4,F0,F2

SD 0(R1),F4

DADDI R1,R1,#-8

BNEZ R1,Loop- 1

- 2

- 3

- 4

- 5

用VLIW做8段循环展开如下:

存储器引用1 存储器引用2 浮点运算1 浮点运算2 整数运算/分支

LD F0,0(R1) LD F6,-8(R1)

LD F10,-16(R1) LD F14,-24(R1)

LD F18,-32(R1) LD F22,-40(R1) ADDD F4,F0,F2 ADDD F8,F0,F2

LD F26,-48(R1) LD F30,-56(R1) ADDD F12,F0,F2 ADDD F16,F0,F2

ADDD F20,F0,F2 ADDD F24,F0,F2

SD 0(R1),F4 SD -8(R1),F8 ADDD F28,F0,F2 ADDD F32,F0,F2

SD -16(R1),F12 SD -24(R1),F16 DADDI R1,R1,#-64

SD 32(R1),F20 SD 24(R1),F24

SD 16(R1),F28 SD 8(R1),F32 BNEZ R1,Loop- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

(不好排版)9周期完成8段循环,一段循环只需要1.125周期!

5.7 多发射&动态调度的指令级并行

多发射动态调度略,基本思路是扩展Tomasulo让其有多个发射控制器(浮点和整数),最主要的思想是保证指令序的前提下,用队列检测的方法防止三种相关